VGA全稱是Video Graphics Array,即視頻圖形陣列,是一個使用模擬信號進行視頻傳輸的標準。分辨率高,顯示速度快。

一、傳輸協議

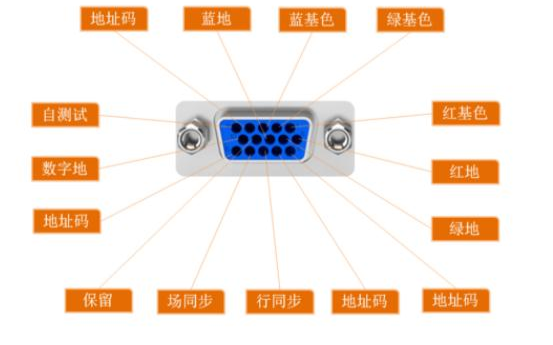

VGA接口15個引腳,除去地線,我們一般會用到5個引腳:1(RED)、2(GREEN)、3(BLUE)、13(HSYNC)、14(VSYNC)。

如圖1:

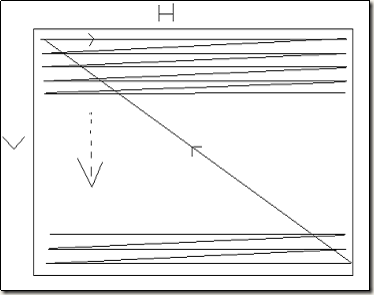

1、2、3指的是傳輸的紅、綠、藍三色的模擬信號,范圍為0-0.714V,0代表無色,0.714V代表滿色,需要注意的這是模擬信號,因此前面還需要進行一個數模轉換。HSYNC(行同步信號)和VSYNC(場同步信號)分別是指傳輸一行和傳輸一幀的時序,下面看一下他們的時序圖:

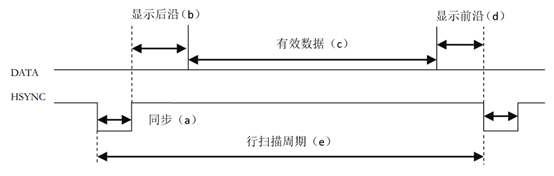

a:行同步時期,掃描地址的復位

b:行消隱后肩,掃描地址轉移后的穩定等待準備期

c:行顯示時期,數據有效區域

d:行消隱前肩,掃描地址轉移的準備

e:行掃描總時間,一行掃描的總時間

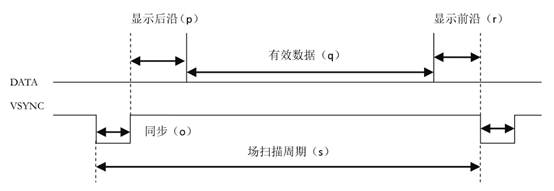

o:場同步時期,掃描地址的復位

p:場消隱后肩,掃描地址轉移后的穩定等待準備期

q:場顯示時期,數據有效區域

r:場消隱前肩,掃描地址轉移的準備

s:場掃描總時間,一場掃描的總時間

可以看出,行同步時序和場同步時序類似,分別經歷4個階段:拉低、顯示后沿、有效數據傳輸和顯示前言。

FPGA硬件測試時要將sys_pll中的輸出頻率改為25MHZ。

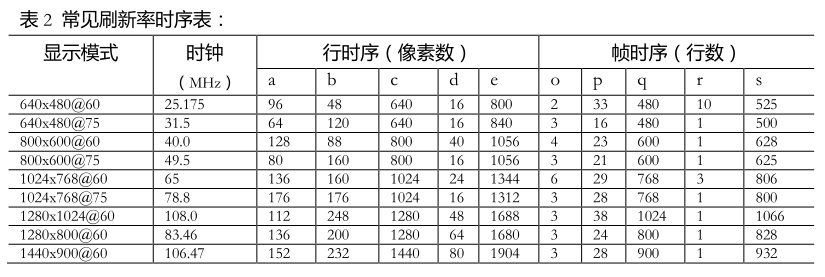

目前液晶顯示器普及,而高于 60Hz 的刷新率對于液晶來說,沒有任何意義,所以我們以 640*480 在 60Hz 的刷新率下為例。

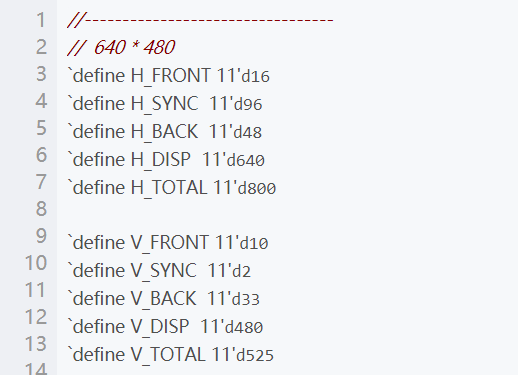

1)為便于移植,根據640*480 60hz分辨率下的參數,宏定義相關數據。

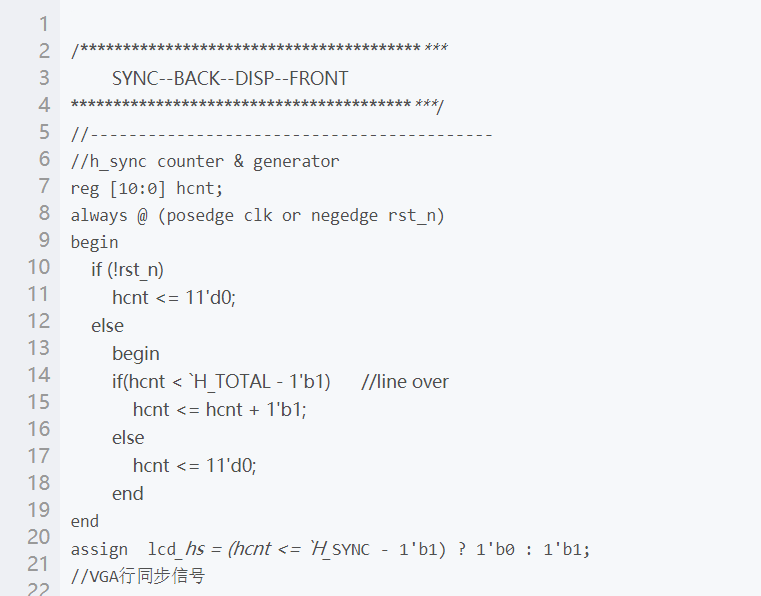

2)行掃描單位hcnt計數

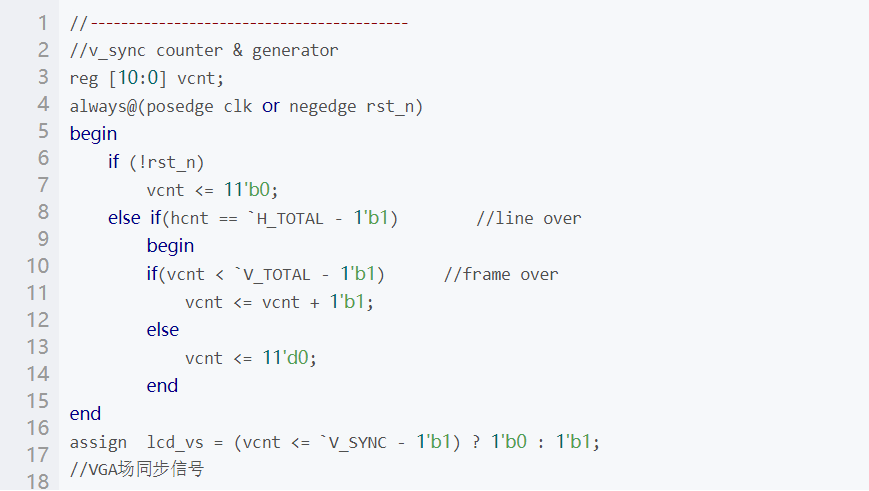

3)列掃描單位vcnt計數

每掃描完一行,即hcnt完成H_TOTAL次計數后,vcnt進行自加。

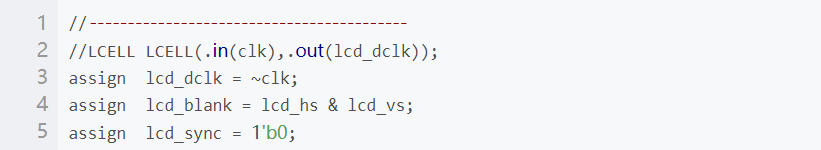

4)ADV7123控制信號輸出

為了實現數據在lcd_dclk上升沿有效,我們將clk翻轉輸出,已實現上升沿采樣 。

lcd_blank作為顯示空白信號,低電平有效。

設計中不需要lcd_sync信息,可以直接接地。

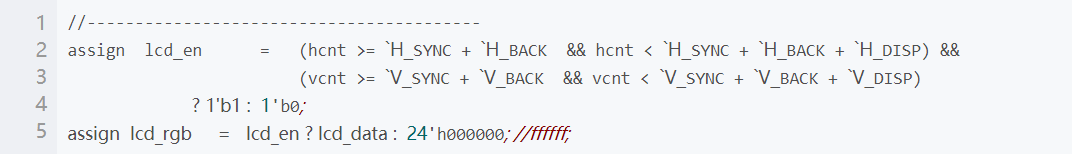

5)有效顯示使能信號輸出

當使能信號有效時,接收外部輸入的RGB數據lcd_data.

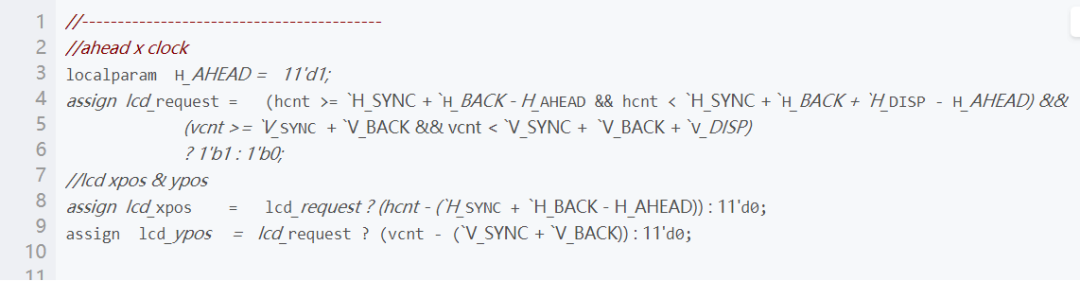

6)外部數據請求控制信號

為了保證數據穩定,lcd_request要提前一個時鐘請求外部輸入數據 。

同時,設計中實時顯示下一時刻的掃描地址lcd_xpos、lcd_ypos,也要提前一個時鐘輸出,以保證外部數據輸入的同步化。

lcd_xpos、lcd_ypos是顯示器有效顯示區域的行列坐標計數值。

四、模擬VGA圖像數據的輸入

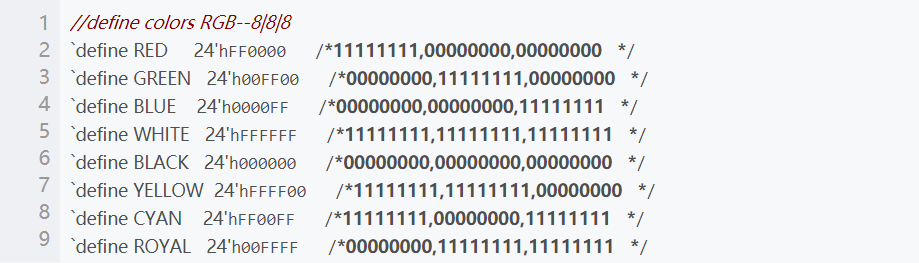

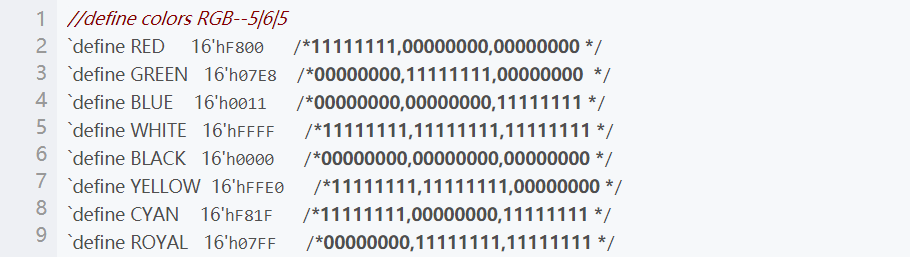

1)宏定義三原色組合的顏色如下

這里要注意所用的VGA驅動電路是RGB888還是RGB565,如果是RGB565,三原色要改成下面樣式,并把其他程序中lcd_data的位數改為16位:

筆者曾在這里犯過錯誤。

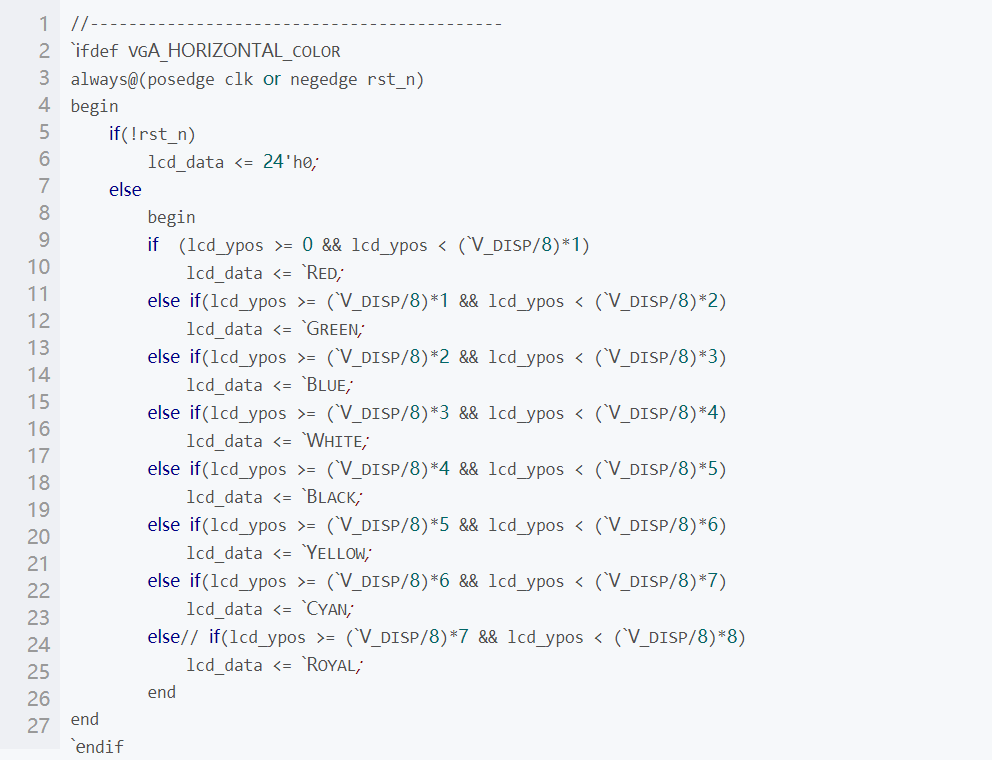

2)根據輸入的行、列地址信號,輸出三原色組合后得到的8條彩色。

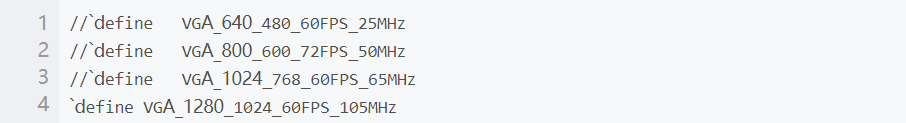

五、不同分辨率的VGA驅動

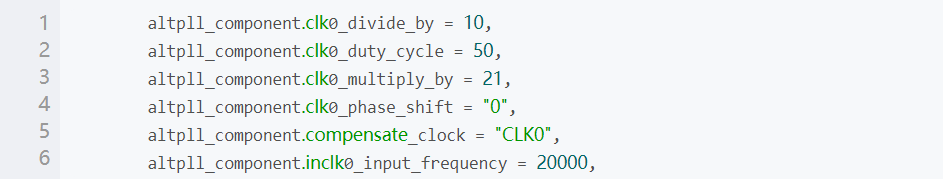

lcd_para文件定義了四種VGA分辨率驅動,這里只需修改定義的注釋就行,并把PLL鎖相環中的頻率改為相應的頻率。

PLL修改方法為直接修改下面參數中的乘法除法因子:

編輯:hfy

-

FPGA

+關注

關注

1626文章

21669瀏覽量

601872 -

Verilog

+關注

關注

28文章

1344瀏覽量

109986 -

模擬信號

+關注

關注

8文章

1118瀏覽量

52404 -

驅動電路

+關注

關注

152文章

1520瀏覽量

108380 -

VGA

+關注

關注

5文章

533瀏覽量

62831

發布評論請先 登錄

相關推薦

勇敢的芯伴你玩轉Altera FPGA連載20:VGA顯示接口電路

Verilog編寫的基于SPARTAN板的VGA接口顯示程序

在FPGA_CPLD中實現AD或DA的文章(英文Verilog)

基于叁芯智能科技的SANXIN -B01 FPGA開發板的VGA協議驅動設計

FPGA設計中DAC控制的Verilog實現

FPGA設計中DAC控制的Verilog實現修訂稿

ADC0809驅動FPGA實現的verilog程序

基于FPGA的Verilog實現VGA驅動電路

基于FPGA的Verilog實現VGA驅動電路

評論