在ZYNQ進(jìn)階之路3中我們講解了PL端UART 發(fā)送的設(shè)計(jì),本節(jié)我們講解PL端實(shí)現(xiàn)串口UART的接收設(shè)計(jì);

下面主要是uart接收模塊的編碼講述,uart接收模塊設(shè)計(jì)主要分為波特率控制計(jì)數(shù)邏輯和按位接收邏輯,其具體編碼如下所示:

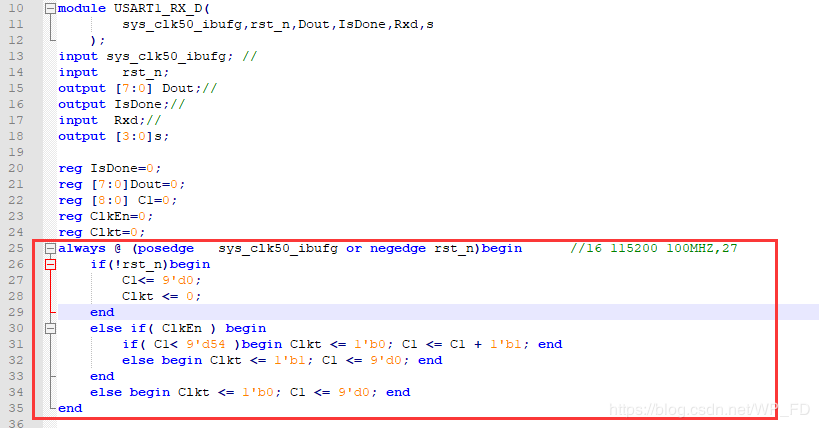

波特率控制計(jì)數(shù)邏輯:

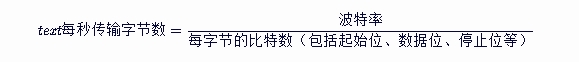

其中325是根據(jù)主時(shí)鐘頻率為100Mhz,這里設(shè)置波特率為115200,所以計(jì)數(shù)值=100000000/115200/16=54;需要注意的是在串口接收中需要將一個(gè)波特率周期分成16份然后再一個(gè)波特率周期的第8份是進(jìn)行采樣,所以需要進(jìn)行16分頻;

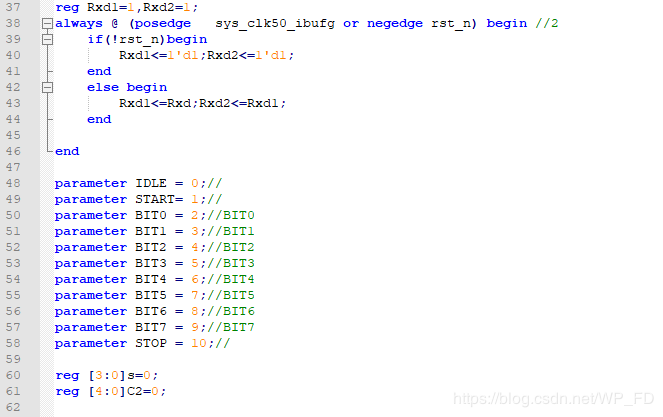

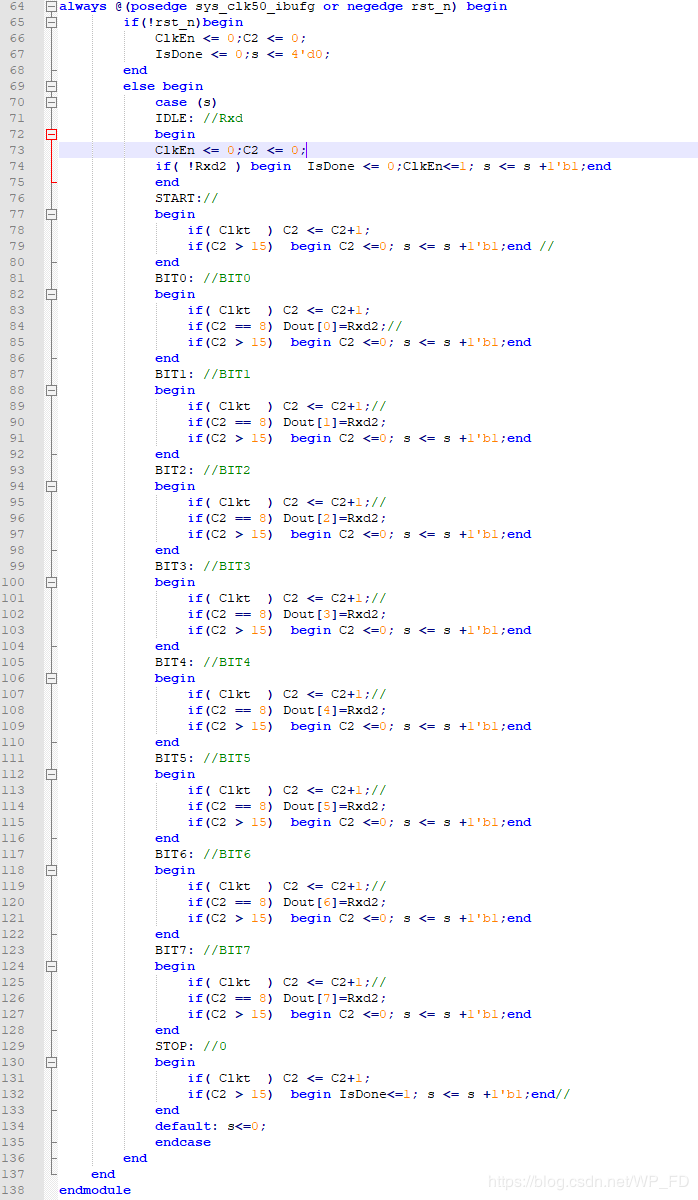

按位接收邏輯:

通過檢測IsDone上升沿到來來檢測串口數(shù)據(jù)接收是否完成。讀者可自行將上一節(jié)中的串口發(fā)送模塊和本節(jié)的接收模塊組合成一個(gè)工程,實(shí)現(xiàn)通過USB轉(zhuǎn)串口電路模塊實(shí)現(xiàn)PC端發(fā)送數(shù)據(jù)相應(yīng)返回同樣的數(shù)據(jù)給PC,實(shí)現(xiàn)回環(huán)測試功能。

編輯:hfy

-

uart

+關(guān)注

關(guān)注

22文章

1227瀏覽量

101177 -

波特率

+關(guān)注

關(guān)注

2文章

303瀏覽量

34068 -

Zynq

+關(guān)注

關(guān)注

9文章

608瀏覽量

47128

發(fā)布評論請先 登錄

相關(guān)推薦

uart波特率和傳輸頻率的關(guān)系 UART串口的常用波特率為多少

復(fù)旦微PS+PL異構(gòu)多核開發(fā)案例分享,基于FMQL20SM國產(chǎn)處理器平臺

FM20S用戶手冊-PS + PL異構(gòu)多核案例開發(fā)手冊

如何將ESP32端AT串口接收改為DMA方式?

請問如何實(shí)現(xiàn)ESP32 uart的接收空閑中斷?

簡談Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

HAL_UART_Receive_IT,HAL_UART_Transmit不能正常接收數(shù)據(jù)的原因?

UART串口通信協(xié)議是什么?

請問FX3的UART口和Xilinx ZYNQ7000的PS端的UART進(jìn)行硬件連接需要TTL電平轉(zhuǎn)換嗎?

labview串口接收數(shù)據(jù)怎么不丟幀

什么是串口(UART)?串口的組成和FPGA實(shí)現(xiàn)

ZYNQ進(jìn)階:PL端實(shí)現(xiàn)串口UART的接收設(shè)計(jì)

ZYNQ進(jìn)階:PL端實(shí)現(xiàn)串口UART的接收設(shè)計(jì)

評論