在ZYNQ進階之路2中我們講解了PL端PWM呼吸燈的設計,本節我們講解PL端實現串口UART的發送設計;

首先新建一個串口發送的工程,工程建立在ZYNQ進階之路1中已經講述,這里不再累述;

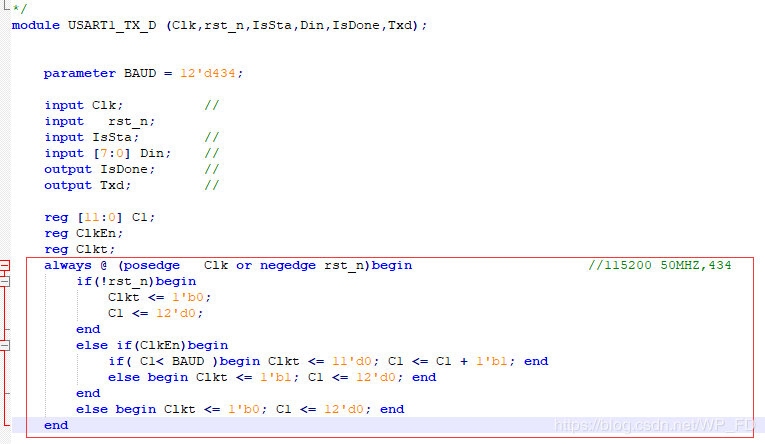

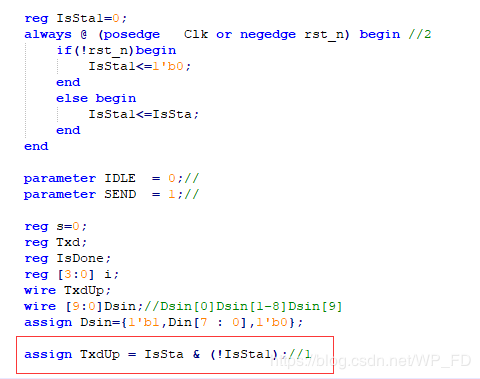

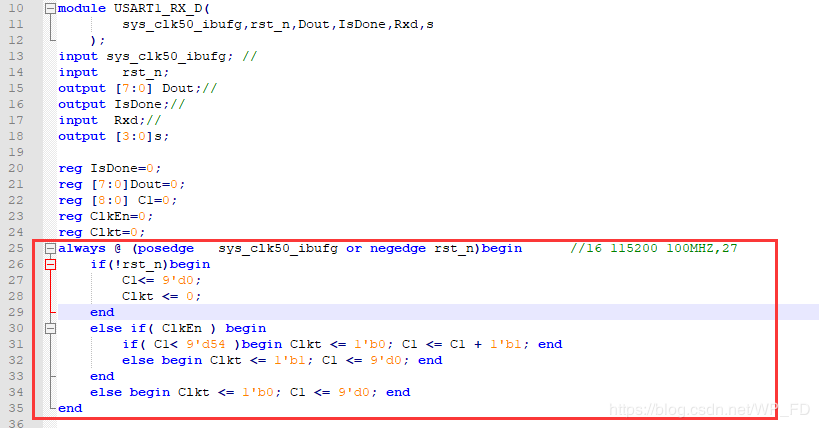

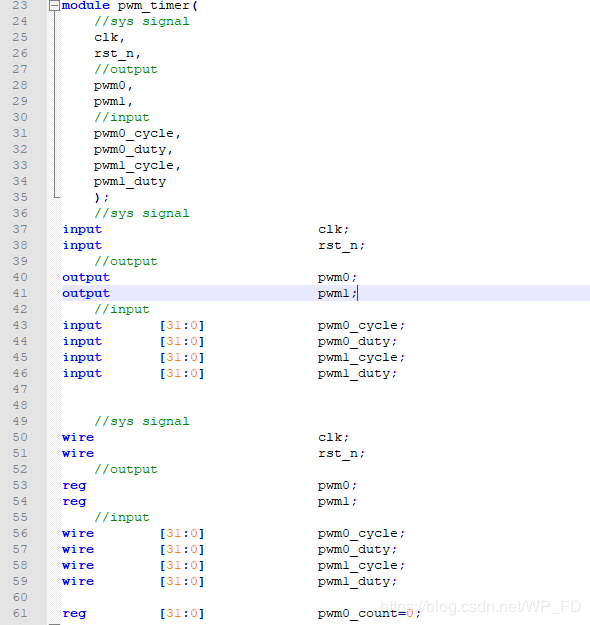

下面主要是uart發送模塊的編碼講述,uart發送模塊設計主要分為波特率控制計數邏輯和按位發送邏輯,其具體編碼如下所示:

波特率控制計數邏輯:

其中BAUD = 434是根據主時鐘頻率為50Mhz,這里我們去波特率為115200,所以計數值BAUD = 50000000/115200 =434;

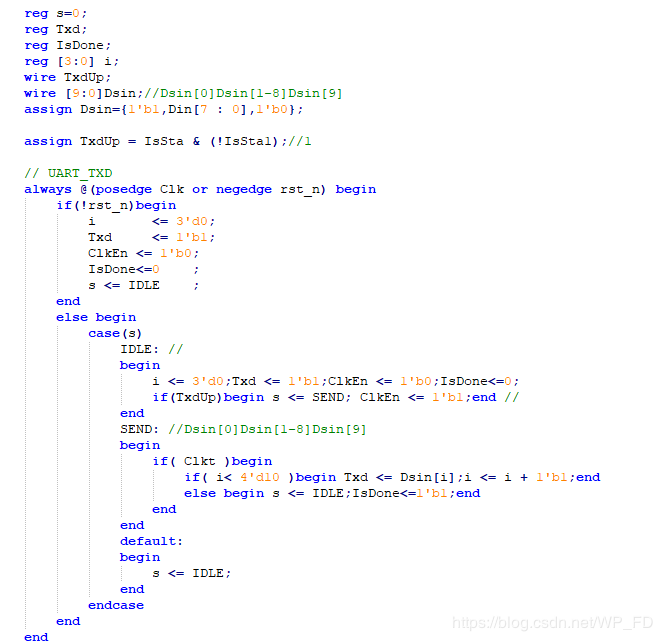

按位發送邏輯如下所示:

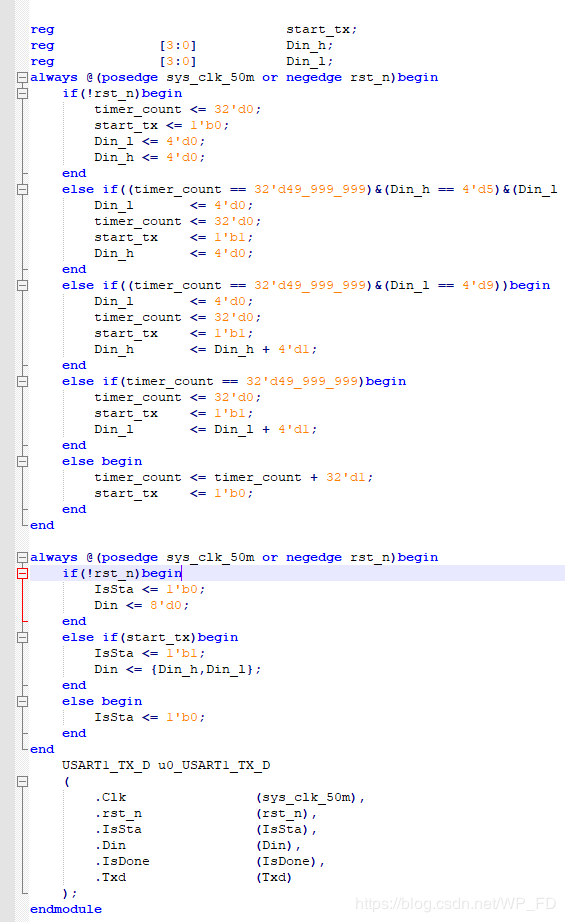

然后我們需要一個頂層文件,讓串口按照每秒鐘發送一個秒計時數據出去(BCD碼),器邏輯代碼如下所示:

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

uart

+關注

關注

22文章

1199瀏覽量

100834 -

波特率

+關注

關注

2文章

290瀏覽量

33928 -

Zynq

+關注

關注

9文章

604瀏覽量

47016

發布評論請先 登錄

相關推薦

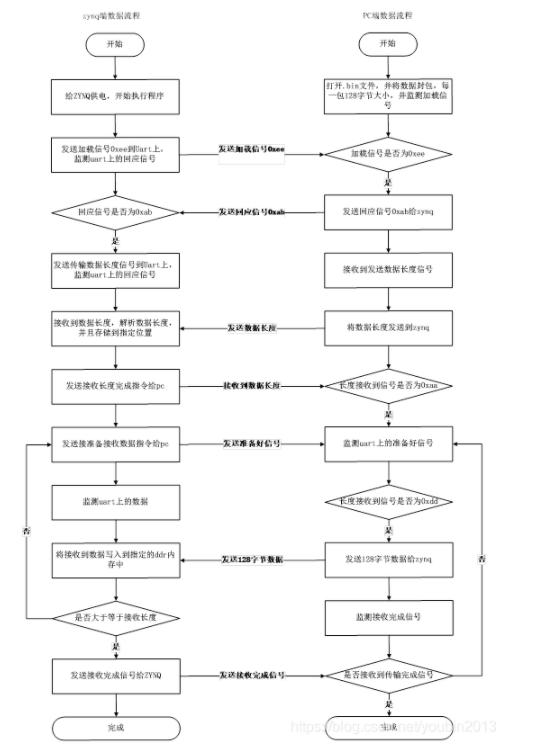

ZYNQ開發案例之ZYNQ的UART加載

,最終將這個文件寫入到QSPIFLASH中,整個ZYNQ在配置好啟動方式為FLASH啟動后,便可做到上電自啟動運行下載到FLASH中的用戶程序。 為了實現遠程加載,拋開仿真器,通過UART的方式將固定的.bin文件發送給

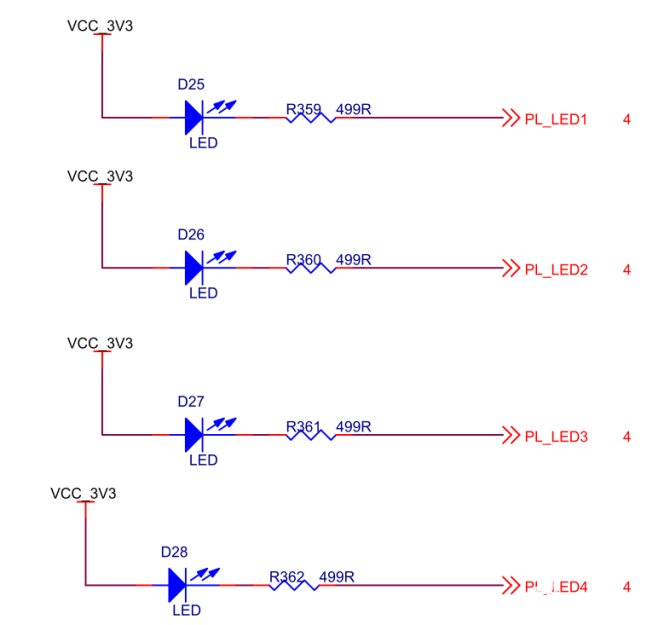

【ZYNQ Ultrascale+ MPSOC FPGA教程】第四章PL的LED實驗

對于ZYNQ來說PL(FPGA)開發是至關重要的,這也是ZYNQ比其他ARM的有優勢的地方,可以定制化很多ARM端的外設,在定制ARM端的外

【ZYNQ Ultrascale+ MPSOC FPGA教程】第二十九章PL端AXI GPIO的使用

使用zynq最大的疑問就是如何把PS和PL結合起來使用,在其他的SOC芯片中一般都會有GPIO,本實驗使用一個AXI GPIO的IP核,讓PS端通過AXI總線控制PL

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三十二章PL讀寫PS端DDR數據

PL和PS的高效交互是zynq soc開發的重中之重,我們常常需要將PL端的大量數據實時送到PS端處理,或者將PS

怎么在Petyninux 2014.4上使用Zynq上的PL UART?

你好我在Zynq 7010設計上添加了一個UART 16550 IP,中斷直接連接到Zynq INTC。在petalinux中導入硬件設計后,pl.dtsi結構似乎沒問題,但是當我編譯

發表于 04-08 07:50

zynq 7020 PS和zynq PL是如何通話的?

嗨,我必須找出zynq 7020 PS和zynq PL如何通話,特別是我必須找到將在ARM中處理的SDK C代碼。你能用一個明確的C代碼告訴我,它解釋了數據如何從PS轉移到PL,這是A

發表于 05-08 09:37

請問zynq 怎么實現PS與PL數據交互,然后通過UART串口打印出來?

請問zynq 怎么實現PS與PL數據交互,然后通過UART串口打印出來?前輩們做過的指導我一下。

發表于 08-03 15:53

使用Zynq PL結構時鐘驅動代碼沒有反應是為什么?

錯誤。然后,我在SDK中編程PS端,led閃爍正確的頻率!我的問題,當鎖定Zynq PL時鐘? PS程序之后?需要多長時間?是不是意味著,PL配置期間LED閃爍錯誤,在非易失性Flas

發表于 08-27 15:09

PS端實現FreeRTOS嵌入式系統

ZYNQ進階之路9--PS端實現FreeRTOS嵌入式系統導論FreeRTOS簡介實現步驟導論在之前的章節中我們我們完成了PS端、PL

發表于 12-22 08:29

AD9681是否可被zynq-7020的pl端驅動?

您好:

我想咨詢AD9681是否可以被zynq-7020的PL端驅動(zynq7020的性能是否足夠)。我們需要做衛星的探測載荷,由于衛星能源控制嚴格,我們需要低功耗、多通道(至少8個

發表于 12-04 08:18

關于Zynq-7000 PL端HDMI的顯示控制的性能分析和應用介紹

Zynq-7000 PL端HDMI的顯示控制 Zynq-7000 PS到PL端emio的使用 V

發表于 09-15 14:57

?3560次閱讀

ZYNQ進階:PL端UART 發送設計案例

ZYNQ進階:PL端UART 發送設計案例

評論