在高速的同步電路設計中,時序決定了一切,要求所有時序路徑都必須在約束限制的時鐘周期內,這成為設計人員最大的難題,因此,首先確定和分析基本時序路徑有助于設計者快速,準確地計算時序裕量,使系統穩定工作,XILINX公司提倡的幾種常用基本路徑。

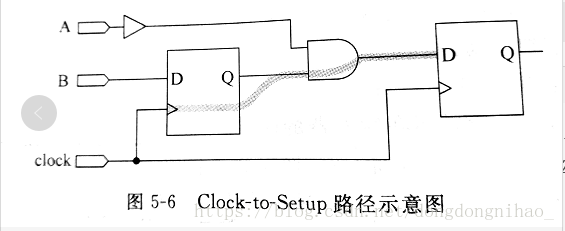

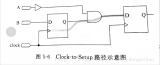

(1)Clock-to-Setup路徑:

clock-to-setup路徑從觸發器的輸入端開始,結束于下一級觸發器,鎖存器或者RAM的輸入端,對終止端的數據信號要求一定的建立時間。

如下圖所示:

該條路徑包括了觸發器內部clock-to-Q的延遲,觸發器之間的由組合邏輯造成的路徑延遲以及目標觸發器的建立時間,其延時是數據從源觸發器開始,在下一個時鐘沿來到之前通過組合邏輯和布線的最大時間,Clock-to-Setup時間可通過約束文件中的周期約束來限制。

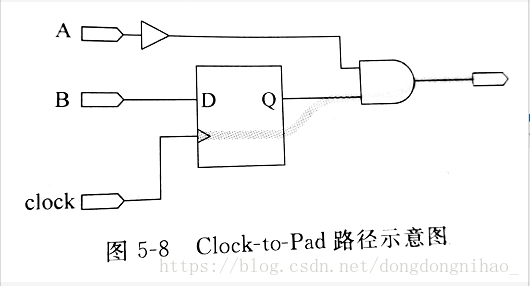

(2)Clock-to-pad路徑:

Clock-to-Pad路徑從寄存器或者鎖存器的時鐘輸入端開始,終止于芯片的輸出引腳,中間經過了觸發器輸出端以及所有的組合邏輯,如下圖所示:

這條路徑包括了經過觸發器的延時和從觸發器到輸出引腳之間的邏輯延遲,在約束文件中,可以通過OFFSET語句和FROM:TO來約束,如果使用OFFSET語句,那么時延計算時會包含時鐘輸入BUFFER/ROUTING延時;如果使用FROM:TO約束,則延時從觸發器自身開始,不包括輸入路徑,比較精確,所以使用相對更頻繁一些。

① OFFSET語句:OFFSET說明了外部時鐘和與其相關的輸入,輸出數據引腳之間的時序關系。其語法規則如下:

OFFSET={IN/OUT}"offset_time"[unit] {BEFORE/AFTER} "clk_name"[TIMEGRP"group_name"];

OFFSET可以用于設置多類約束,對于Clock-to-Pad需要將屬性配置為OUT AFTER, 例如:

NET Q_out OFFSET = OUT 35.0 AFTER "CLK_SYS"

② FROM :TO 語句 :FROM:TO定義了兩組信號之間時序關系。

其語法規則如下:

#TIMESPEC "TSname" = FROM "group1"TO "group2" value;

其中,TSname 必須以TS開頭,group1是起始路徑,group2是目的路徑,value值的默認單位為ns,也可以使用MHZ。

實例:

TIMESPEC TS_aa = FROM FFS TO PAD 10;

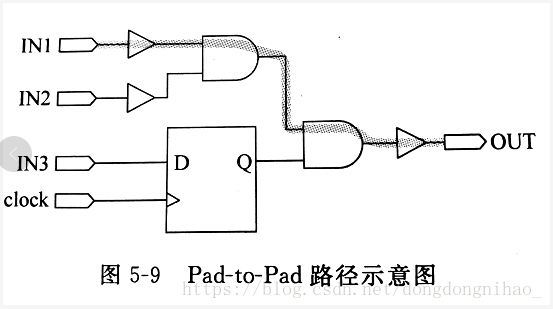

(3)Pad-to-Pad路徑:

Pad-to-Pad路徑從芯片輸入信號端口開始,結束于芯片輸出信號端口,中間包含所有組合邏輯,但并不包含任何同步邏輯如圖所示:

Pad-to-Pad路徑延時是數據輸入到芯片,經過邏輯延時和布線時延后再輸出芯片的最大時間要求,在約束文件中任然通過FROM:TO來約束,其語法如下:

TIMESPEC TS_aa = FROM PADS TO PADS 10 ;

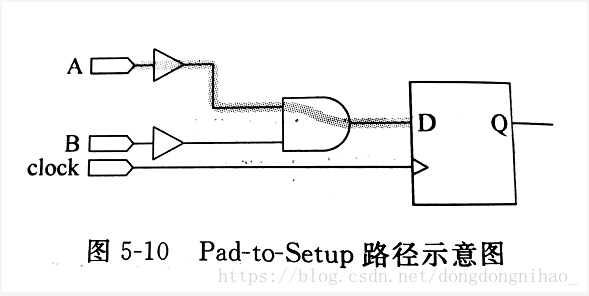

(4)Pad-to-Setup路徑

Pad-to-setup路徑從芯片的輸入信號端口開始,結束于同步電路模塊(觸發器,鎖存器和RAM),對相應的數據信號要求一定的建立時間,如下圖所示:

該路徑可以通過BUFFER和所有組合邏輯,不包含任何同步電路木塊和雙向端口,是數據到達芯片的最大時間要求,和Clock-to-Pad一樣,該路徑可以通過OFFSET和FROM:TO來設計,其中OFFSET語句的屬性設置為OFFSET IN BEFORE。

例如:

OFFSET = IN 10 ns BEFORE my_clk TIMEGRP My_FFS;

編輯:hfy

-

FPGA

+關注

關注

1626文章

21671瀏覽量

601886 -

RAM

+關注

關注

8文章

1367瀏覽量

114533 -

鎖存器

+關注

關注

8文章

904瀏覽量

41447 -

觸發器

+關注

關注

14文章

1996瀏覽量

61053 -

時序路徑

+關注

關注

0文章

12瀏覽量

1394

發布評論請先 登錄

相關推薦

高速ADC與FPGA的LVDS數據接口中避免時序誤差的設計考慮

時序邏輯電路故障分析

FPGA 高級設計:時序分析和收斂

Xilinx FPGA編程技巧之常用時序約束詳解

FPGA工程的時序約束實踐案例

Xilinx FPGA編程技巧之常用時序約束詳解

“AI+工業互聯網”賦能新型工業化的路徑分析

FPGA設計的常用基本時序路徑分析

FPGA設計的常用基本時序路徑分析

FPGA設計的常用基本時序路徑分析

評論