今天,我們聊聊雙核通信。雙核通信的基礎(chǔ)是已經(jīng)建立好了雙核工程,且配置完成。兩個CPU之間傳遞數(shù)據(jù),采用了共享內(nèi)存,共享內(nèi)存設(shè)置在OCM(On Chip Memory)內(nèi)。

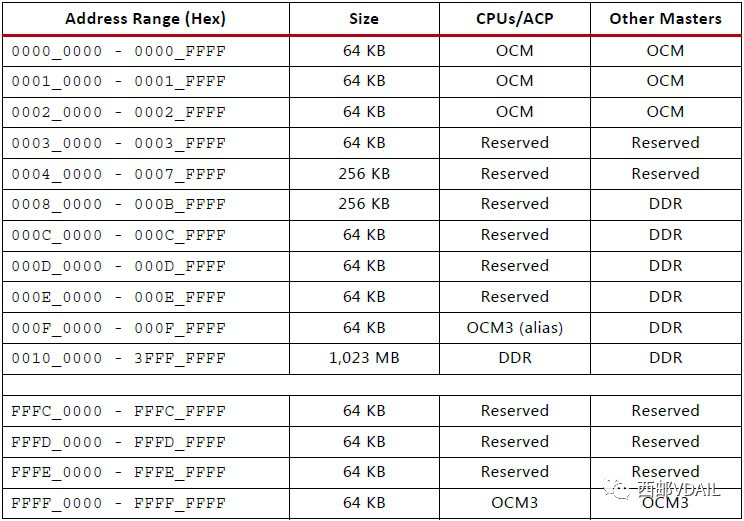

在沒有做其他設(shè)置的情況下,ZYNQ上電后地址空間分別如下圖所示:

OCM共256KB按照64KB分為4塊,其中前三塊在SDK中表述為RAM0占192KB處于地址空間的最開頭和DDR共用地址空間,最后一塊64KB處于地址空間的最后。ZYNQ的DDR固定占地址空間的最開頭1GB字節(jié)因而ZYNQ的DDR最大容量就只有1GB。

為了避開OCM從上圖可知實際使用的DDR只有1023MB(最開頭的1MB被保留避開OCM的前三塊)。從0x40000000到0xDFFFFFFF的2GB空間留給了自定義IP或者其他IP的寄存器,從BSP的xparameters.h可以看出在PL部分添加的IP其基址都是從0x40000000開始的,而ZYNQ自己的寄存器則從0xE0000000開始編制,具體寄存器內(nèi)容請查閱UG585的附錄B Register Details。

其實Standalone作為基礎(chǔ)的BSP所作的工作都是在通過指針訪問各個寄存器而已,在不考慮安全性的前提下可以完全不用BSP直接操作寄存器對ZYNQ進行操作。

需要在SDK中進行雙核通信的設(shè)置,主要是程序的設(shè)置。

1、CPU1需要被CPU0啟動

CPU0的配置

設(shè)置共享內(nèi)存區(qū)域:

#define Send_CPU1_Status (*(volatile unsigned int *)(0xFFFF0000))

在主函數(shù)中添加:

Xil_SetTlbAttributes(0xFFFF0000,0x14de2);// CPU0中禁止OCM的Cache屬性

2、CPU1通信配置

CPU1的配置

設(shè)置共享內(nèi)存區(qū)域:

#define Send_CPU1_Status (*(volatile unsigned int *)(0xFFFF0000))

在主函數(shù)中添加:

Xil_SetTlbAttributes(0xFFFF0000,0x14de2);// CPU0中禁止OCM的Cache屬性

3. 設(shè)置完成

雙核之間通過對該內(nèi)存區(qū)域進行讀寫操作完成通信功能。

編輯:hfy

-

cpu

+關(guān)注

關(guān)注

68文章

10825瀏覽量

211146 -

Zynq

+關(guān)注

關(guān)注

9文章

608瀏覽量

47126

發(fā)布評論請先 登錄

相關(guān)推薦

AMD/Xilinx Zynq? UltraScale+ ? MPSoC ZCU102 評估套件

全志T113雙核異構(gòu)處理器的使用基于Tina Linux5.0——異構(gòu)雙核通信驗證

雙核dsp和單核dsp的區(qū)別

正點原子ZYNQ7015開發(fā)板!ZYNQ 7000系列、雙核ARM、PCIe2.0、SFPX2,性能強悍,資料豐富!

TI基于Concerto雙核MCU的PRIME電力線通信數(shù)據(jù)集中器方案應(yīng)用說明

ZYNQ學(xué)習(xí)要點:雙核通信

ZYNQ學(xué)習(xí)要點:雙核通信

評論