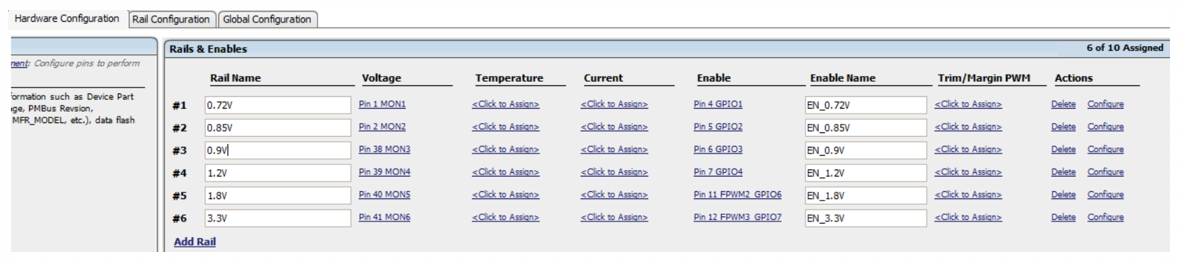

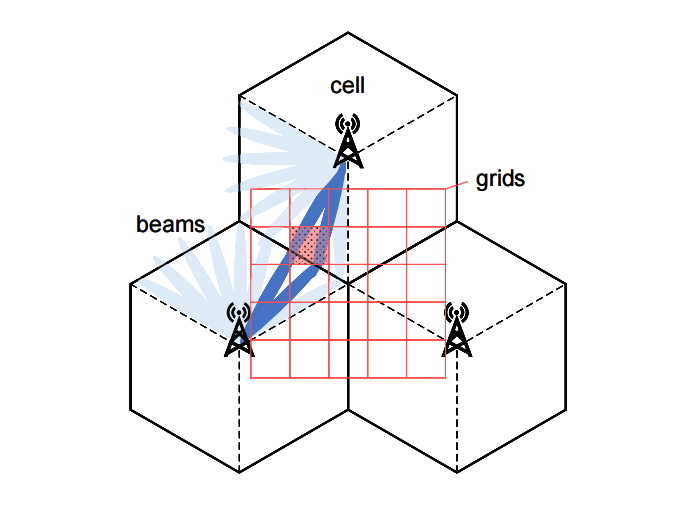

5G是目前通信設備領域的市場趨勢, Massive MIMO指的是64T64R應用中常用的多輸入和多輸出, 更多的發送器和接收器通道需要更多的數字處理器(FPGA / ASIC)來執行數據傳輸,而典型的64T64R MIMO應用中通常需要4-5個數字處理器。 每個FPGA都需要自己的電源上電/下電的時序,以便FPGA能夠正常工作。 在下面的圖1中,是典型的64T64R Massive MIMO框圖,4顆 ASIC / FPGA用于與4顆 RF采樣模擬前端(AFE7799)進行通信和控制。

圖 1: Massive MIMO 框圖

TI UCD90xx系列包括多個軌道選擇,從10個通道到32個通道,溫度范圍支持高達125C,非常適合用于通信設備領域,特別是在5G Massive MIMO應用中。

UCD90xx系列是一款數字電源時序器,無需寫軟件,并使用TI Fusion Digital Power Designer GUI配置時序。 硬件工程師更容易通過GUI設計電源時序列器而無需寫代碼。 此外,TI還提供培訓視頻,指導工程師如何將Fusion Digital Power Designer與UCD90x排序器配合使用,以便工程師可以快速掌握使用TI Fusion數字電源設計器的知識。

UCD90xx系列以非常小的解決方案尺寸集成了全功率監控,電源時序和故障記錄,可幫助服務器和通信設備客戶實現一體化芯片解決方案,同時具有設計靈活性和提高系統可靠性的優勢。

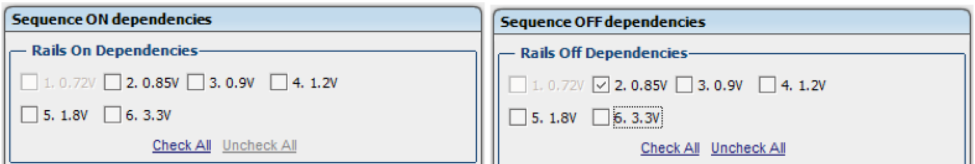

如何設計以UCD9090A給Xilinx Zynq Ultrascale FPGA系列的電源軌供電時序控制

1)了解上電/掉電時序要求

上電時序:0.72V - > 0.85V - > 0.9V - > 1.2V - > 1.8V - > 3.3V

掉電時序:3.3V - > 1.8V - > 1.2V - > 0.9V - > 0.85V - > 0.72V

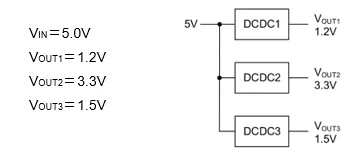

2)定義電源軌和使能名稱

圖 2: 電源軌和使能

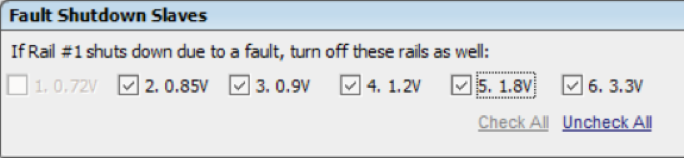

3)設計故障關閉,對每個電源軌的上電和掉電時序的依賴關系和故障響應進行時序。在電源軌配置(電源軌#1,0.72V)時序故障時的操作選項中,點擊其他電源軌,這意味著如果電源軌0.72V由于故障而關閉,則關閉這些點擊的電源軌。

圖 3: 發生故障時的操作

點擊0.85V掉電時序依賴關系,這意味著電源軌 0.72V斷電時序依賴于0.85V的Power Good的電壓低于正常水平就會觸發0.72V掉電時序。

圖 4: 上電/掉電時序的依賴性

在故障響應選項中,將響應更改為“立即關閉”和重啟為“不重啟”,這意味著當故障發生時,它將立即關閉軌道并且不會重新啟動該特定軌道。 這個基于設計要求來定義,如果需要重啟可以改為“連續重啟”。

圖 5: 故障響應

4)檢查電源軌和時序圖

圖 6: 電源軌

圖7: 上電和掉電時序

TI UCD90xx系列是服務器和通信設備應用中的最佳解決方案,它將監控,時序和故障記錄集成到一個芯片方案中。 TI Fusion數字電源設計器GUI可幫助硬件工程師節省寫軟件的工作并縮短設計周期。

編輯:hfy

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602047 -

服務器

+關注

關注

12文章

9029瀏覽量

85209 -

數字處理器

+關注

關注

0文章

18瀏覽量

10339 -

5G

+關注

關注

1353文章

48380瀏覽量

563463

發布評論請先 登錄

相關推薦

5G室外基站控制器專用晶振SG2016CAN編碼X1G004801003100

5G 外置天線

通過TI電源時序控制器在5G MIMO應用的通信和控制

通過TI電源時序控制器在5G MIMO應用的通信和控制

評論