實驗室回來一批板子,上面有RGMII接口、SGMII接口等各種接口,怎么測試這些網口是否正常呢?的確需要一些經驗。比如RGMII接口,最重要的是看在哪里去做的時鐘和數據偏移。這時,常常需要使用VIO去讀取PHY里面對應寄存器的值,看是否工作在正常RGMII接口時序模式。

測試場景

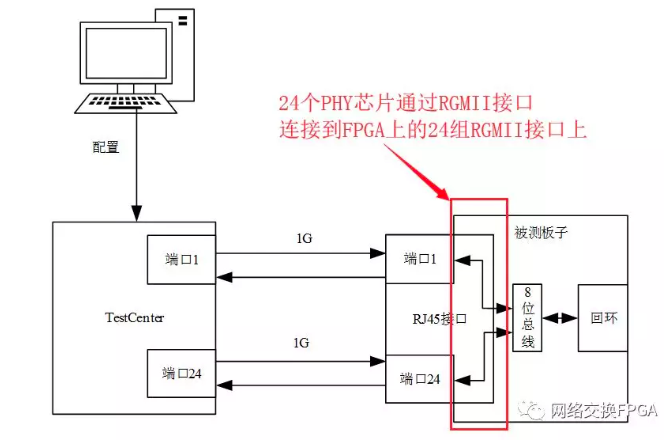

測試拓撲圖如下

試場景連接圖

測試方法:使用TestCenter向被測板子上的千兆以太網口打流,在FPGA內部通過自回環從源端口返回給TestCenter,通過看TestCenter控制界面上顯示結果判斷自回環是否正確。

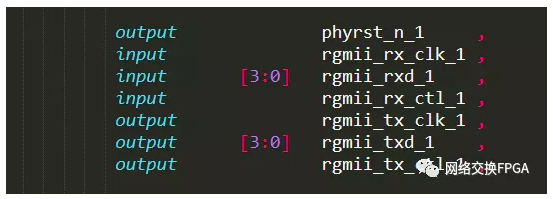

測試RGMII接口時使用的PHY芯片為MARVELL 公司的88e1512PHY芯片,RGMII頂層接口信號如圖1所示。

圖1 測試代碼頂層接口信號

采用以往經驗發現問題

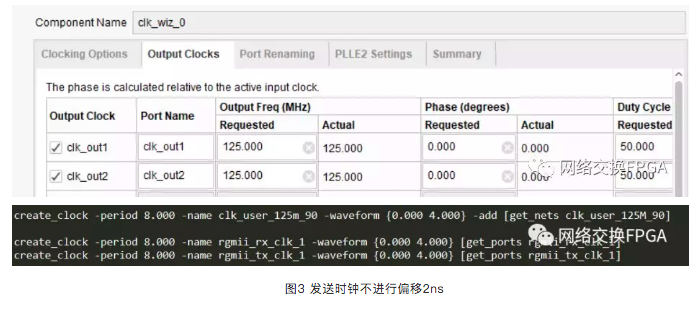

按照以往的RGMII接口使用經驗,通過約束將接口的輸出時鐘延遲了2ns,如圖2所示。使用TestCenter對以太網口進行測試,以太網口無法正常發送數據。具體表現為,TestCenter接收的數據幀數目,和發送的數據幀數目相等,但是接收的bit數明顯比發送的bit數少。抓取測試代碼的內部信號發現,FPGA接收到的以太網數據幀均正常,所以推測FPGA給PHY芯片的發送數據的時序不正常。

圖2 發送時鐘偏移2ns約束代碼

修改代碼,不對發送時鐘進行2ns的偏移,如圖3所示。使用TestCenter對以太網口進行測試,以太網口正常地工作。

圖3 發送時鐘不進行偏移2ns

問題原因定位

推測在不同的PHY芯片的工作模式下,對時鐘的要求不一樣。

之前使用的REALTEK的RTL8211E PHY芯片,需要對發送時鐘進行2ns的延遲,查找該 PHY芯片手冊, PHY芯片對發送時鐘有圖4所示的要求。表格中明確指出,需要自己添加時鐘和數據之間的2ns時延。

圖4 RTL8211E的發送時鐘

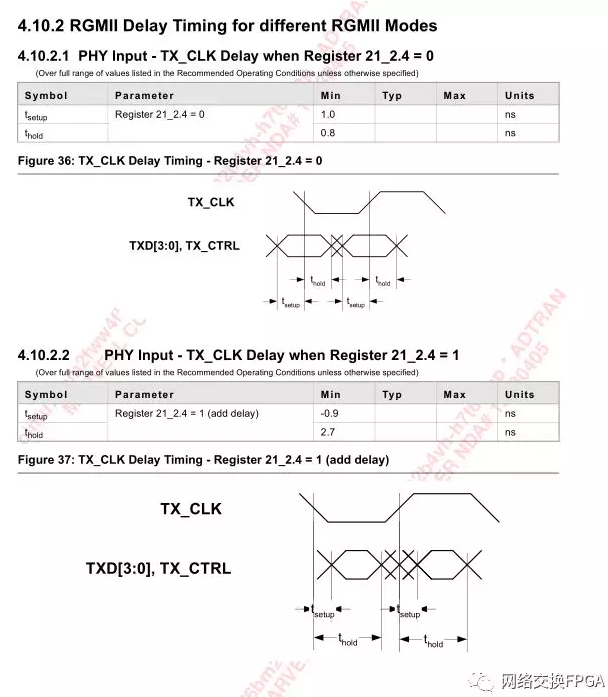

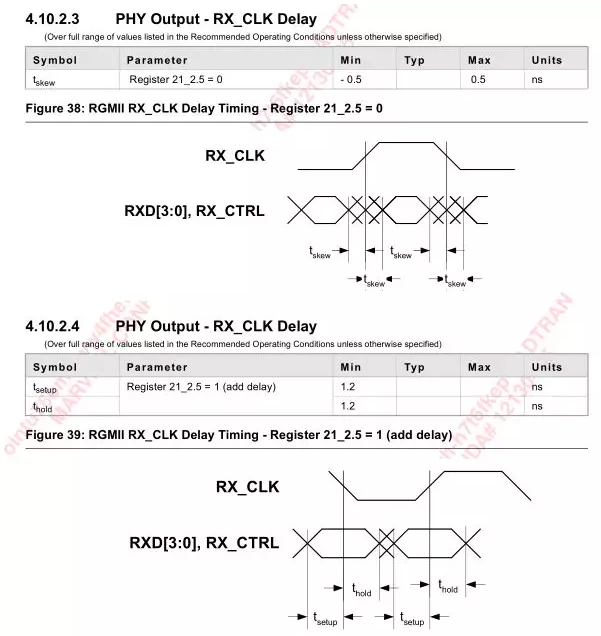

查找目前調試板子上所使用MARVELL的88e1512 PHY芯片的芯片手冊,發現RGMII接口有4種不同的時鐘工作模式。

圖5 88e1512的4種時鐘工作模式

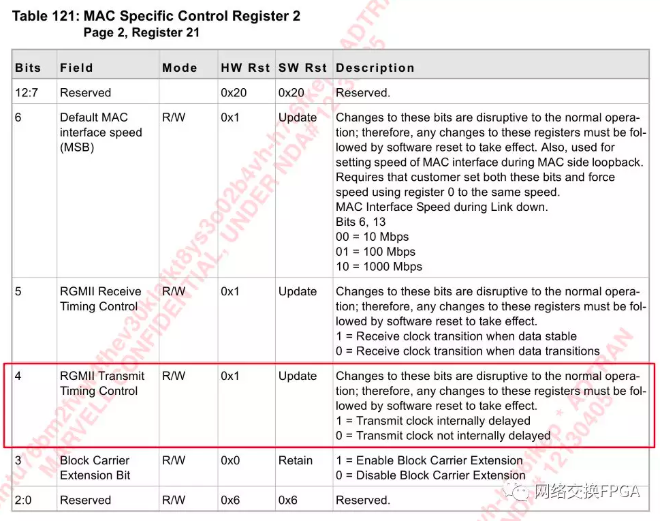

4種時鐘工作模式下的信號時序圖如圖6、圖7所示,結合上板現象,推測當前的工作模式為add delay模式,即Register21_2.4=1。

圖6 RGMII發送時序

圖7 RGMII接收時序

圖8 寄存器的時鐘模式配置

由上面圖6、圖7和圖8可以看出,跟前面RTL8211E PHY芯片不同的是,MARVELL的88e1512 PHY芯片可以配置PHY與FPGA的RGMII接口時鐘信號和數據信號是否已經相對偏移2ns。也就是說,可以通過讀取PHY芯片相應寄存器的方法來看默認的工作模式。

經驗總結:遇到RGMII接口調試時,最關鍵的是要查看PHY芯片的型號,查閱PHY芯片手冊,通過MDIO讀取PHY芯片寄存器的值,看RGMII接口上數據和時鐘是否偏移2ns,再決定FPGA對應管腳約束是否進行偏移!

用VIO方法讀取或配置PHY芯片的寄存器

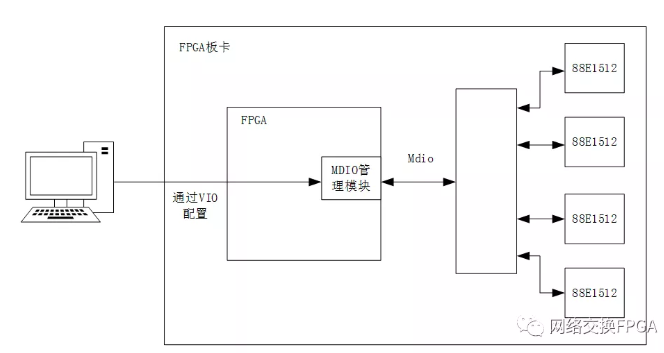

在沒有CPU的情況下,對PHY芯片中寄存器在線讀取的最好辦法使用VIO通過MDIO接口對PHY芯片中的寄存器進行讀取。具體方法可以查看本公眾號之前文章:

一種動態調整RGMII接口時序的方法

Vivado進行FPGA調試“犯罪現場”,在仿真環境中重現方法

使用VIVADO中VIO模擬CPU接口進行在線寄存器讀寫調試(附源代碼)

干貨:Vivado 直接修改RAM初始化文件,避免重新綜合、實現的方法

上圖為測試場景,由FPGA芯片通過24個Mdio接口控制24個88E1512 PHY芯片。

具體的測試步驟為:通過VIO配置MDIO管理模塊PHY地址、寄存器地址,然后選擇讀操作讀取某一PHY芯片的寄存器的值,結合PHY的工作狀態,判斷該寄存器是否被正確讀取。由于執行讀操作時是采用先寫入地址,在讀取數據的方式,因此只測試讀操作就可以完整的測試MDIO管理模塊的功能。以下是VIO對應的調用代碼。

//-----------------------------

mdio_module_VSC8658 U_mdio_module (

.mdc(mdc_o),

.mdio(mdio),

.reset(reset),

.mdir (mdir),

.execute(execute), //

.req(req), //讀 tb用

.phy_addr(phy_addr),

.reg_addr(reg_addr),

.data_phy(data_phy),

.data_rd(data_rd),

.op_done(op_done)

);

//-----------------------on board-----------------------------------

vio_0 u_vio (

.clk(clk), // input wire clk

.probe_out0(req), // output wire [0 : 0] probe_out1

.probe_out1(phy_addr), // output wire [4 : 0] probe_out2

.probe_out2(reg_addr), // output wire [4 : 0] probe_out3

.probe_out3(data_phy) // output wire [15 : 0] probe_out4

);

//-----------------

//----------------------mdc generate--------------------------------

//mdc should be 0~12.5MHz, the module is n*2 Divide

mdio_clk #(.Divider(25)) U_mdio_clk(

.reset (reset),

.clk(clk) ,

.clk_o(mdc_o)

);

//-------------------------------------------------------------------

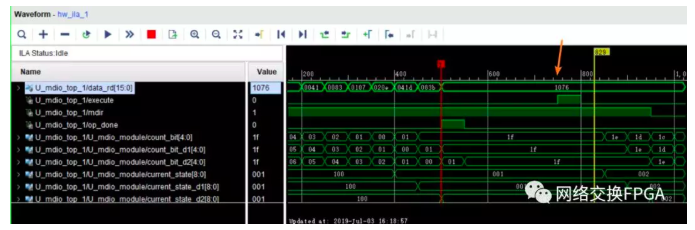

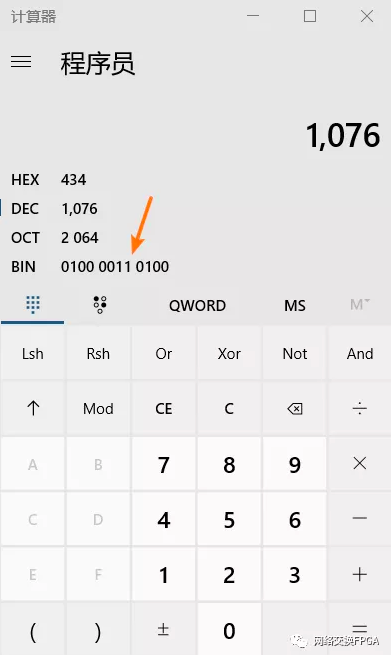

通過VIO和MDIO讀取相應寄存器的值,如圖10所示,讀取到的值為1076,換算成2進值為0000_0100_0011_0100,對應的工作模式為圖8所示的Transmit clock internally delayed,即 add delay模式,不需要對時鐘進行2ns的偏移。

圖9 寄存器的地址

圖10 讀取的寄存器數值

圖11 用windows自帶的計算器看二進制

確認完之后,Testcenter打流,一切OK。但有時候,因為PCB設計的問題,比如RGMII接口的時鐘未采用專用的時鐘管腳,或者是對應的4bit數據信號不在FPGA芯片的同一個BANK,就會導致RGMII接口無論如何調整時鐘與數據之間的相位關系,該RGMII接口都無法正常工作。所以,能夠正常工作的前提是硬件的連線關系及PCB板是OK的。

FPGA使用RGMII接口與PHY芯片連接時經驗總結

事實上,相對于Altera的FPGA,Xilinx的FPGA在使用RGMII接口與PHY芯片相連時會比較講究。以下歸納幾點與大家分享。

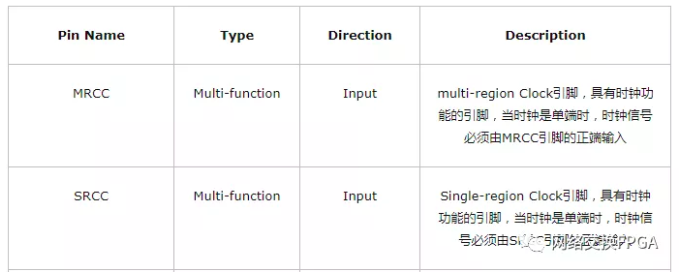

1、rgmii信號中的接收時鐘phy_rxclk為單端時鐘,如果將此時鐘接到FPGA中多功能時鐘引腳(MRCC或SRCC)上時,必須從正端(P)輸入;

每個PHY芯片的tx和rx信號接在FPGA的同一個bank中,其中tx_clk和rx_clk需要接入bank中時鐘專用管腳的P端,且其N端不能夠接其它信號;

2、rgmii中接收信號(rxd、rxclk、rxctl)必須在FPGA中同一個bank或者相鄰bank上,如果是在相鄰bank上,rxclk必須接到MRCC中;

每個PHY芯片有4個rxd、4個txd、2個ctl信號,每個PHY共10個,4個PHY共40個信號;接收發送每個PHY各有兩個時鐘,總共1個PHY占用12個引腳。理論上1個bank可以接4個PHY芯片;

3、注意PHY芯片的供電電壓與FPGA的供電電壓是否相同;

4、每個PHY芯片采用單獨的晶振產生參考時鐘;(本公眾號之前文章SDN先驅Nick教授以及netFPGA無法完美實現6802時間同步一文中就曾指出netFPGA就疑似存在此問題,由于抖動過大,多個端口無法實現6802同步);‘’

RGMII接口與GMII接口

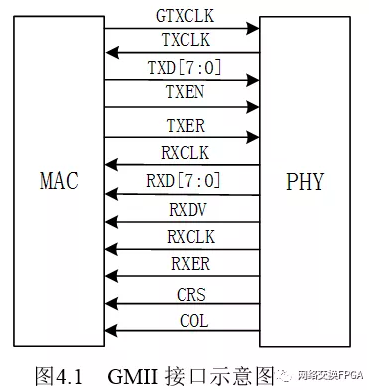

在MAC核與PHY芯片的通信過程中,存在多種接口形式,如MII、GMII、RGMII、XGMII等,千兆以太網端口中以GMII(GigabitMedia Independent Interface)和RGMII(ReducedMedia Independent Interface)最為常見。GMII能夠支持10Mbps、100Mbps、1000Mbps的數據傳輸,其關鍵接口信號如圖4.1所示。

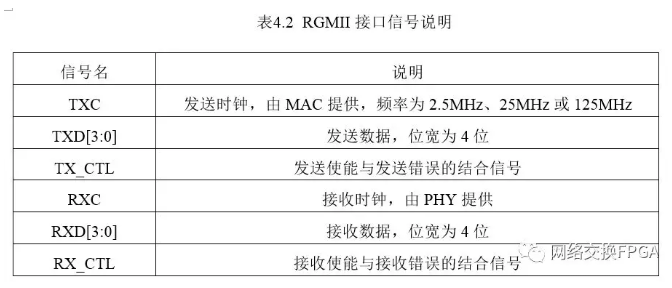

相比與GMII,RGMII接口的信號線大幅減少至12根,移除了其中不必要的TXER、RXER、COL、CRS,并將數據線寬度由8位縮減至4位,但同樣能夠支持10Mbps、100Mbps和1000Mbps傳輸,其接口信號如下圖4.2所示。

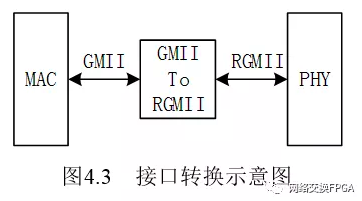

RGMII接口中的雙沿數據信號適于傳輸,但并不適于數據處理,因此在MAC核內處理PHY側數據時首先需要將雙沿數據變換為單沿數據。在Crossbar交換機實現時硬件平臺采用的是RGMII接口,故需要實現RGMII接口與GMII接口的相互轉換,如圖4.3所示。

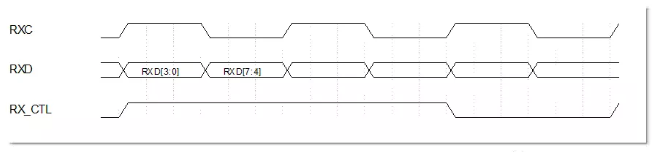

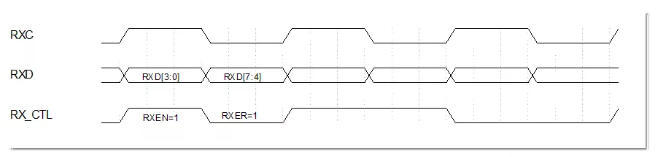

RGMII雖然相比于GMII縮減了大量信號線,但仍能實現1000Mbps數據傳輸,原因在于RGMII采用雙沿傳輸技術,在時鐘的上、下沿同時傳輸數據,那么在一個時鐘周期內就能完成8bits數據的傳輸,與GMII的收發效果相同,如圖4.4所示。而在RGMII中單向只有一個指示信號RX_CTL(TX_CTL),在雙沿傳輸時可將GMII中的RXEN與RXER也分別在RX_CTL的上、下沿進行傳輸即可。

在上圖4.4中,RGMII數據在時鐘的上升沿傳輸GMII中的3~0位,在時鐘的下降沿傳輸GMII中的7~4位,一個時鐘完成8bits數據的傳輸。RX_CTL信號持續拉高,表明當前幀正確無誤。

在上圖4.5中,數據傳輸與圖4.4相同,而RX_CTL在時鐘的下降沿跳變為0,代表了GMII中的RXER信號為1,表明傳輸錯誤。而在RX_CTL持續時間結束時,是在時鐘的上升沿拉低,此時在一個完整的時鐘周期內RXEN=0,RXER=0,可知RX_CTL與RXEN、RXER的關系為:RXEN xorRXER = RX_CTL,xor代表異或運算。

為實現RGMII信號與GMII信號的相互轉換,本文借助了Xilinx提供的基于FPGA的幾類原語,原語指Xilinx針對其器件特征開發的一系列常用模塊的名字。下面列出所用原語的名稱及介紹。

(1)IDDR、ODDR

DDR(Dual Data Rate)即雙倍速率,數據在時鐘的上升沿、下降沿均發生變化,IDDR用作將一路雙沿時鐘數據轉換為兩路普通數據,ODDR用作將兩路普通數據幀轉換為一路雙沿時鐘數據,如圖4.6所示。

(2)BUFIO

一種特殊的時鐘buffer,該buffer獨立于全局時鐘之外,適合用作接收源同步數據,但需要之處的是,該buffer輸出的時鐘無法直接驅動邏輯資源,適合驅動IDDR等專用組件。

(3)BUFR

一種特殊的時鐘buffer,獨立于全局時鐘外,該buffer輸出的時鐘用作驅動該區域內的邏輯資源。

(4)IBUFG

一種全局時鐘buffer,在FPGA的時鐘輸入處都應添加IBUFG進行緩沖,使得緩沖后的時鐘線擁有最小的延遲與抖動,且驅動能力大幅增加。

(5)IODELAY1、IDELAYCTRL

IODELAY1為一種可編程的絕對延時組件,可對某一線路添加一定的延時,其延時值由IDEALYCTRL決定。IDELAYCTRL的延時精度為參考時鐘的1/64,如提供200MHz的參考時鐘,延時精度為5ns/64 = 78ps,二者需配合使用。

在接口轉換的硬件實現過程中,分為接收轉換與發送轉換,二者存在較大區別,下面分別給出接收轉換與發送轉換的實現過程。

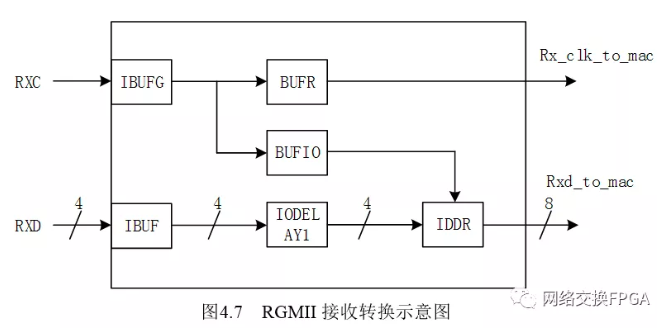

接收轉換即為對RXD、RX_CTL的轉換,在千兆模式下RGMII接口接收數據時,隨路時鐘即RXC為125MHz,且為雙沿傳輸,因此不僅要使用IDDR取出雙沿數據,更要對時鐘進行額外處理,轉換過程如圖4.7所示。

在圖4.7中,并未給出RX_CTL的轉換,其轉換原理與RXD轉換類似,在IDDR轉換后Q1為GMII下的RXDV,Q1 xor Q2為GMII下的RXER。圖中,IBUFG用于將外部輸入的性能較差時鐘RXC轉換為內部可用的高效時鐘RXC_BUFG,BUFIO用于將RXC_BUFG轉換為適合采集源同步數據的時鐘RXC_BUFIO,BUFR用于將RXC_BUFG轉換為適合區域內邏輯資源使用的時鐘Rx_clk_to_mac,相比于RXC_BUFG更適合驅動Rxd_to_mac。IBUF與IBUFG功能相似,但IBUFG只適用于時鐘信號,IBUF為數據線buffer。IODELAY1用作給RXD信號添加一定的延時,抵消時鐘線在經過BUFIO時與在硬件布線時引入的延時,其延時值需要視硬件特性決定,在本文中使用Zedboard實現Crossbar交換機時延時值設置為0。IDDR在圖中只給出一個,在實現時需要用到5個IDDR分別對應于RXD0~RXD4以及RX_CTL。

發送轉換即為對TXD、TX_CTL的轉換,在RGMII的發送過程中,時鐘信號由FPGA內部給出,因此不需要對時鐘線添加額外的buffer,需要指出的是,RGMII的發送時鐘與發送數據并非是沿對齊的,而是如圖4.8所示的中心對齊,采用這樣的時序好處在于對于對端接收來說,雙沿采樣更加穩定。

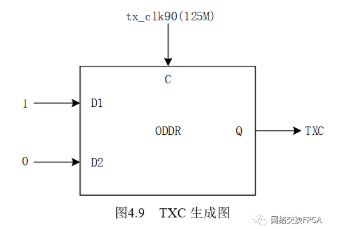

在實際的發送轉換中,首先利用125MHz的時鐘驅動ODDR獲得TXD以及TX_CTL(TX_CTL的轉換中D1為GMII中的TXEN,D2為GMII中的TXEN xorTXER),此時的TXD與TX_CTL與最初的125MHz時鐘是沿對齊的。特殊之處在于,TXC同樣由ODDR產生,該ODDR的驅動時鐘為最初的125MHz時鐘相移90度后的另一時鐘tx_clk90,如圖4.9所示。之所以采用ODDR產生TXC是因為此時的TXC就與TXD、TX_CTL經過了相同的ODDR延時,最終TXC與TXD、TX_CTL就是中心對齊的。

編輯:hfy

-

寄存器

+關注

關注

31文章

5325瀏覽量

120052 -

PHY

+關注

關注

2文章

301瀏覽量

51700 -

RGMII

+關注

關注

0文章

27瀏覽量

12154

發布評論請先 登錄

相關推薦

如何使用VIO去讀取PHY里面對應寄存器測試RGMII接口

如何使用VIO去讀取PHY里面對應寄存器測試RGMII接口

評論