AXI (Advanced eXtensible Interface) 本是由ARM公司提出的一種總線協議, Xilinx從 6 系列的 FPGA 開始對 AXI 總線提供支持,目前使用 AXI4 版本。

AXI總線

ZYNQ有三種AXI總線:

(A)AXI4:(For high-performance memory-mapped requirements.)主要面向高性能地址映射通信的需求,是面向地址映射的接口,允許最大256輪的數據突發傳輸;

(B)AXI4-Lite:(For simple, low-throughput memory-mapped communication )是一個輕量級的地址映射單次傳輸接口,占用很少的邏輯單元。

(C)AXI4-Stream:(For high-speed streaming data.)面向高速流數據傳輸;去掉了地址項,允許無限制的數據突發傳輸規模。

AXI4總線和AXI4-Lite總線具有相同的組成部分:

① 讀地址通道,包含ARVALID, ARADDR, ARREADY信號;

② 讀數據通道,包含RVALID, RDATA, RREADY, RRESP信號;

③ 寫地址通道,包含AWVALID,AWADDR, AWREADY信號;

④ 寫數據通道,包含WVALID, WDATA,WSTRB, WREADY信號;

⑤ 寫應答通道,包含BVALID, BRESP, BREADY信號;

⑥ 系統通道,包含:ACLK,ARESETN信號。

而AXI4-Stream總線的組成有:

① ACLK信號:總線時鐘,上升沿有效;

② ARESETN信號:總線復位,低電平有效

③ TREADY信號:從機告訴主機做好傳輸準備;

④ TDATA信號:數據,可選寬度32,64,128,256bit

⑤ TSTRB信號:每一bit對應TDATA的一個有效字節,寬度為TDATA/8

⑥ TLAST信號:主機告訴從機該次傳輸為突發傳輸的結尾;

⑦ TVALID信號:主機告訴從機數據本次傳輸有效;

⑧ TUSER信號 :用戶定義信號,寬度為128bit。

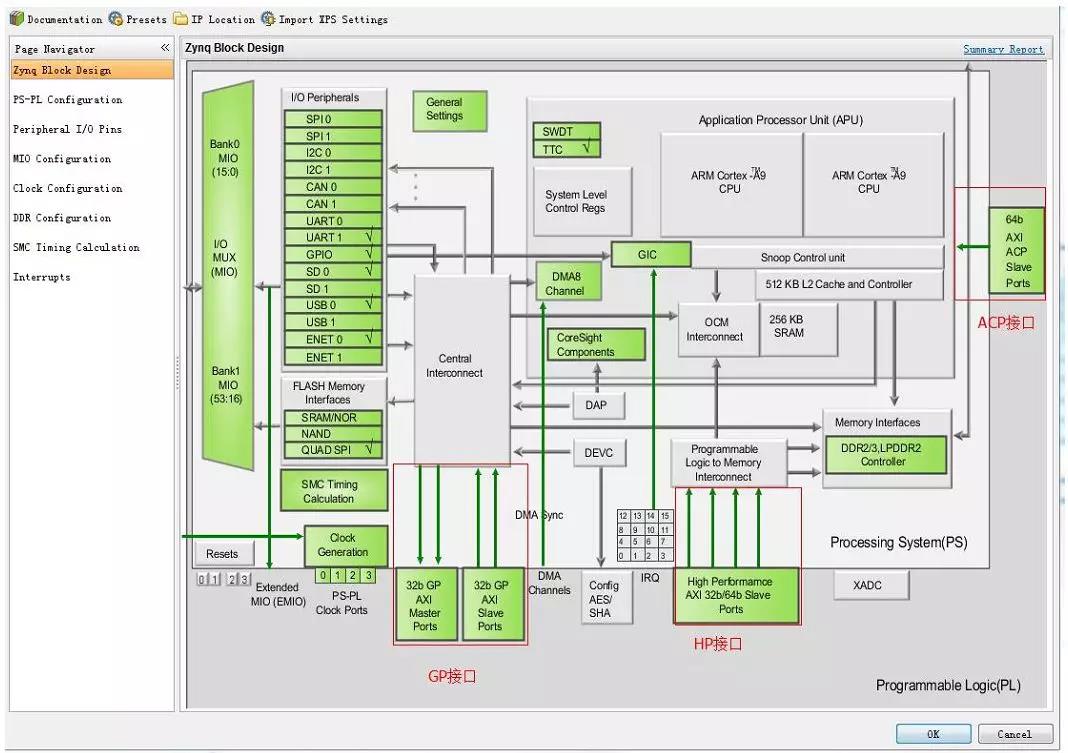

AXI接口

AXI有三種接口:

(A)AXI-GP接口(4個):是通用的AXI接口,包括兩個32位主設備接口和兩個32位從設備接口,用過該接口可以訪問PS中的片內外設。

(B)AXI-HP接口(4個):是高性能/帶寬的標準的接口,PL模塊作為主設備連接(從下圖中箭頭可以看出)。主要用于PL訪問PS上的存儲器(DDR和On-Chip RAM

(C)AXI-ACP接口(1個):是ARM多核架構下定義的一種接口,中文翻譯為加速器一致性端口,用來管理DMA之類的不帶緩存的AXI外設,PS端是Slave接口。

AXI協議

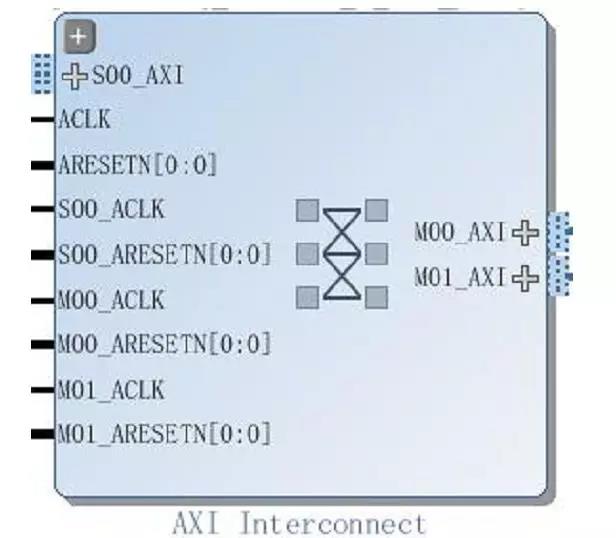

協議的制定是要建立在總線構成之上的。因此說AXI4,AXI4-Lite,AXI4-Stream都AXI4協議。AXI總線協議的兩端可以分為分為主(master)、從(slave)兩端,他們之間一般需要通過一個AXI Interconnect相連接,作用是提供將一個或多個AXI主設備連接到一個或多個AXI從設備的一種交換機制。

AXI Interconnect的主要作用是,當存在多個主機以及從機器時,AXIInterconnect負責將它們聯系并管理起來。由于AXI支持亂序發送,亂序發送需要主機的ID信號支撐,而不同的主機發送的ID可能相同,而AXI Interconnect解決了這一問題,他會對不同主機的ID信號進行處理讓ID變得唯一。

AXI協議將讀地址通道,讀數據通道,寫地址通道,寫數據通道,寫響應通道分開,各自通道都有自己的握手協議。每個通道互不干擾卻又彼此依賴。這是AXI高效的原因之一。

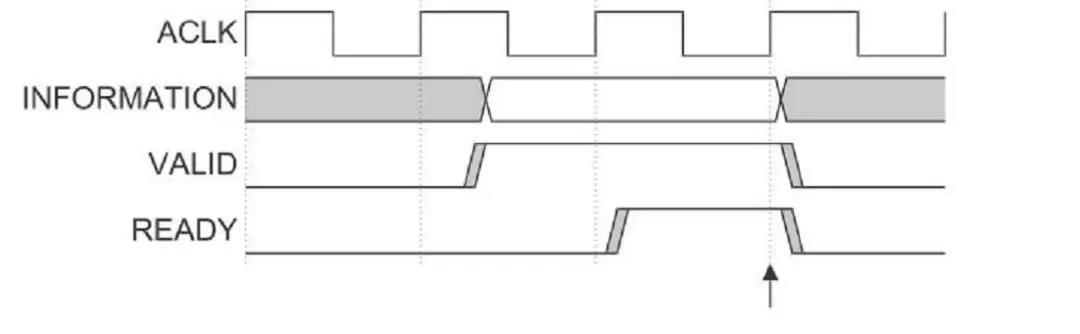

01:AXI握手協議

AXI4 所采用的是一種 READY,VALID 握手通信機制,簡單來說主從雙方進行數據通信前,有一個握手的過程。傳輸源產生 VLAID 信號來指明何時數據或控制信息有效。

而目地源產生READY信號來指明已經準備好接受數據或控制信息。 傳輸發生在VALID和 READY信號同時為高的時候。

如下圖中的一種實例:

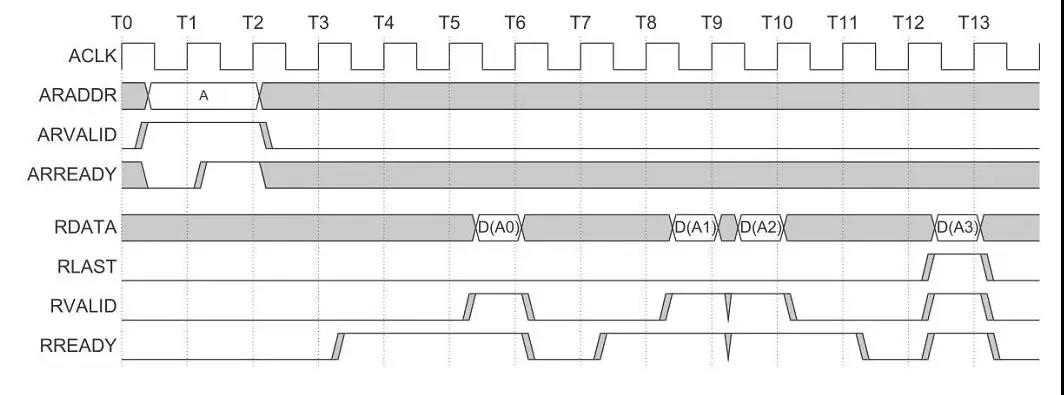

02:突發式讀寫

突發式讀的時序:

當地址出現在地址總線后,傳輸的數據將出現在讀數據通道上。設備保持VALID 為低直到讀數據有效。為了表明一次突發式讀寫的完成,設備用 RLAST 信號來表示最后一個被傳輸的數據。

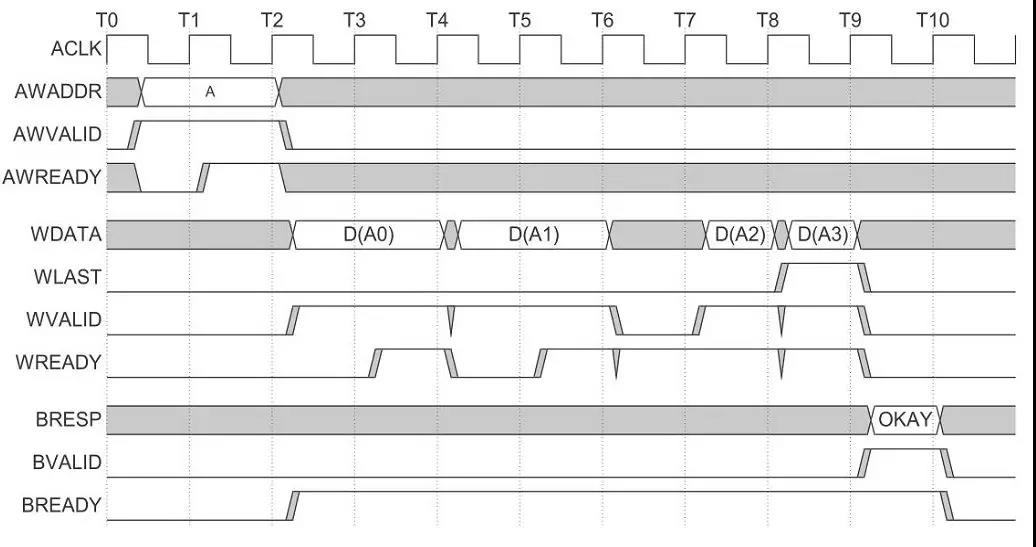

突發式寫的時序:

這一過程的開始時,主機發送地址和控制信息到寫地址通道中,然后主機發送每一個寫數據到寫數據通道中。當主機發送最后一個數據時,WLAST 信號就變為高。當設備接收完所有數據之后他將一個寫響應發送回主機來表明寫事務完成。

編輯:hfy-

Xilinx

+關注

關注

70文章

2133瀏覽量

120114 -

總線協議

+關注

關注

0文章

96瀏覽量

14794 -

Zynq

+關注

關注

9文章

603瀏覽量

46914

發布評論請先 登錄

相關推薦

SoC設計中總線協議AXI4與AXI3的主要區別詳解

Xilinx ZYNQ 動手實操演練

AXI總線協議總結

使用 PCIE 更新 AMD ZYNQ? 的 QSPI Flash 參考設計

XILINX FPGA IP之AXI Traffic Generator

ZYNQ的ARM和FPGA數據交互——AXI交互最重要的細節

AXI IIC總線接口介紹

什么是AXI?AXI如何工作?

適用于Xilinx Zynq UltraScale+ MPSoC應用的電源參考設計

基于AXI總線的DDR3讀寫測試

基于Xilinx FPGA AXI-EMC IP的EMIF通信測試

Xilinx zynq AXI總線全面解讀

Xilinx zynq AXI總線全面解讀

評論