新建工程

1. 打開vivado2017.4,在出現的對話框中選擇創建一個工程,如圖所示。這一步是為了創建一個ZYNQ的工程。

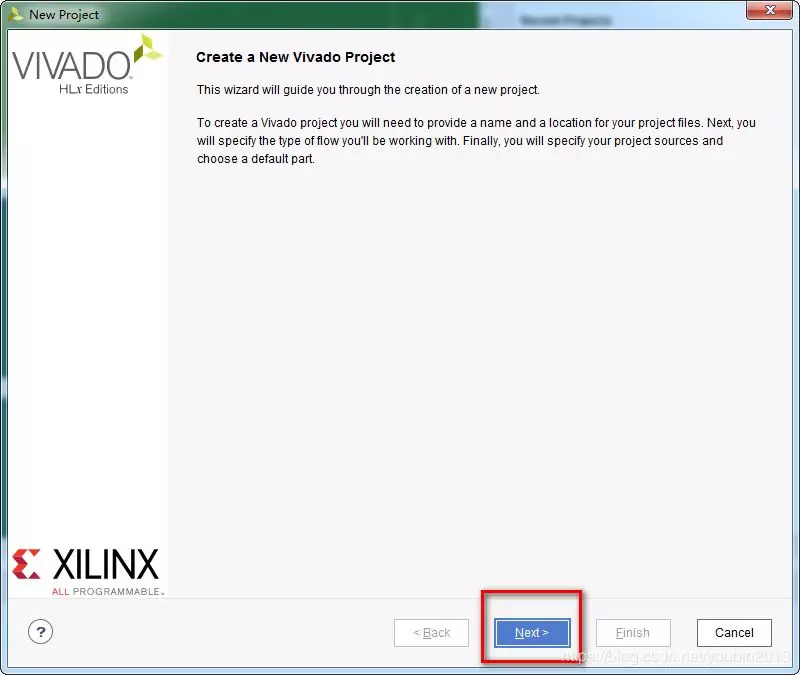

2. 點擊創建工程后,出現對話框如圖所示,然后點擊對話框中的下一步。這一步表示這是一個創建工程的向導,通過該向導去新建一個工程。

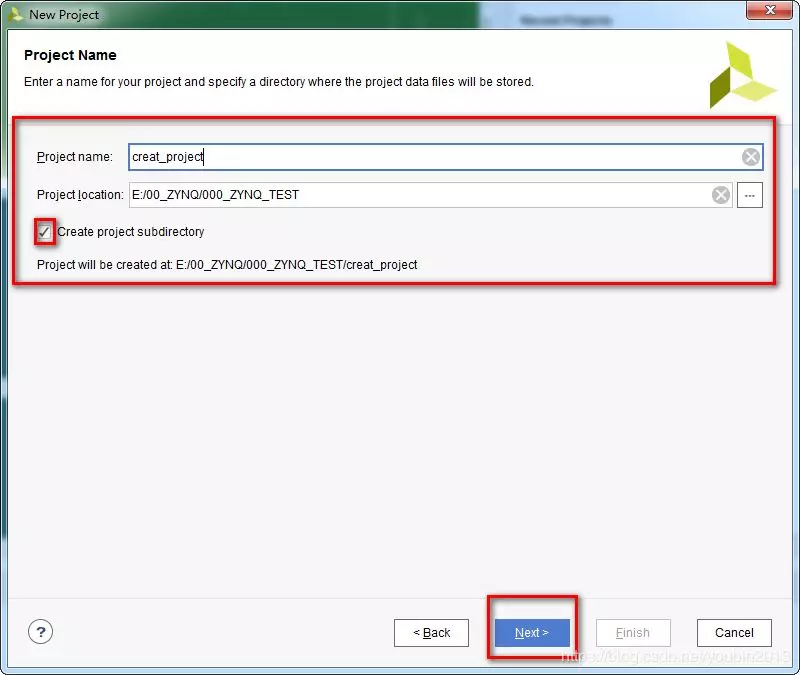

3,此時會出現一個對話框如圖所示,這一步給工程命名,并且確定工程的保存路徑,下面的小勾表示創建一個和工程名字相同子目錄,然后點擊下一步。

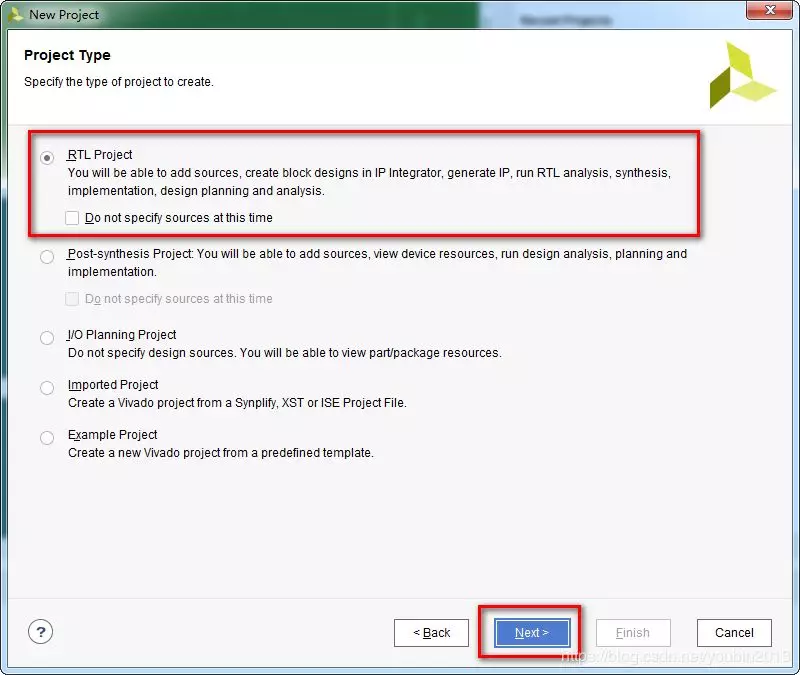

4,下一步后出現對話框如圖所示,該步驟是確定需要創建工程的類型,我們選擇RTL工程,該類型的工程可以添加源文件,創建IP大框架,生成IP,綜合分析和實現等。點擊下一步。

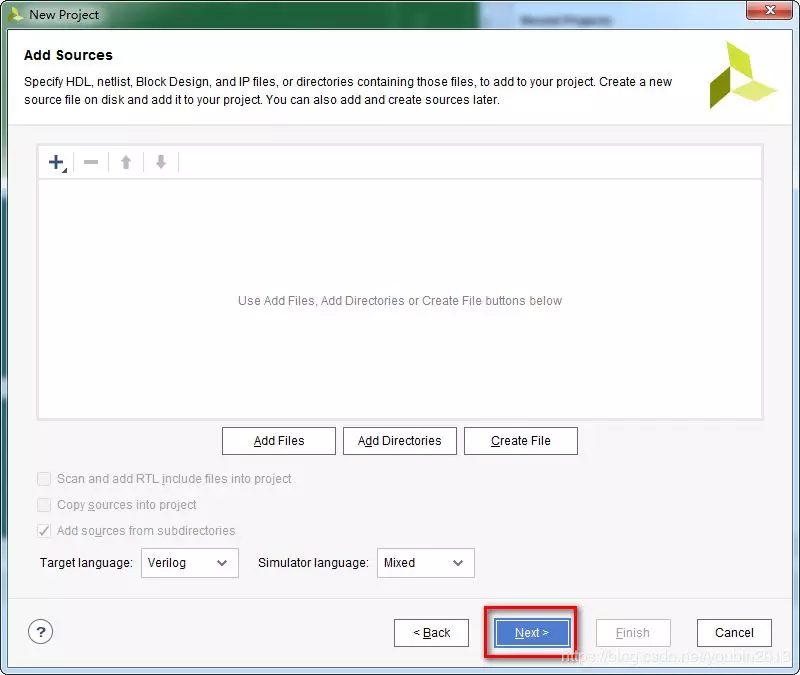

5,此時出現對話框如圖所示,該步驟表示添加現有的源文件,創建一個空的工程,這步直接點擊下一步。

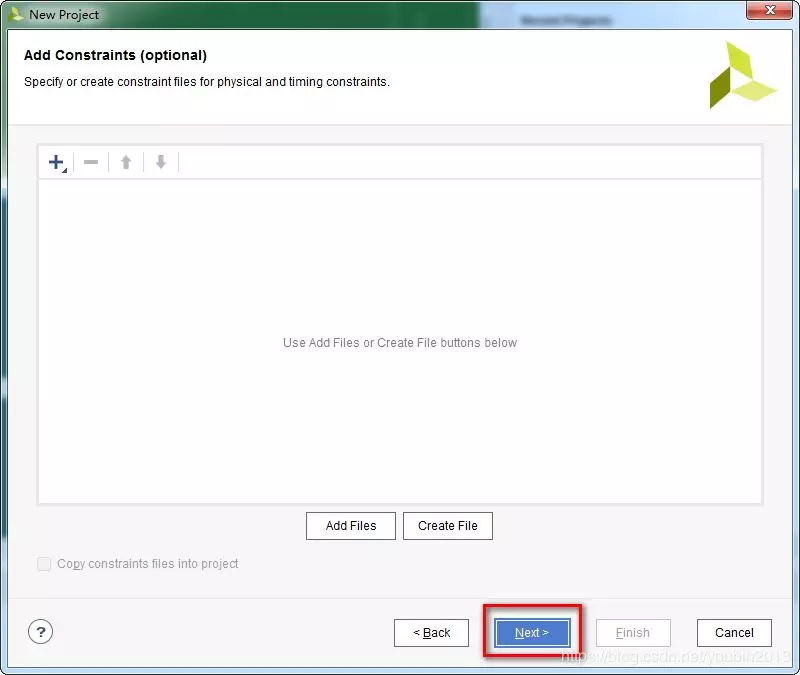

6,出現對話框如圖所示,該步驟為添加現有的約束文件,創建空的工程,直接點擊下一步。

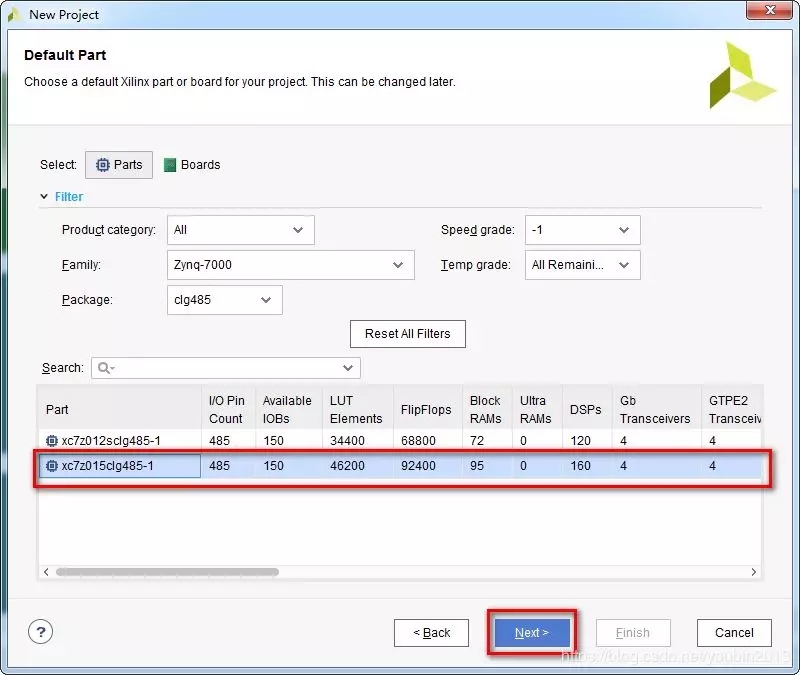

7,出現對話框如圖所示,該步驟選擇芯片的類型,本工程建立在7015型號上,所以選擇xc7z015clg485-1,然后點擊下一步。

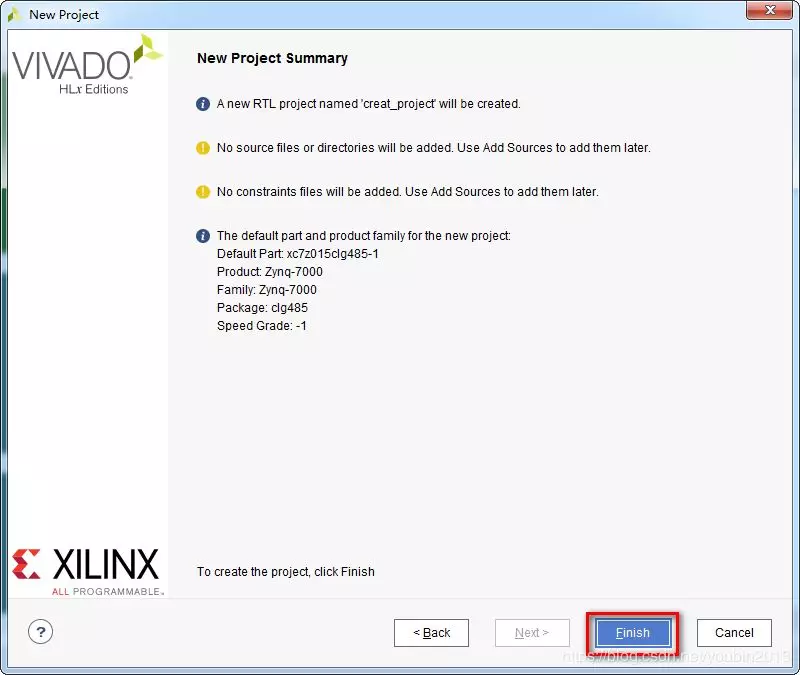

8,此時出現對話框如圖所示,該步驟表示工程創建完成,顯示所創建的工程的信息,點擊完成。

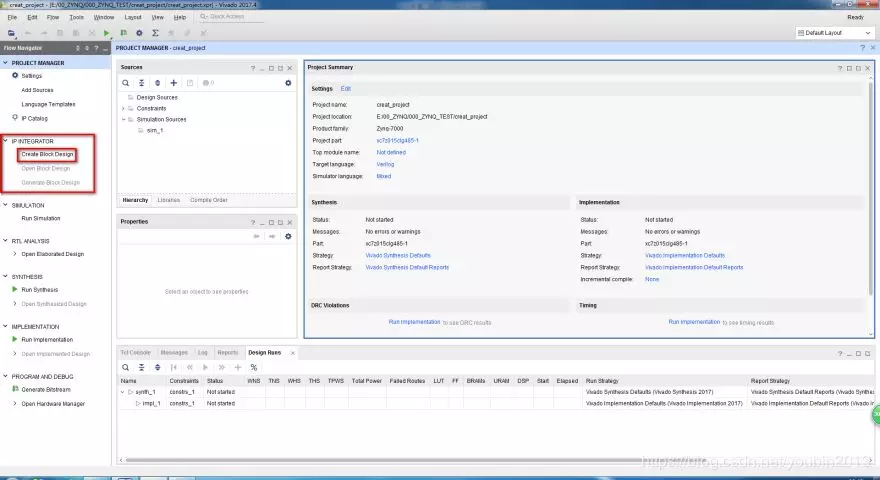

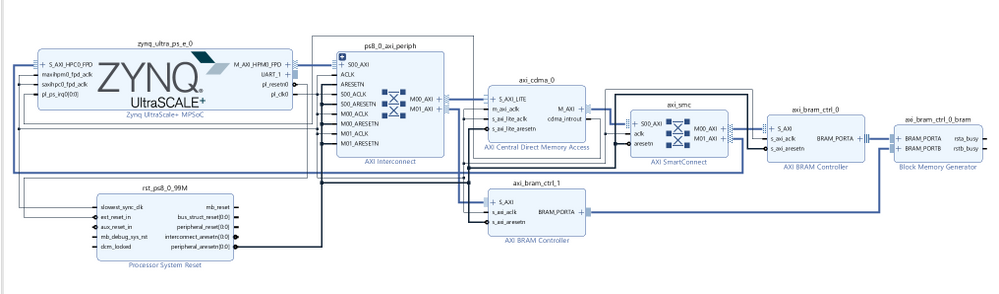

9,空的工程創建完成以后出現界面如圖所示,需要往里面添加需要的IP大框架,在IP向導下拉表中雙擊創建IP框架,建立IP框架圖。

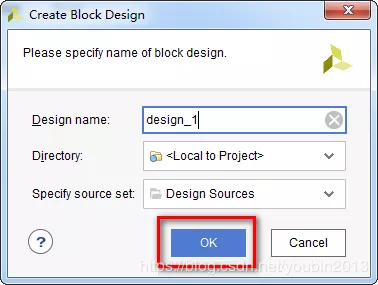

10,雙擊后出現創建設計對話框如圖所示,點擊OK。

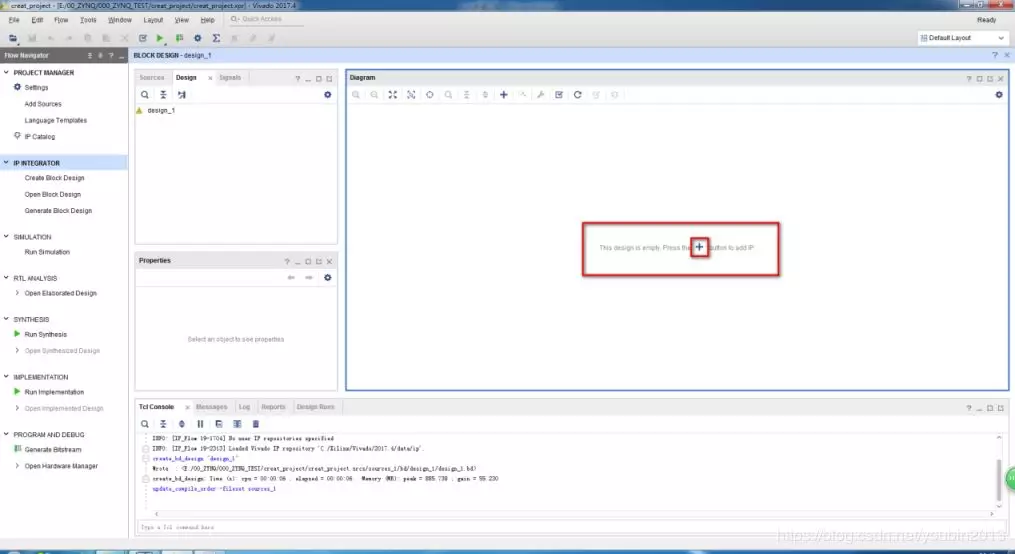

11,創建背框后出現如圖的對話框,點擊diagram中的大空白頁中的“+”圖標,添加IP到設計框架。

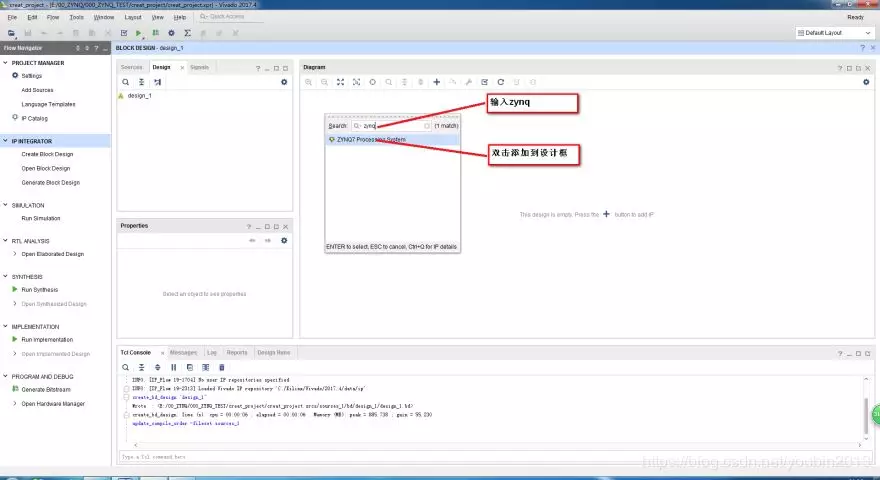

12,點擊+號后添加ZYNQ的IP到設計框架中,如圖所示,在輸入框中輸入zynq,下拉表中會有對應的zynq出現,雙擊下面的IP添加到設計框中。

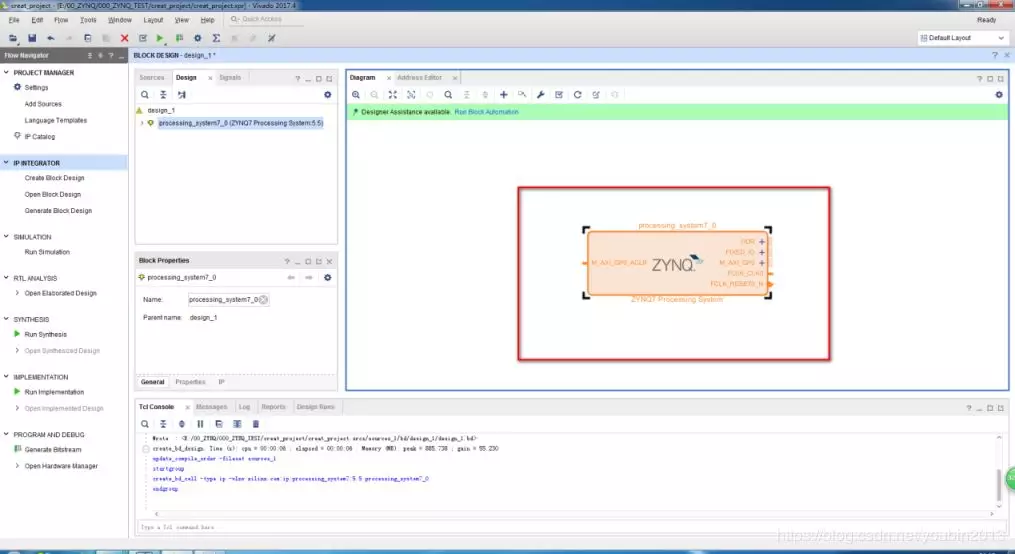

13,添加zynq的ip后對話框如圖所示,雙擊圖中的ZYNQ核心IP,出現配置界面。

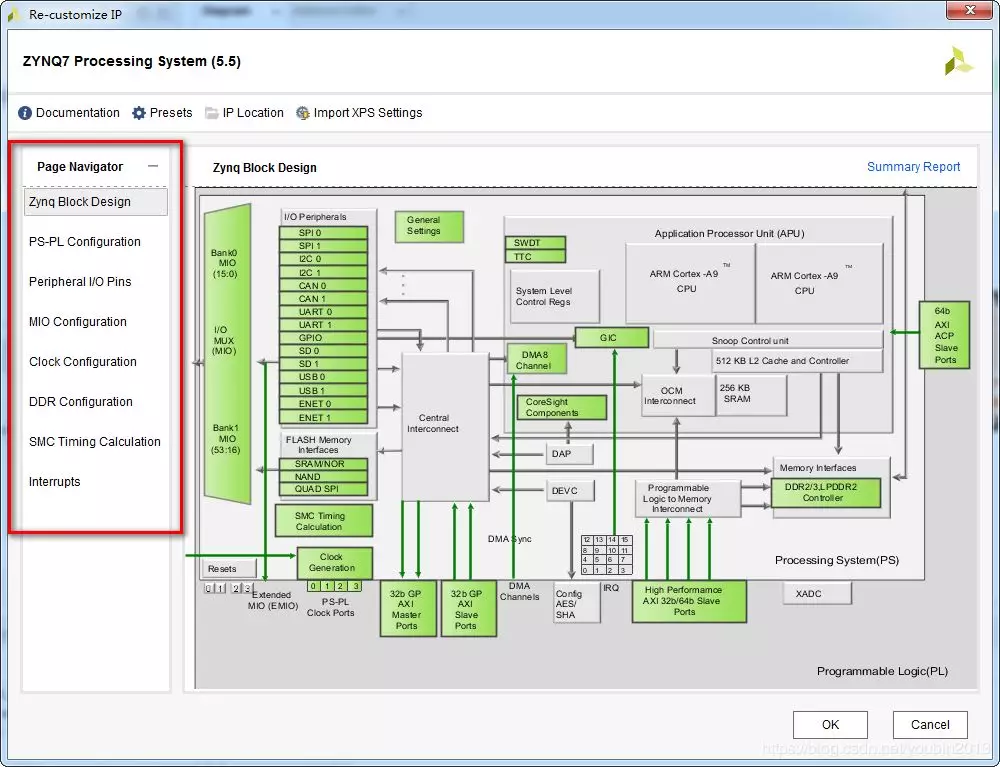

14,出現的配置界面如圖所示,這時可以對ZYNQ進行配置了,其Page Navigator 界面下有 8 個子項,分別為 Zynq Block Design,PS-PL Configuration,

Peripheral I/O Pins,MIO Configration,Clock Configuration,DDRConfiguration,SMC Timing Calculation,Interrupts。這些頁面選項是針對 ZYNQ 的不同硬件模塊的配置,其中PS_PL 頁面提供了 PS 到 PL 的相關接口配置信息以及 PS 部分一些配置信息;Peripheral I/O Pins 頁面主要是對一些通用外設接口的配置;MIO Configruation 頁面主要是對 MIO 以及EMIO 的分配控制;Clock Configruation 頁面主要是對 PS 端時鐘資源的配置和管理;DDR Configration 頁面主要是對 DDR 控制器一些參數的配置;Interrupts 頁面主要是對中斷進行配置管理。

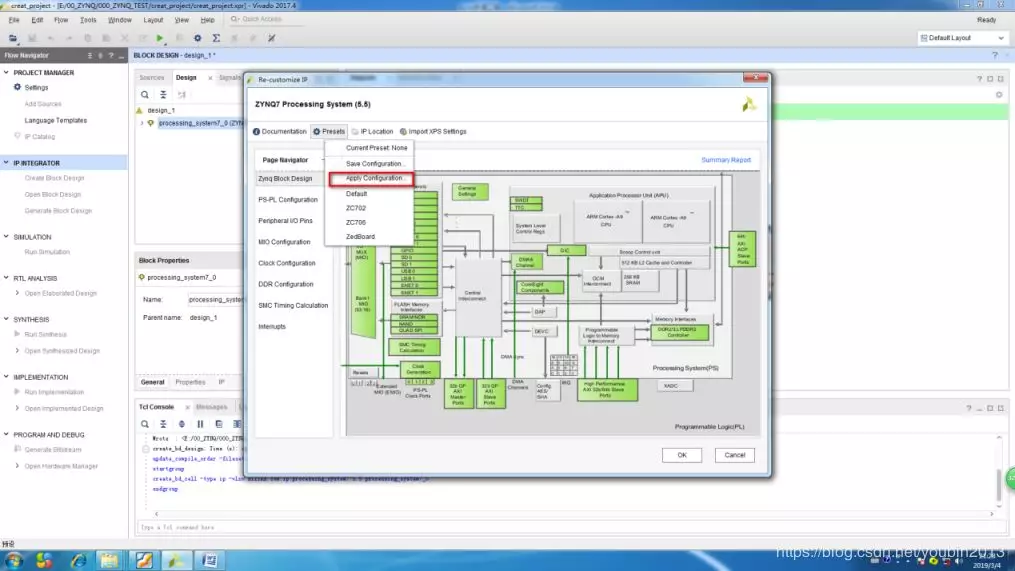

15,可以通過page navigator中的的八個設計單元分別去配置工程中zynq的硬件外設單元;也可以通過加載腳本的方式配置設計單元;這里通過腳本去設計ZYNQ器件的基本單元,點擊presets,出現下列列表,選擇apply configuration選項,如圖所示。

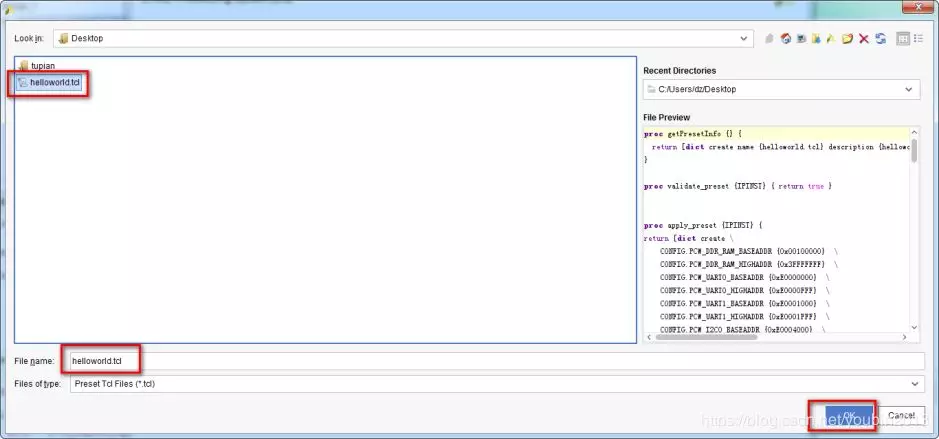

16,然后出現選擇腳本路徑的對話框如圖所示,選擇之前保存的好的最小系統腳本,點擊ok按鈕,配置好ZYNQ的IP。

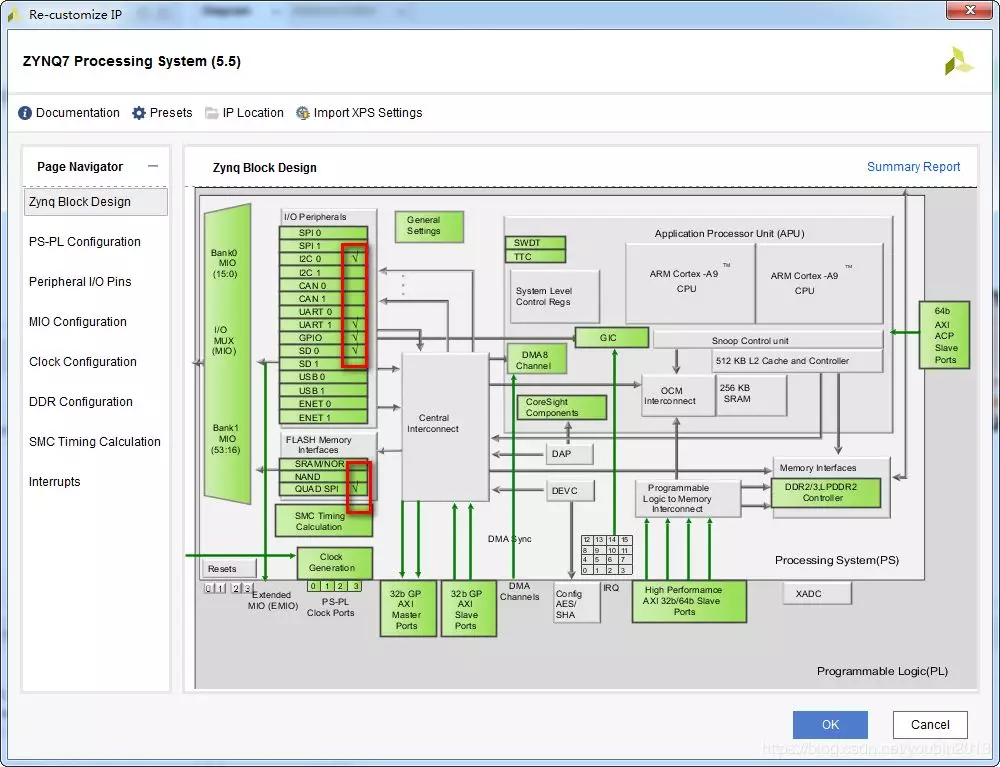

17,待配置好IP后會出現如圖的對話框,表示配置好了相關的屬性和外設,配置了的外設后面會打上勾,點擊ok。

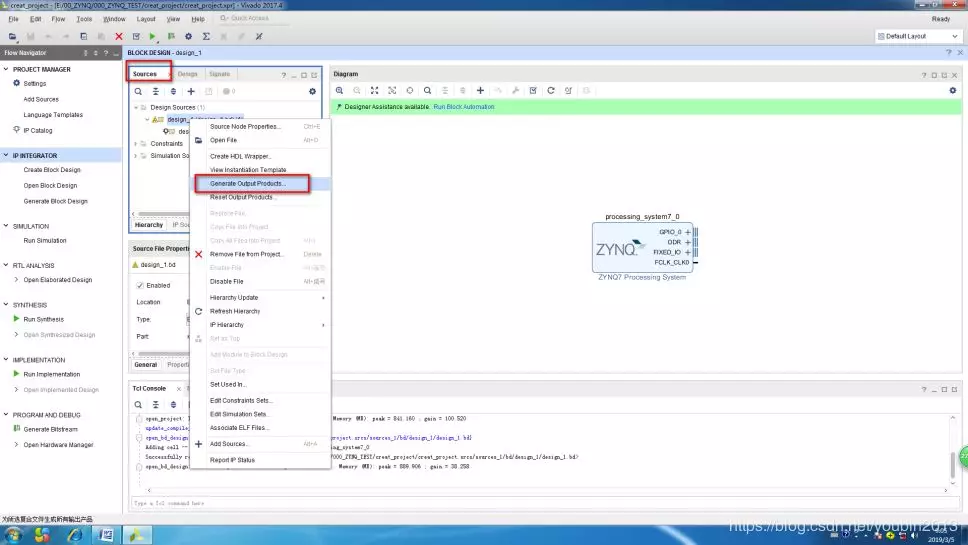

18,配置好IP外設后出現如圖的對話框,點擊紅框中的source選項卡,然后鼠標右鍵點擊在design sources下的design_1(design_1為剛剛設計的IP),在彈出的下拉列表中選擇generate output products,生成輸出的產品。

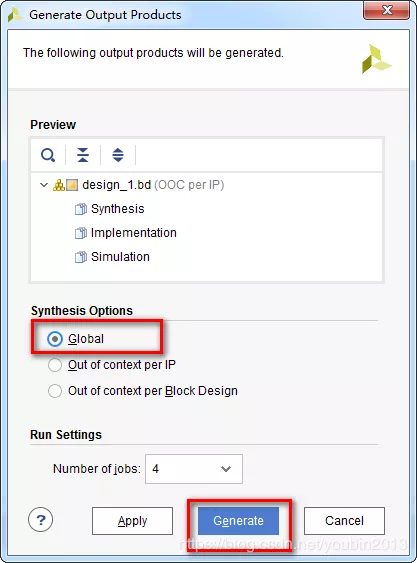

19,點擊generate output products后出現對話框如圖所示,表示將要生成輸出產品,選擇global,并點擊下面的生成。生成成功后點擊OK,

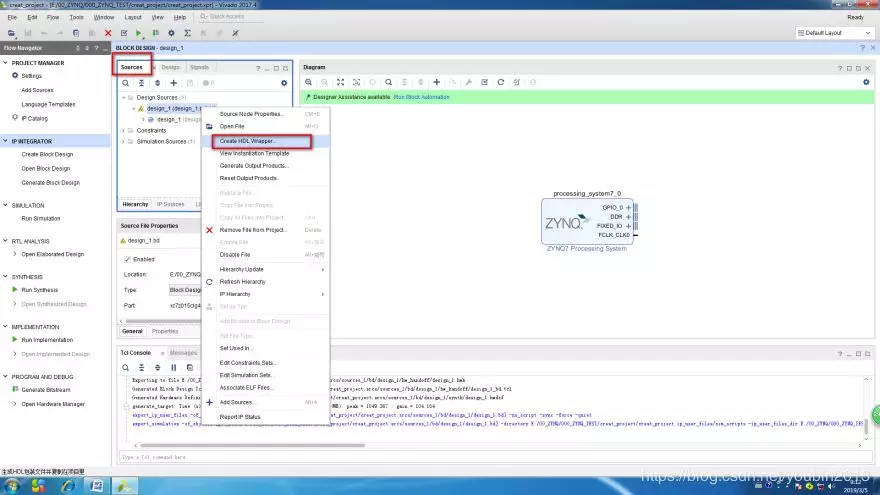

20,再點擊紅框中的source選項卡,然后鼠標右鍵點擊在design sources下的design_1,在彈出的下拉列表中選擇create HDL wrapper,如圖所示,表示生成頂層文件。

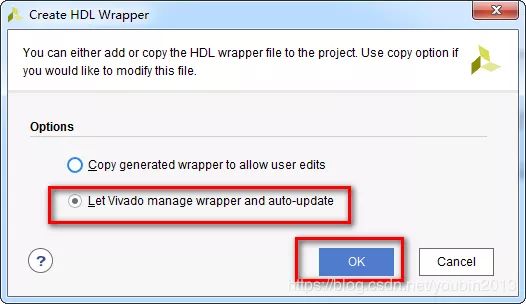

21,生成頂層文件成功后出現如圖所示對話框,點擊OK。

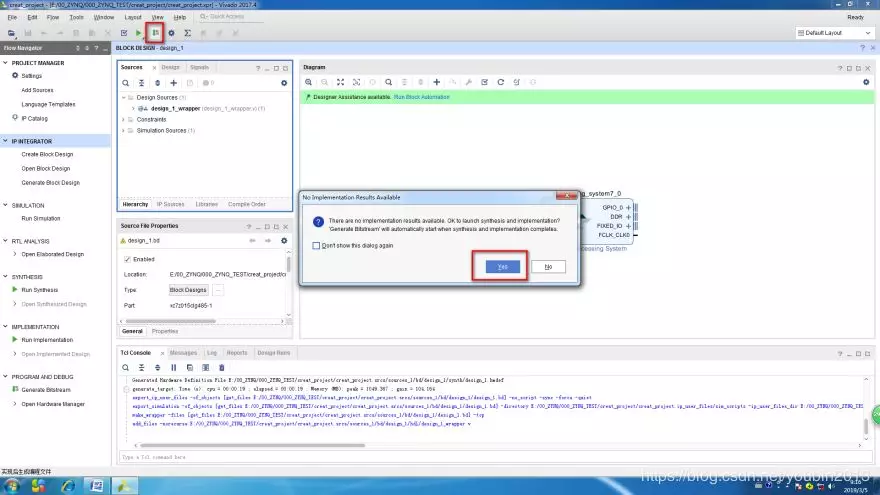

22,生成了頂層文件后,進行綜合實現布線并生成.bit文件,如圖所示,點擊紅框圖標,然后出現對話框是否確認生成bit文件,點擊yes,確定生成文件。

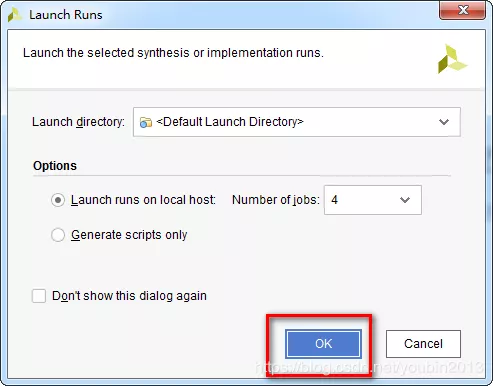

23,點擊yes后出現對話框如圖所示,點擊ok開始生成bit文件。

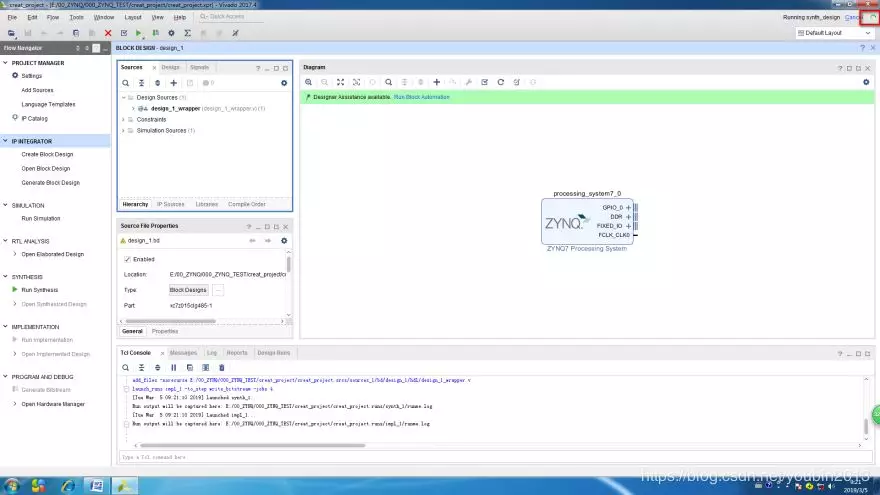

24,然后等待綜合實現布線的完成,等待界面右上角的圈圈轉完,表示.bit文件生成完成,如圖所示。

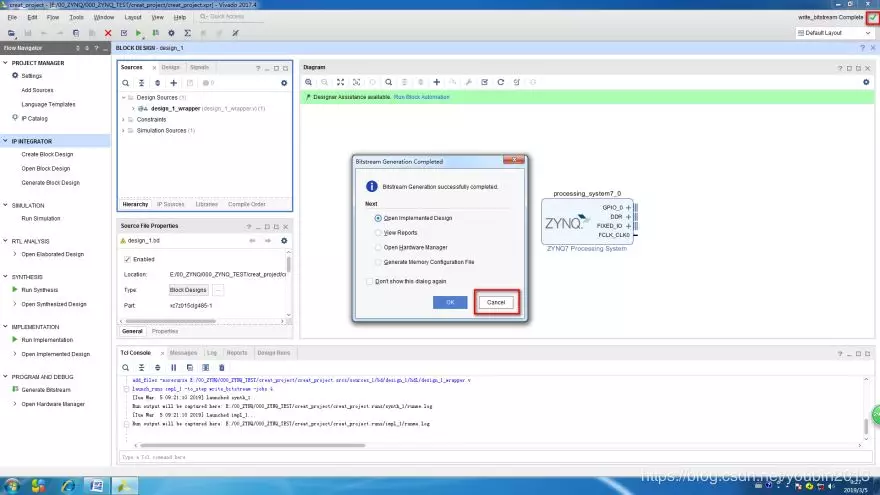

25,生成成功以后會出現如圖所示的對話框,右上角會有勾出現,并且提示是否看生成后的設備布線等具體信息,這里不看點擊cancel。

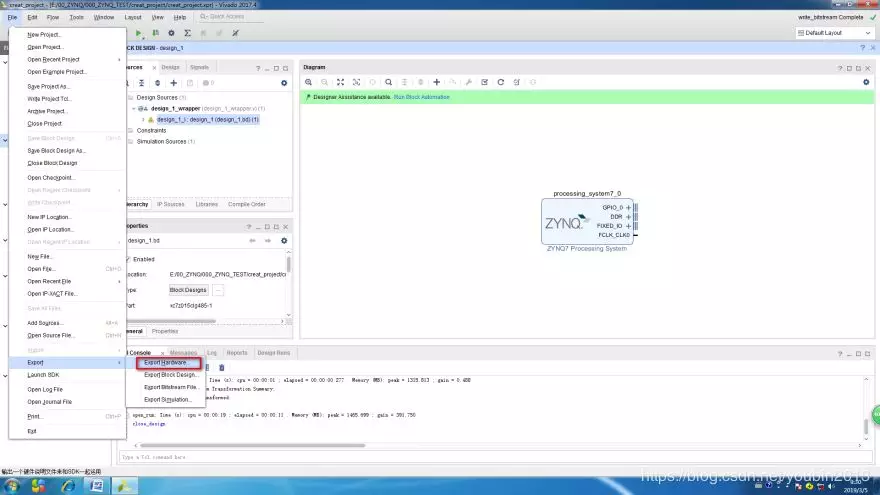

26,生成.bit文件以后,點擊file菜單,在下拉列表中選擇export,并且在子菜單中選擇export hardware,生成硬件平臺,供后續軟件sdk使用,如圖所示。

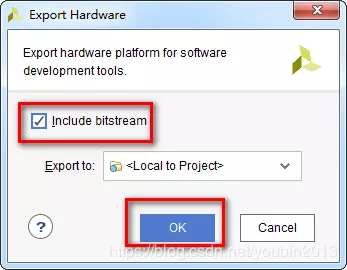

27,后續出現對話框如圖所示,勾選上包含.bit文件,點擊OK,表示生成硬件平臺。

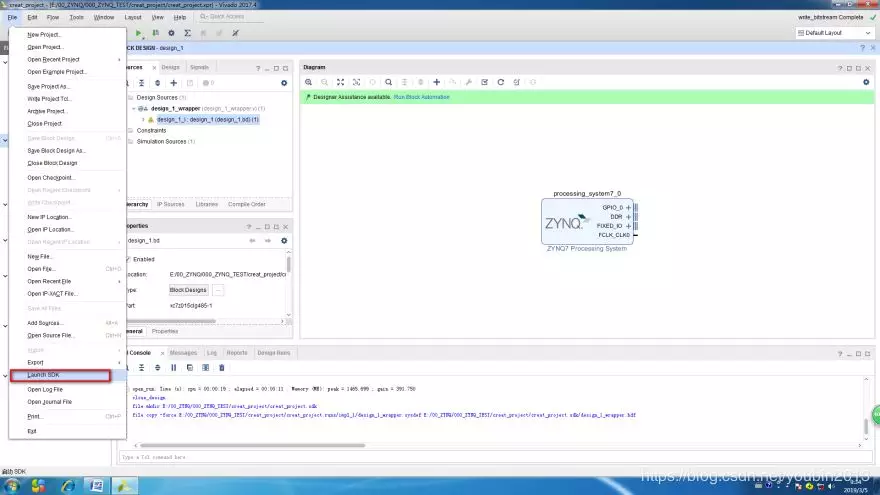

28,有了硬件平臺后,點擊file菜單,在下拉列表中選擇launch SDK,打開ps端開發的SDK,如圖所示。

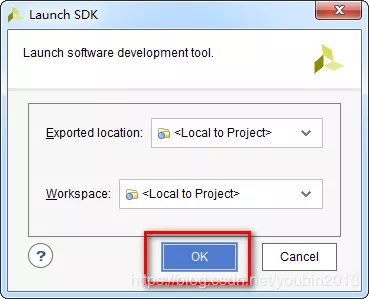

29,然后出現對話框如圖所示,確認SDK的工作空間等信息,點擊OK,至此開始進入到PS端開發SDK。

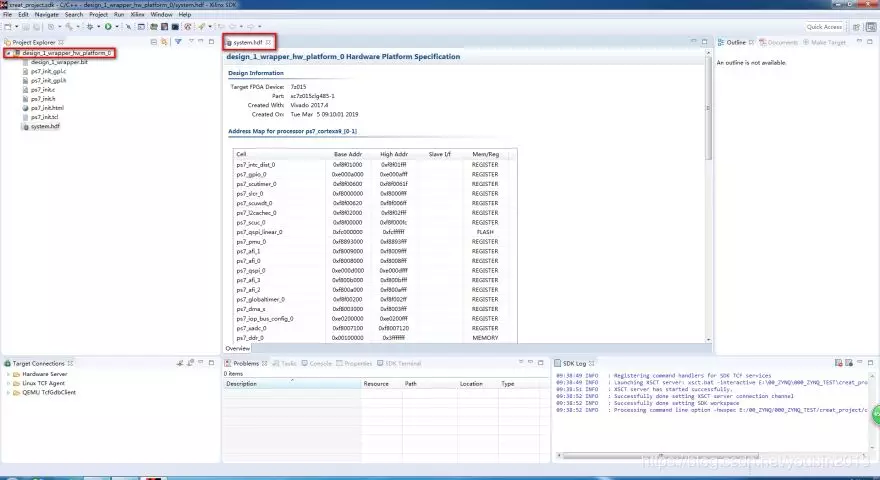

30,等待SDK打開完成,打開后出現界面如圖所示,此時擁有了硬件平臺design_1_wrapper_hw_platform_0。在system.hdf文件中會顯示相應硬件平臺外設的基地址和地址范圍。

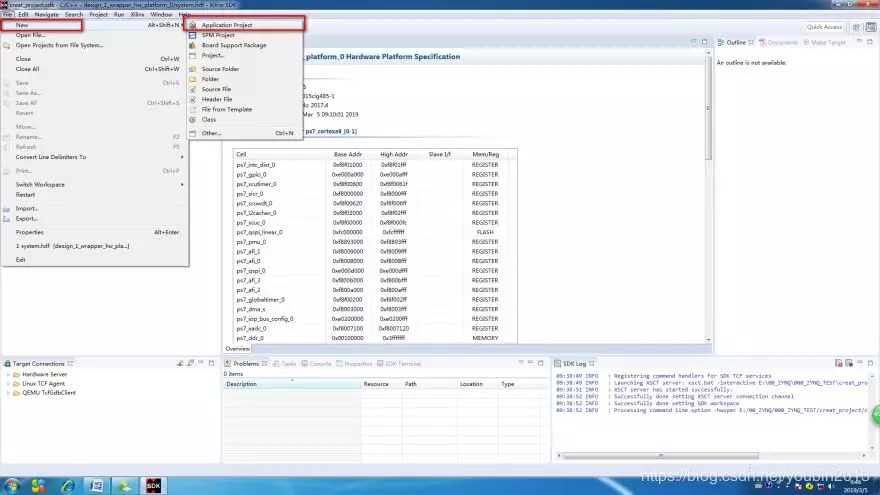

31,擁有硬件平臺后,此時還需要建立軟件工程,軟件工程一般需要建立兩個,一個是FBSL工程,一個是應用工程,FBSL工程是用來做固化啟動芯片的工程,而應用工程則是需要實現的應用程序,這里先新建FBSL工程,點擊file菜單,在下拉列表中選擇new,在子菜單中選擇application project,如圖所示。

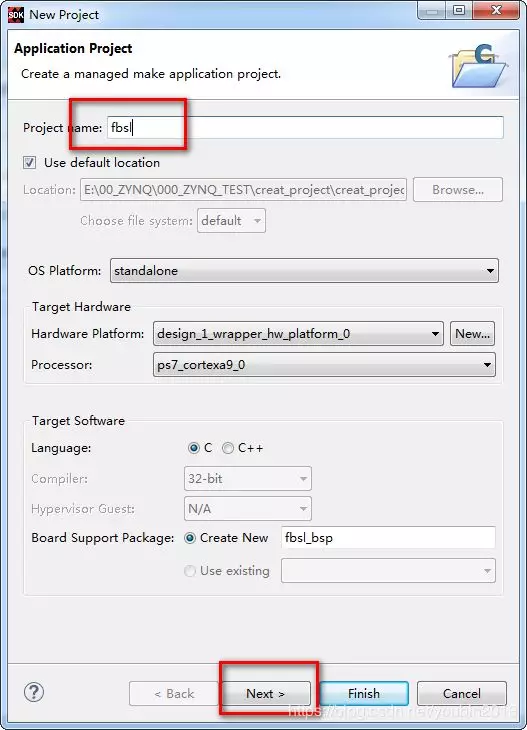

32,然后出現對話框如圖所示,輸入工程名字,選擇工程路徑,一般使用默認路徑,選擇系統平臺standalone,選擇上述的硬件平臺design_1_wrapper_hw_platform_0,選擇操作核心0核(ps_cortexa9_0),確定開發語言為C語言,創建新的板級開發包,然后點擊下一步。

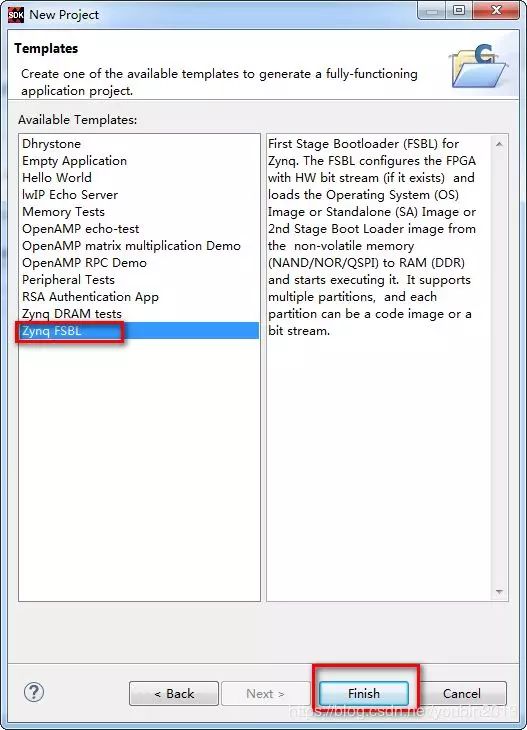

33,后續出現對話框如圖所示,選擇創建工程的模板類型,這里要創建FBSL工程,所以選擇zynq fbsl類型模板,點擊finish,完成工程的新建。

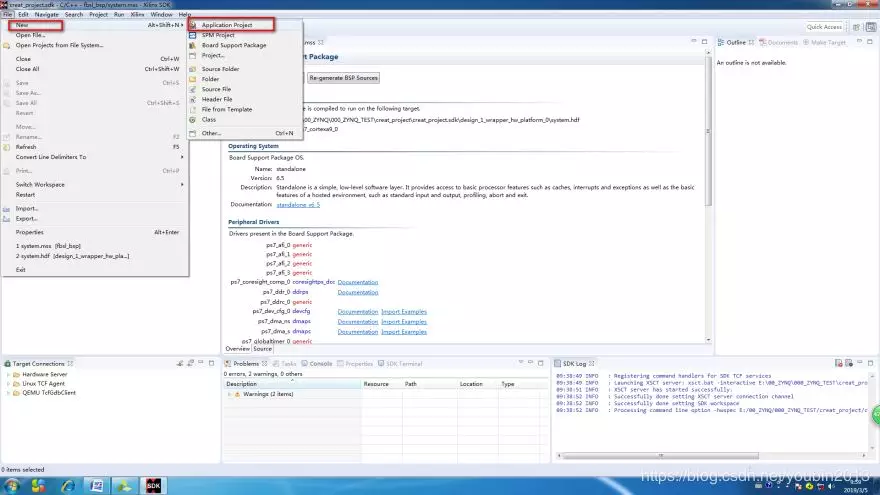

34,有了啟動工程以后,還要有應用程序工程,所以在新建一個應用程序,這里再新建一個應用工程,點擊file菜單,在下拉列表中選擇new,在子菜單中選擇application project,如圖所示。

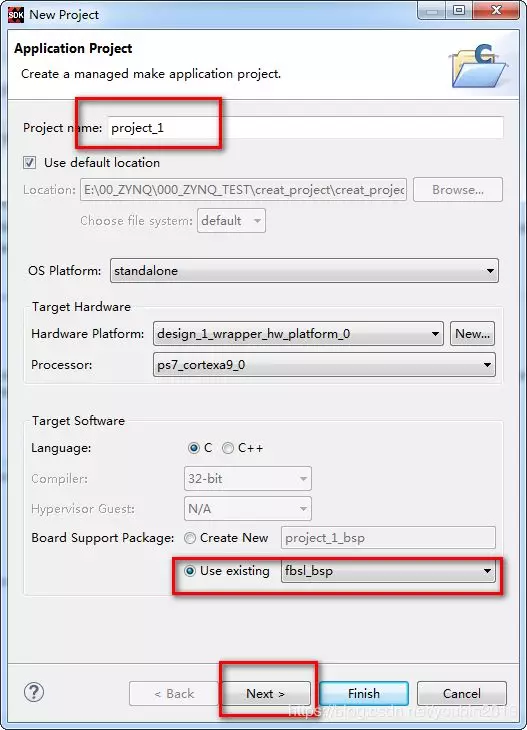

35,然后出現新建工程信息對話框,如圖所示,輸入工程名字,選擇工程路徑,一般使用默認路徑,選擇系統平臺standalone,選擇上述的硬件平臺design_1_wrapper_hw_platform_0,選擇操作核心0核(ps_cortexa9_0),確定開發語言為C語言,由于有了板級開發包了,所以這里使用之前創建的板級開發包,然后點擊下一步。

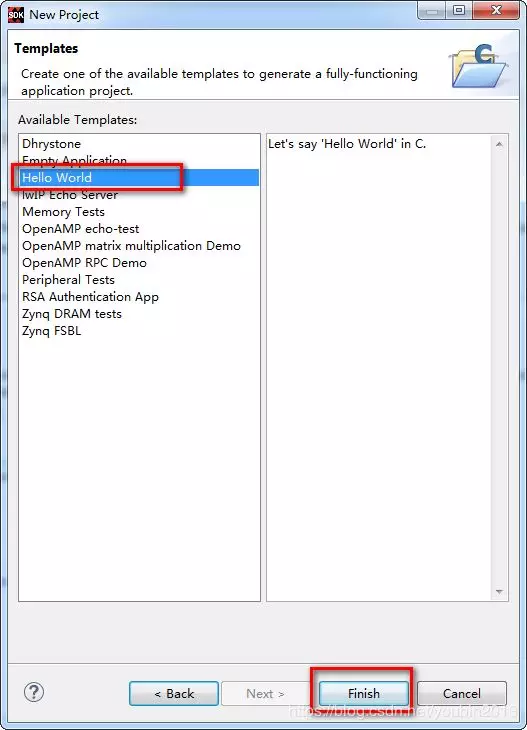

36,后續出現對話框如圖所示,選擇創建工程的模板類型,這里要創建一個helloworld模板應用程序,所以選擇helloworld類型模板,點擊finish,完成工程的新建。

使用調試

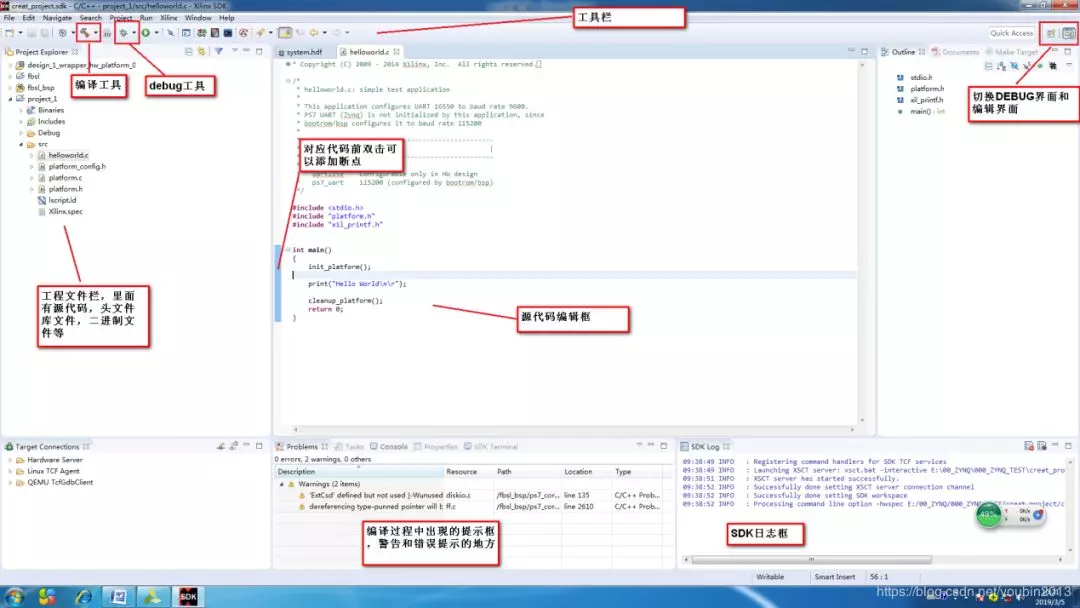

1,建立完工程以后需要進行在線調試程序,整個SDK中的界面分布如圖所示。

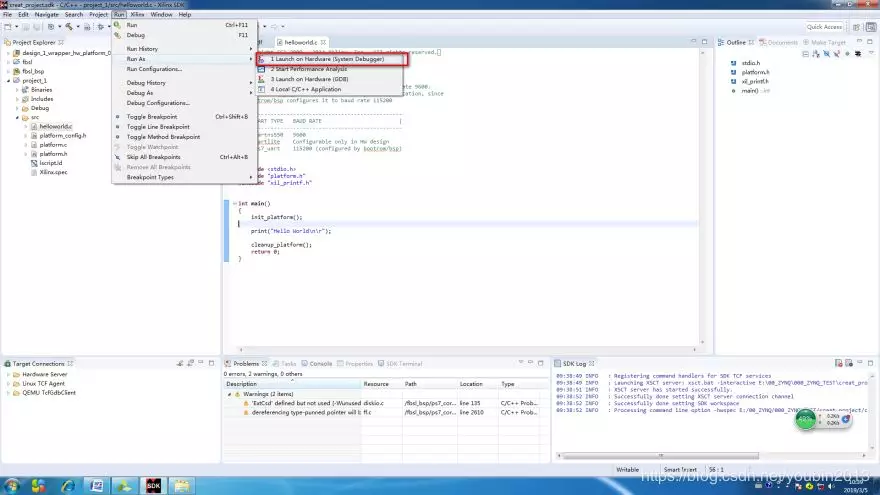

2,配置debug的一些相關設置,點擊菜單欄上的run,會出現下拉列表,如圖所示,在列表中會出現好多和debug相關的調試配置,有斷點的配置,有運行的配置,這里先選擇run as下的launch on hardware,選擇在創建的硬件平臺上運行程序。

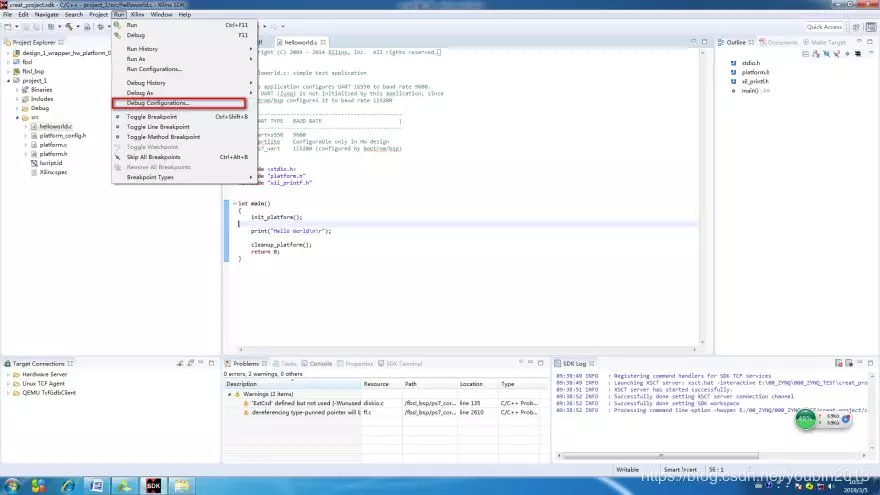

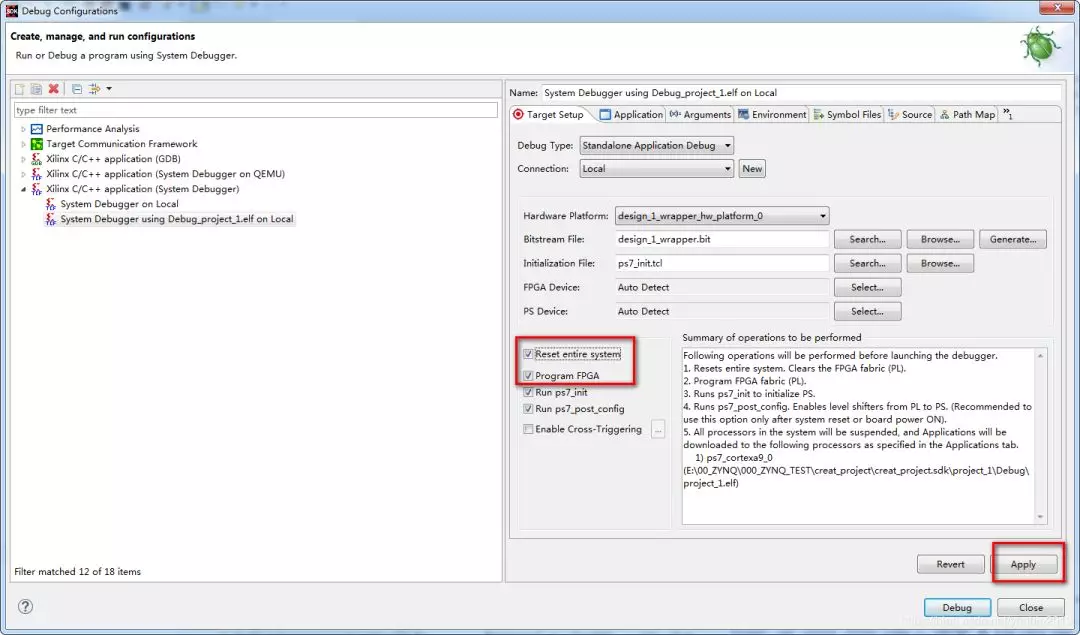

選擇debug configurations,配置一些debug相關的信息,如圖所示。主要是選擇上復位整個系統和下載FPGA程序的操作,在這兩個選項上打上勾,然后點擊應用,主要是在進入調試模式時復位系統,并且下載好fpga程序。

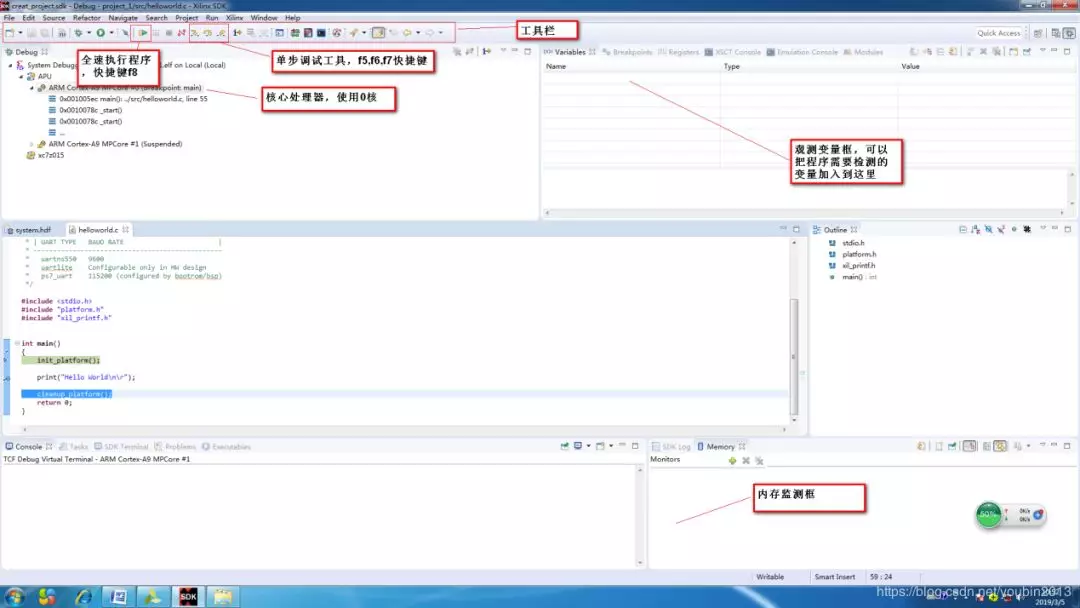

3,點擊小爬蟲以后進入debug的界面,如圖所示。其分布主要為:工具欄,核心選擇欄,程序源碼欄,變量監測欄,內存監測欄等,在圖中紅色框框中描述的功能是調試過程中經常用到的功能。

加載固化

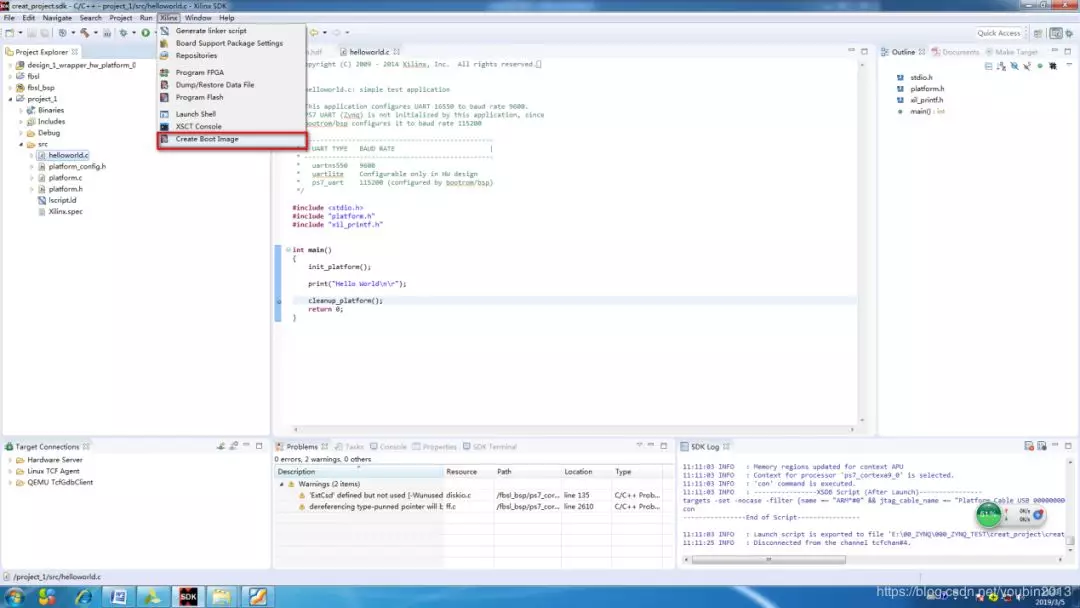

1,固化程序需要首先創建一個固化程序文件,然后將這個.bin文件下載到flash中;作為ZYNQ的固化程序,需要三個部分的程序,一部分為FBSL程序,該程序作為應用程序的bootloader;一部分為FPGA端的.bit文件,工程中的系統文件;還有一部分就是應用程序的文件了。使用SDK生成固化文件,選擇菜單 Xilinx ->Create Boot Image,如圖所示。

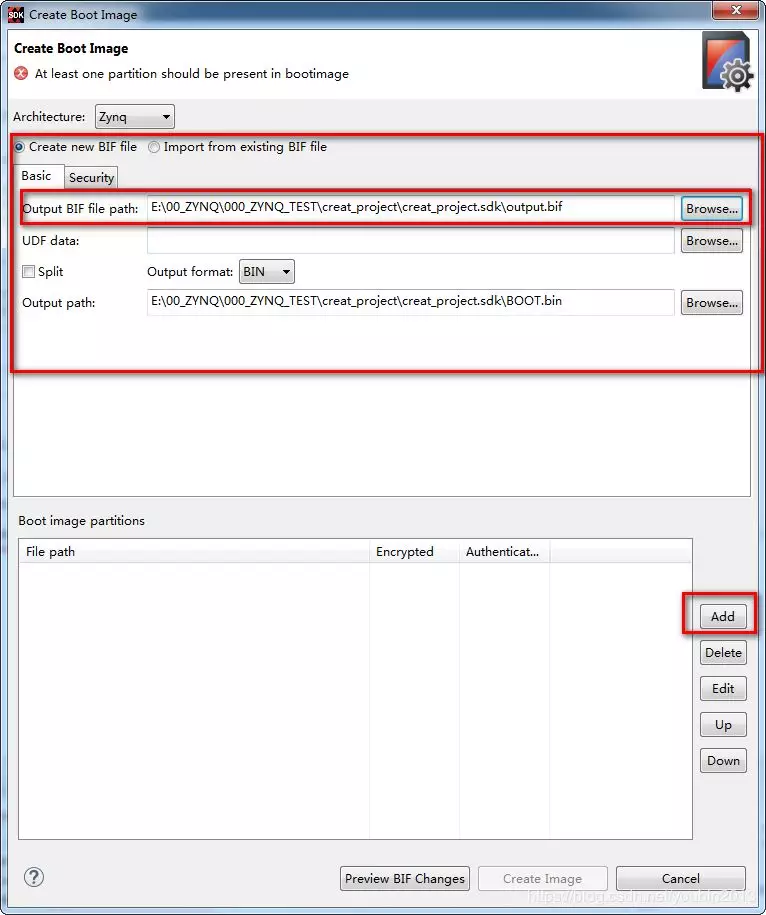

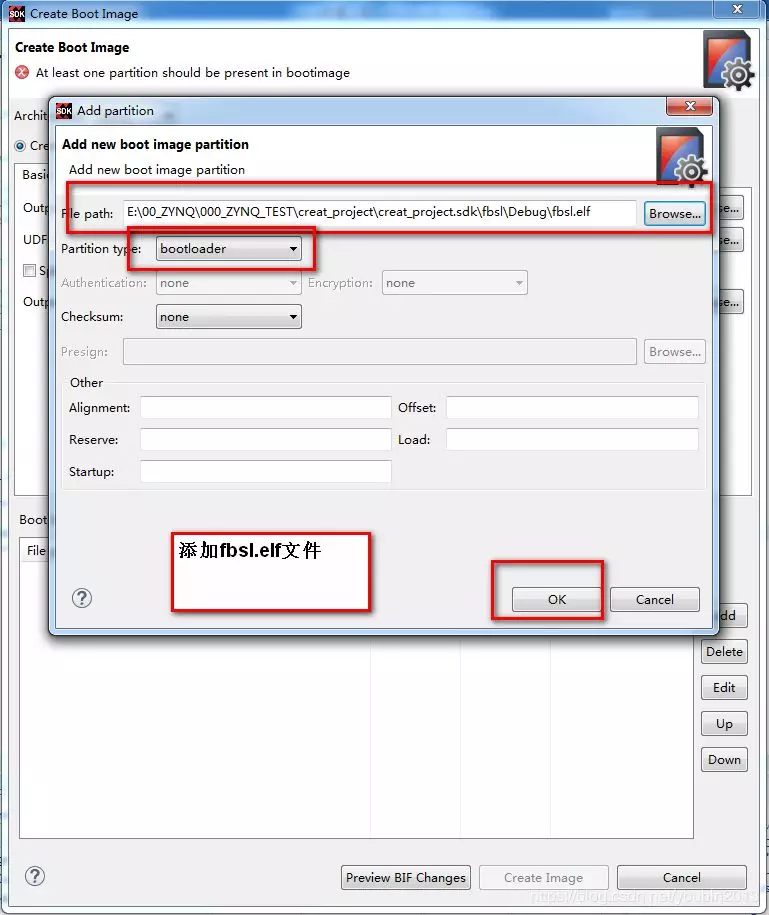

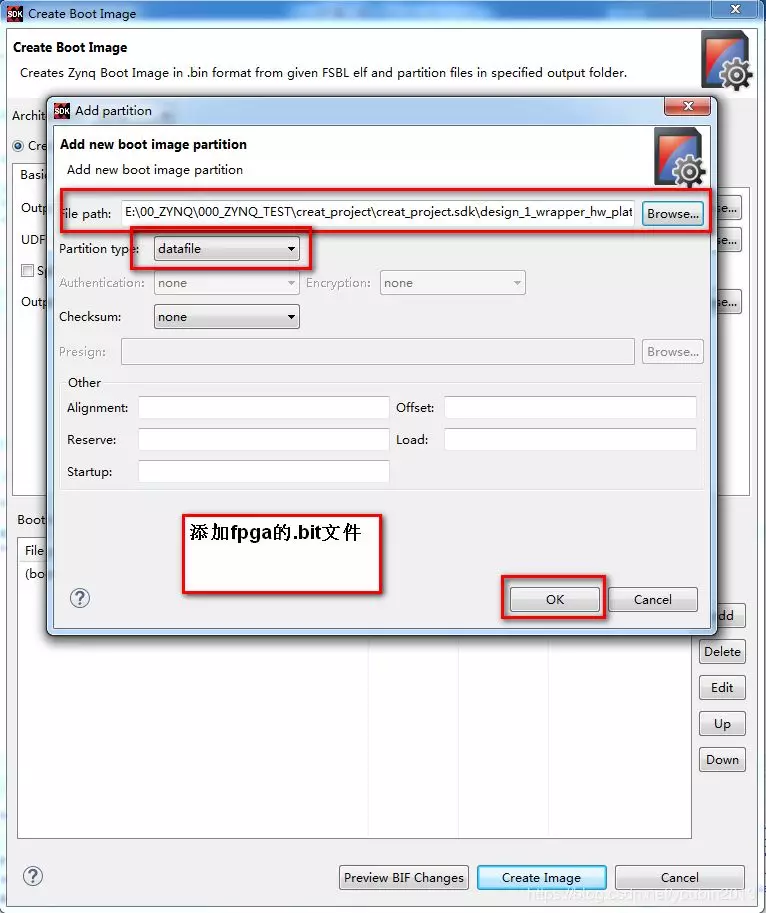

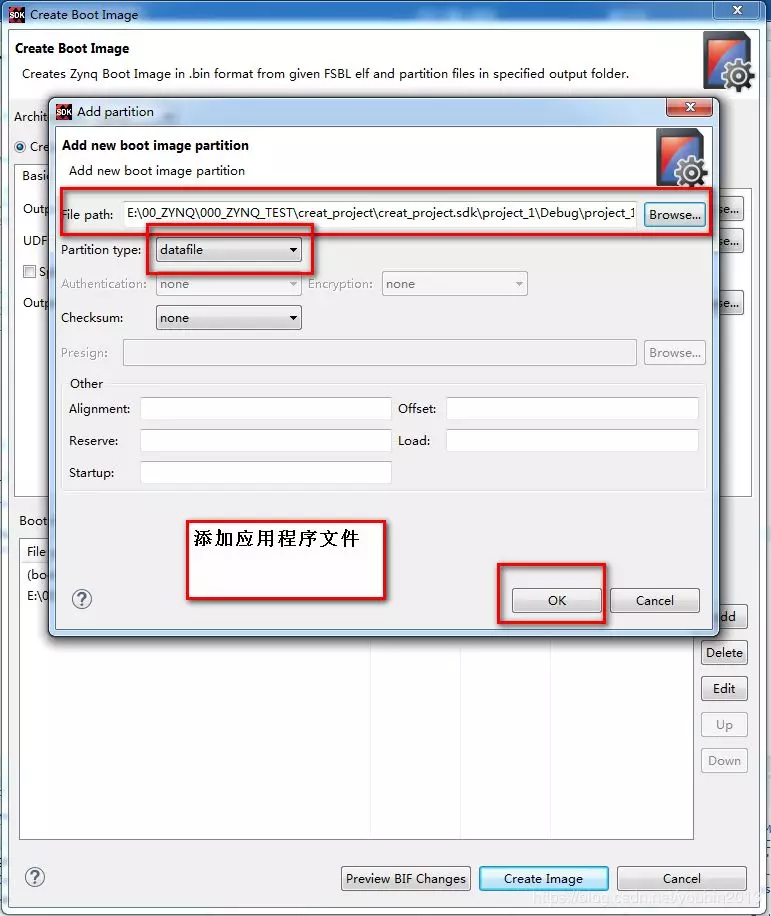

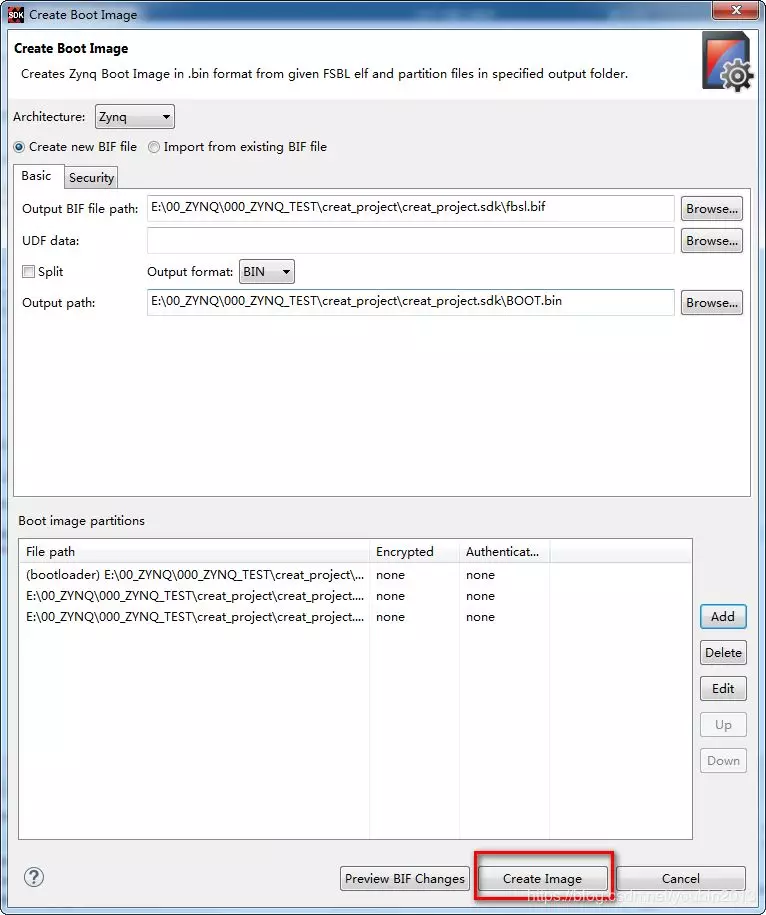

2,彈出對話框如圖所示,輸入生成固化程序的路徑,點擊output bif file path路徑中的browse瀏覽生成路徑,下面output path會和上述選擇路徑一樣,然后在下方的框框中點擊add,通過三次添加把fsbl程序文件,fpga端的.bit文件以及應用程序的.elf文件三個文件加入到boot image partion中,最后點擊create image創建出固化程序。

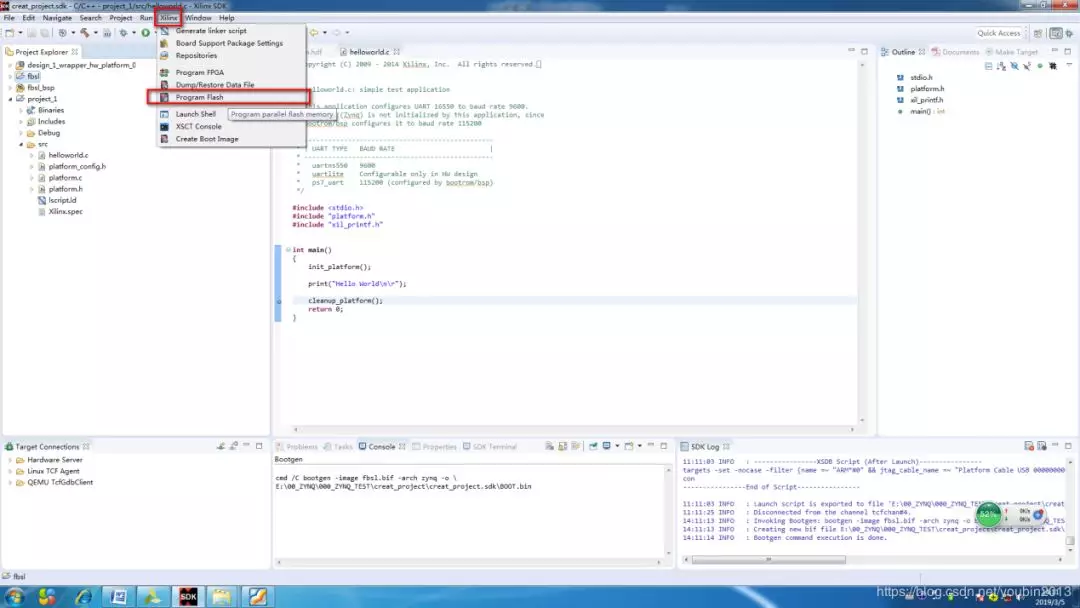

3,有了固化程序,還需要將程序下載到qflash中,需要用到SDK中的下載程序,在菜單欄中選擇Xilinx下拉列表中的Program Flash,然后彈出下載對話框,如圖所示。

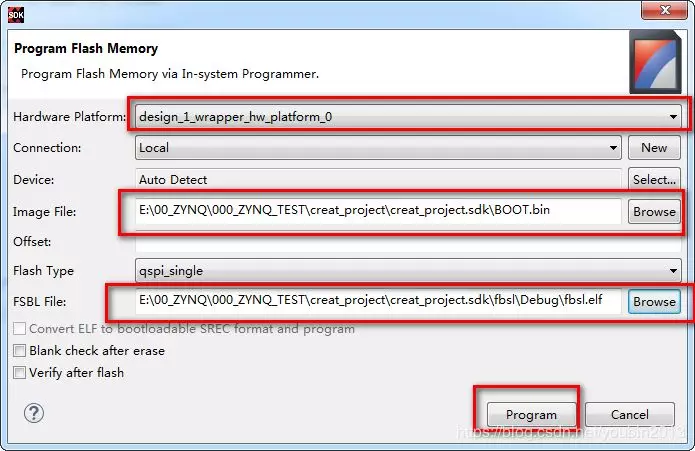

4,對話框如圖所示,需要選擇固化程序文件的路徑(Image File),還需要選擇能夠下載程序的FBSL.elf文件。

5,但是,使用的vivado版本為2017.4,在生成的FBSL.elf文件不能正常加載程序到qflash,在fbsl工程源碼中可以看到啟動方式為QFLASH,會對flash進行分區,無法正常下載,我們需要修改其啟動方式為JTAG模式,然后編譯,這樣子生成的FBSL.elf文件才能做加載使用。修改源碼如圖所示。

6,同時還需要添加環境變量到系統變量中,改變QSPI的時鐘為10MHz,如圖所示。右鍵點擊我的電腦,點擊屬性,彈出對話框,選擇高級系統設置;彈出對話框,點擊環境變量;彈出對話框,在系統變量那一欄點擊新建;彈出對話框,在變量名中輸入XIL_CSE_ZYNQ_UBOOT_QSPI_FREQ_HZ,變量值中輸入10000000,然后點擊確定。

7,修改上面內容后進行加載,有了固化程序,還需要將程序下載到qflash中,需要用到SDK中的下載程序,在菜單欄中選擇Xilinx下拉列表中的Program Flash,選擇固化程序文件的路徑(Image File)以及能夠下載程序的FBSL.elf文件(修改后重新編譯的fbsl.elf文件)。

注意:下載的fbsl.elf文件與生成固化程序的fbsl.elf文件是兩個不同的文件,為了以后不需要做修改,可以將上述修改后的fbsl.elf文件單獨放在一個路徑中,在下載flash程序的時候選擇這個路徑下的fbsl.elf文件就可以了。

編輯:hfy

-

Zynq

+關注

關注

9文章

608瀏覽量

47128

發布評論請先 登錄

相關推薦

玩轉Zynq連載27——導出PS硬件配置和新建SDK工程

玩轉Zynq連載28——[ex50] 第一個Zynq系統工程“Hello Zynq”

淺析在Windows系統中將RT-Thread移植到Zynq的步驟

如何創建一個DSP/BIOS程序

創建ZYNQ處理器設計和Logic Analyzer的使用

創建一個ZYNQ的工程和配置的詳細步驟

創建一個ZYNQ的工程和配置的詳細步驟

評論