時鐘篇

選用全局時鐘緩沖區(BUFG)作為時鐘輸入信號,BUFG是最穩定的時鐘輸入源,可以避免誤差。

只用一個時鐘沿來寄存數據,使用時鐘的兩個沿是不可靠的,如果時鐘沿“漂移”,就會導致時序錯誤。

不要隨意將內部信號作為時鐘,如門控時鐘和分頻時鐘,而要使用CLKDLL或者DCM產生的時鐘,或者可以通過建立時鐘使能或者DCM產生不同的時鐘信號。

FPGA盡量采取同步設計,也就是所有時鐘都是同一個源頭,如果使用兩個沒有相位關系的異步時鐘,必須要解決跨時鐘域問題。

性能篇

邏輯級的時延不要超過時序預算的百分之五十,否則會影響系統的運行頻率。可以通過分析時序報告中某個路徑的時序統計量來掌握系統的邏輯級時延。

對于關鍵的輸出選擇快速轉換速率,可以為LVCMOS和LVTTL電平選擇轉換速率來降低輸出時延。

如果設計允許增加延遲,可以對組合邏輯采用流水操作來提高性能。

利用四種全局約束來對設計進行全局約束,周期、偏置、輸入/輸出,管腳到管腳。

I/O寄存器提供了最快的時鐘到輸入、輸出到時鐘的延時,對于輸入、輸出信號,管腳到寄存器、寄存器到管腳都不可以有組合邏輯存在,對于三態寄存器,必須低電平有效,才能被綜合到IOB當中。

盡量使用IP核進行設計,因為IP核都是針對FPGA器件進行了優化,性能更高。

編程篇

使用Case語句而不是if-then-else語句

復雜的if-then-else語句在綜合布局布線以后會生成優先級譯碼邏輯,增加路徑上的時延。然而,case語句則綜合為并行邏輯,沒有時延。

有限狀態機盡量不要包含有算術邏輯、數據通路邏輯以及其它與狀態機不相關的組合邏輯;

狀態機編寫的時候,下一狀態邏輯和輸出譯碼邏輯必須放在獨立的進程中或者always語句中,綜合工具在輸出和下一狀態邏輯之間不允許共享資源。

盡量使用一位編碼有限狀態機;

使用不同風格的計數器,二進制計數器是非常慢的,可以考慮LFSR,Pre -scalar,Johnson.

代碼設計要按照功能塊劃分成不同的層次,層次化有助于設計更加容易讀懂,也容易調試和復用。

編輯:hfy

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601828

發布評論請先 登錄

相關推薦

FPGA時序約束之衍生時鐘約束和時鐘分組約束

基于lmk03806的高性能可編程時鐘發生器的設計與fpga實現 畢...

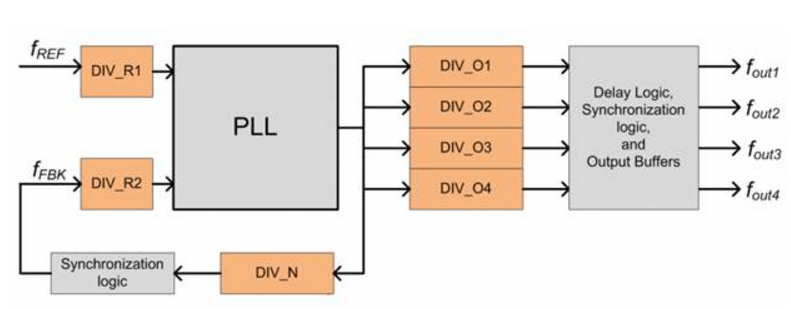

時鐘IC怎么滿足高性能時序需求?

基于FPGA的時鐘設計

(10)FPGA跨時鐘域處理

(12)FPGA時鐘設計原則

(29)FPGA原語設計(差分時鐘轉單端時鐘)

(30)FPGA原語設計(單端時鐘轉差分時鐘)

FPGA設計小技巧(時鐘/性能/編程)

FPGA設計小技巧(時鐘/性能/編程)

評論