對CMOS圖像傳感器采集圖像過程中的噪聲預處理問題,提出一種在FPGA中實現的可配置的自適應加權均值濾波模塊設計方案。該模塊通過檢測濾波窗口內不同方向的方差來確定紋理方向,從而自動生成相應的加權系數,可以對寬度不超過4 094像素的圖像進行流水線式的加權均值濾波處理,達到去噪保邊的目的。最后經過實驗驗證,當圖像寬度為2 048時,輸入輸出延時僅為42.04 μs,滿足實時性要求,且濾波后的圖像噪點明顯減少,紋理邊緣毛刺消失,能較好地改善圖像質量。

0 引言

CMOS圖像傳感器相較于傳統的CCD而言,具有更高的集成度,更靈活的圖像捕獲方式,更寬的動態范圍,加上其低成本、低功耗的特點,越來越受到人們的重視并得到廣泛的應用。但是CMOS圖像傳感器在采集圖像過程中由于暗電流和放大器偏差等原因導致其抗噪聲能力較差,引起圖像噪點增多,質量下降[1],這會直接影響圖像的后期處理工作。為方便圖像的后續處理,在圖像采集過程中,對圖像進行預處理是十分必要的。

1 降噪方法

高斯噪聲是數字圖像中最常見的噪聲[2],消除圖像高斯噪聲一般考慮使用均值濾波方法。傳統的鄰域均值濾波法對高斯噪聲可以起到抑制作用[2],但是會引起圖像邊緣部分細節的丟失。針對圖像噪聲與紋理邊緣的相似性,文獻[2]提出一種基于置信區間的自適應加權均值濾波方法。該方法利用高斯噪聲的正態分布特性,將灰度值處于置信區間內的像素點判斷為噪聲,能在濾除噪聲的同時,保證圖像邊緣不受影響。但該方法需要對噪聲圖像的灰度均值及噪聲的標準差預先進行估計,實時性較差。文獻[3]提出一種基于灰度值相似度和空間鄰近度的加權均值濾波算法,不僅考慮到濾波窗口中像素值的灰度值差異,也考慮到距離對中心像素點的影響,根據其兩個參數局部鄰域灰度因子和局部鄰域空間因子,生成加權系數。該方法相比于傳統的高斯濾波方法有更好的去噪效果,但運算量較大,處理速度較慢。

文獻[4]設計了一種基于極值點的加權均值濾波方法。該方法可以根據圖像的灰度值,自適應調整加權系數。通過4個方向上的方差計算,可以確定濾波窗口與紋理邊緣是否重合,并判斷出紋理的方向,據此生成不同的權重。這樣就可以達到較好的去噪保邊的效果。但如果使用上位機實現該算法,無法保證實時性。

通常上位機處理速度較慢,無法與圖像采集、傳輸與存儲系統形成一套流水線,而FPGA具有高速、并行、數據吞吐量大的特點,因此針對以上問題,提出一種基于FPGA實現的自適應加權均值濾波方法。該方法將文獻[4]提出優化算法映射到FPGA中,實現實時的圖像處理。

2 算法分析及其FPGA映射

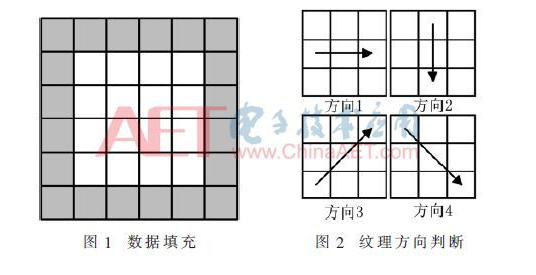

高斯噪聲是基于像素點的噪聲,因此考慮使用3×3的濾波窗口[5]。采用3×3的窗口對圖像進行均值濾波時,圖像第1行和第1列及最后1行和最后1列的像素點會由于數據不足而無法參與運算。為保證數據的完整性,可以采用填充法[6],在處理前先對圖像進行2×2的擴展。擴充后數據如圖1所示,白色部分為圖像原始數據,陰影部分為填充的數據。

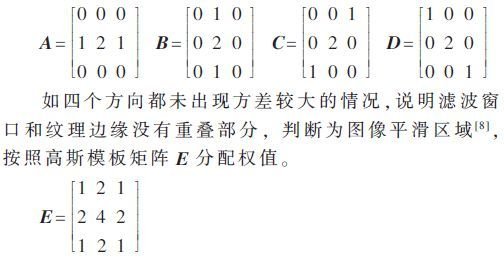

濾波模板生成,首先需要檢測窗口中心點是否為極值點,如果是則可能是噪聲點或紋理邊緣[7]。通過窗口4個方向上3個點方差計算確定該點是噪聲還是紋理邊緣,如圖2所示。如果濾波窗口與紋理邊緣重合,4個方向中與紋理邊緣有交叉的方向,由于灰度值跳變,會出現方差較大的情況。

而與紋理邊緣平行的方向上,灰度值不會出現大幅跳變,因此方差較小。根據4個方向的方差,確定紋理邊緣的方向,再確定其加權系數,在穿越圖像紋理邊緣的方向上,不做濾波處理。方向1到4上生成加權系數分別為A、B、C、D。

A=0 0 0

以上權重的模版矩陣都符合正態分布的規律,且矩陣所有元素的和為2的整數次冪,在后續的歸一化運算中,可以通過移位寄存器代替除法器實現,節省大量FPGA資源。

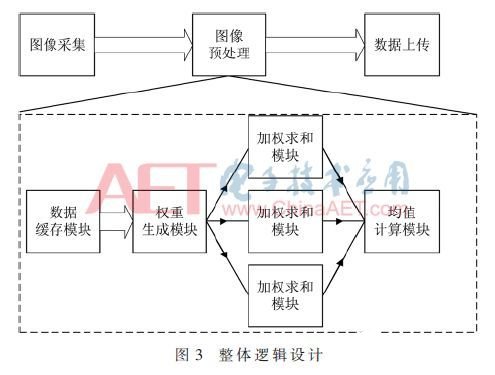

3 FPGA實現

本設計選用Xilinx FPGA XC6SLX45作為主控芯片,以模塊化設計理念為指導,設計了分辨率可配置的加權均值濾波模塊。該模塊由4個部分組成,包括數據緩存模塊、權重生成模塊、加權求和模塊以及求均值模塊,四個子模塊采用流水線的方式工作,保證數據能夠實時處理,整體邏輯設計如圖3所示。

3.1 數據緩存模塊設計

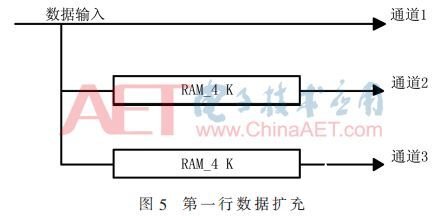

數據緩存模塊的功能是將1路12 bit數據流,經過緩存和時序調整調整為3路并行的12 bit數據流。該模塊使用兩個深度為4 K,寬度為12 bit的讀優先RAM,分別用來存儲一行有效圖像數據。根據行同步信號Hsync和場同步信號Vsync來判斷傳感器采集回的數據是否有效。

每當Hsync的一個上升沿到來時,鎖存輸入的數據,得到每行數據的第一個像素。經過計數后,再次鎖存每行數據的最后一個像素。輸入的數據延時一個時鐘,同時把鎖存的首位數據和末位數據與輸入數據組合,形成一路新的數據流,如圖4所示。由于RAM_4 K用于緩存一行擴充數據,因此圖像數據的寬度需要小于4 094,否則會造成數據丟失。

數據緩存模塊的一個關鍵信號是行計數信號,當一幀圖像數據到來即Vsync的一個上升沿到來時,行計數信號清零,每次Hsync的上升沿到來時,行計數加1。由于需要對數據進行擴充,因此第一行和最后一行數據做特殊處理。當第一行組合數據到來時,同時存儲進兩個RAM中,此時3個輸出通道無輸出。當第二行組合數據到來時,1通道輸出第二行數據,2通道和3通道輸出第一行數據,如圖5所示。

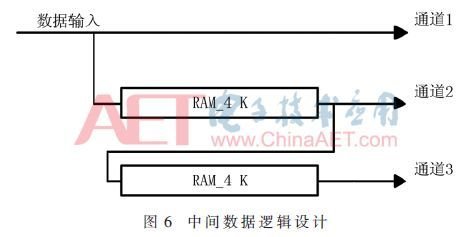

中間數據到來時,延時后輸入1通道,且作為RAM1的輸入。RAM1的輸出同時輸入至RAM2中。在數據輸入的同時,將上次存入RAM的數據讀出。這樣當第N行數據到來時,1通道輸出第N行數據,2通道輸出第N-1行數據,3通道輸出N-2行數據,即完成三行數據的同步輸出,邏輯圖如圖6所示。

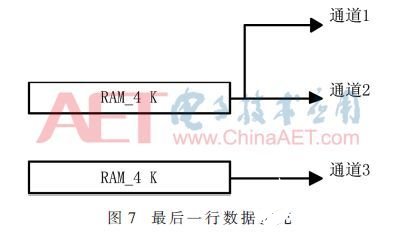

當最后一行數據輸入完成后,開始對其進行擴充。此時Data_in為無效輸入,并且RAM1輸出為最后一行數據,同時賦值給1通道和2通道,RAM2輸出倒數第二行數據,賦值給3通道,完成最后一行數據的擴充,如圖7所示。

經過RAM緩存后的數據輸出受RAM使能控制,由于RAM緩存的圖像數據是擴展后的數據,RAM的使能信號要在行同步信號的基礎上擴展兩個時鐘。三個通道的信號要經過適當的延時實現數據的同步。

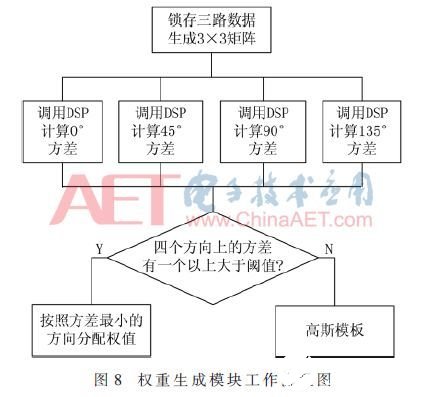

3.2 權重生成模塊設計

權重生成模塊的目的是檢測濾波窗口的中心像素點是平滑區域還是邊緣區域,并根據檢測結果生成相應的加權系數[6],其工作流程如圖8所示。

該模塊由加法器、減法器和乘法器構成,數據緩存模塊輸出的三行數據分別進行三次鎖存,得到窗口內9個像素點的灰度值Pix0~Pix8。其中Pix3~Pix5作為水平方向;Pix2、Pix4、Pix6作為45°方向;Pix1、Pix4、Pix7作為90°方向;Pix0、Pix4、Pix8作為135°方向,分別計算方差。求灰度和時,中心像素點Pix4權重為2,另外兩個點權重為1。這樣計算標準差時,只需將灰度和通過兩個移位寄存器即可。方差計算完成后,根據方差生成相應的權重模板及歸一化系數,作為后續處理的參數。為保證處理過程流水線化,此模塊通過四路并行計算方差,因此占用了較多DSP資源。

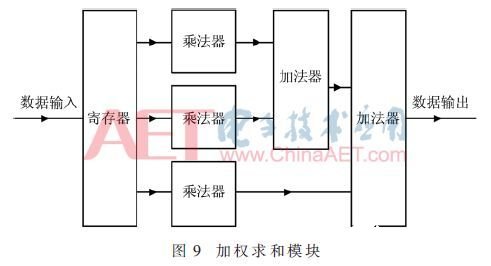

3.3 加權求和模塊設計

加權求和模塊的功能實現同一行的三個像素點的加權運算。該模塊由3個乘法器及兩個加法器組成,如圖9所示。一路數據輸入后,經過三次鎖存,得到同一行的3個相鄰像素點。同時輸入乘法器,進行加權運算,權重由權重生成模塊給出。運算完畢后把兩個乘法器的運算結果輸入加法器進行求和運算,再把得到的結果與另一個乘法器得到的結果輸入下一級加法器進行求和,得到同行3個像素點的加權求和輸出,如圖9所示。加權求和模塊共調用三次,完成三路數據的同步加權求和運算。

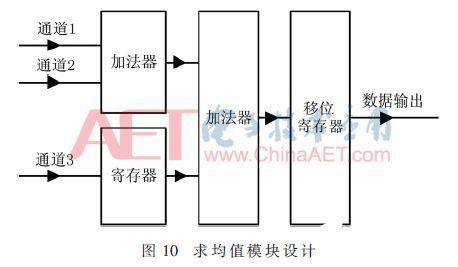

3.4 求均值模塊設計

求均值模塊調用了兩個加法器實現三路同步數據的求和運算。通過移位寄存器來計算輸出的均值。當歸一化系數分別為4和16時,加法器輸出數據經過2個或4個向右的移位寄存器輸出,如圖10所示。

12 bit數據經過乘法器、加法器的運算后,變成24 bit數據,但是有效數據位不變,只需取低12 bit即可。

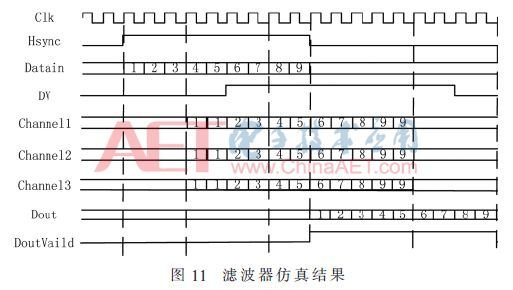

4 仿真及實驗結果分析

在ISE邏輯仿真時賦值給該模塊不同的圖像參數,驗證模塊的正確性和可配置性。以9×5分辨率的圖像為例:輸入圖像有效數據為1~9,數據緩存模塊輸出應為擴充后的并行3行數據,經過權重生成后,加權求和輸出,如圖11所示。

在仿真過程中,根據數據輸入與數據輸出的延遲判斷,在輸入圖像寬度為2 048像素情況下,處理延時為42.04 μs,滿足實時性要求。

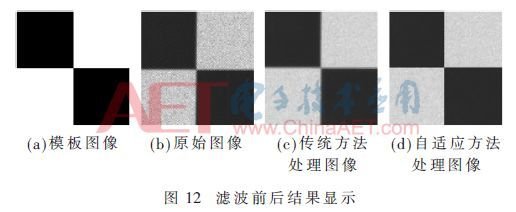

實驗對象選擇ON公司的CMOS圖像傳感器MT9P031,對采集到的2 048×1 944分辨率的圖像進行預處理。結果如圖12所示,其中圖12(a)為模板圖像,圖12(b)為采集回的原始圖像,圖12(c)為傳統加權均值濾波處理過的圖像,圖12(d)為本文方法處理后的圖像。可以看到未處理圖像的噪點較多,且紋理邊緣有毛刺;經過傳統加權均值濾波處理后,圖像的噪點減少,紋理邊緣毛刺消失,但比較模糊;使用本文方法處理后的圖像噪點較少,同時邊緣也更加清晰,圖像質量得到明顯改善。通過MATLAB對處理結果及原始圖像進行均方差MES與峰值信噪比PSNR計算比較,結果見表1。

從表1中圖像的客觀指標可以看到,通過本文方法處理后的圖像相較于傳統加權均值濾波處理后的圖像,其峰值信噪比提高1.04 dB。說明本文方法優于傳統的加權均值濾波方法。

FPGA資源占用率見表2。由表2數據可知,除DSP資源外,本設計的資源占用率低,而一般圖像采集系統對DSP需求不高,因此可以方便嵌入CMOS圖像采集系統設計中。

5 結論

針對傳統均值濾波處理圖像時實時性差等特點,結合FPGA并行處理數據的高效性,實現圖像的自適應加權均值濾波處理,具有可配置、低延時的特點。實驗結果表明,本設計能夠在不影響數據傳輸速度的情況下,嵌入圖像采集系統中,形成一套流水線,并有效提高CMOS圖像傳感器采集圖像的質量。

參考文獻

[1] 徐琳亮.CMOS圖像傳感器預處理數字電路的設計與實現[D].成都:電子科技大學,2017.

[2] 陳家益,黃楠,熊剛強,等.基于置信區間的自適應加權均值濾波算法[J].南京理工大學學報,2017,41(3):307-312.

[3] 張文娟,康家銀.一種用于圖像降噪的自適應均值濾波算法[J].小型微型計算機系統,2011,32(12):2495-2498.

[4] 楊樊,韓艷麗.一種基于極值的自適應均值濾波算法[J].紅外與激光工程,2006(S4):116-120.

[5] 彭宏,趙鵬博.邊緣檢測中的改進型均值濾波算法[J].計算機工程,2017,43(10):172-178.

[6] 張文娟,康家銀.一種用于圖像降噪的自適應均值濾波算法[J].小型微型計算機系統,2011,32(12):2495-2498.

[7] 郭貝貝,易三莉,賀建峰,等.改進的非局部均值濾波算法[J].計算機工程,2016,42(7):227-231.

[8] 李佐勇,湯可宗,胡錦美,等.椒鹽圖像的方向加權均值濾波算法[J].中國圖象圖形學報,2013,18(11):1407-1415.

作者信息:

武昊男,儲成群,任勇峰,焦新泉

(中北大學 電子測試技術國家重點實驗室,山西 太原030051)

-

FPGA

+關注

關注

1626文章

21669瀏覽量

601869 -

寄存器

+關注

關注

31文章

5318瀏覽量

120015 -

圖像處理

+關注

關注

27文章

1282瀏覽量

56646 -

CMOS圖像傳感器

+關注

關注

10文章

215瀏覽量

27652

發布評論請先 登錄

相關推薦

EasyGo實時仿真丨PCS儲能變流器控制仿真應用

EasyGo實時仿真丨PCS儲能變流器控制仿真應用

EasyGo 實時仿真 NetBox 操作指南

EasyGo實時仿真丨三相永磁同步電機開環實驗仿真應用

基于FPGA的實時邊緣檢測系統設計,Sobel圖像邊緣檢測,FPGA圖像處理

FPGA設計中 Verilog HDL實現基本的圖像濾波處理仿真

多端口能量路由實時控制仿真系統解決方案

電力電子實時仿真實驗室,助力高等教育信息化建設

基于FPGA的實時圖像處理仿真實驗方案實現

基于FPGA的實時圖像處理仿真實驗方案實現

評論