1 概述

I2S(Inter—IC Sound)總線, 又稱 集成電路內置音頻總線,是飛利浦公司為數字音頻設備之間的音頻數據傳輸而制定的一種總線標準,該總線專門用于音頻設備之間的數據傳輸,廣泛應用于各種多媒體系統。I2S采用了沿獨立的導線傳輸時鐘與數據信號的設計,通過將數據和時鐘信號分離,避免了因時差誘發的失真,為用戶節省了購買抵抗音頻抖動的專業設備的費用。

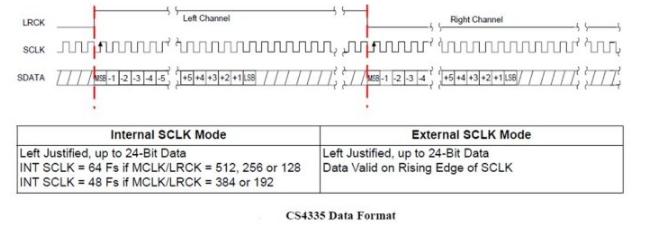

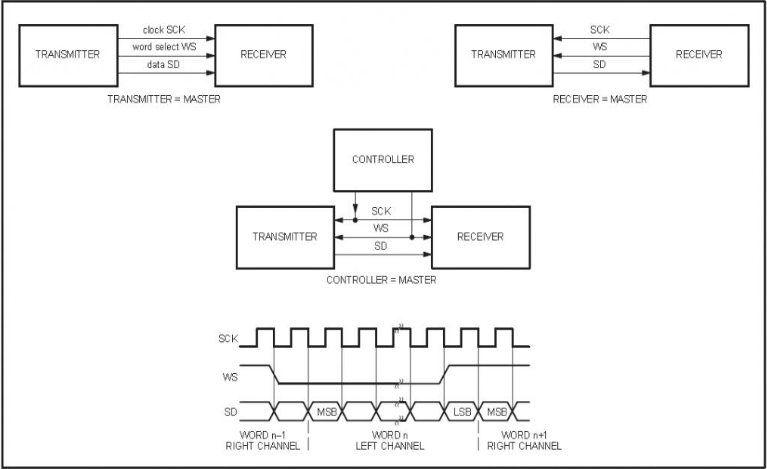

在飛利浦公司的I2S標準中,I2S主要有三個信號。

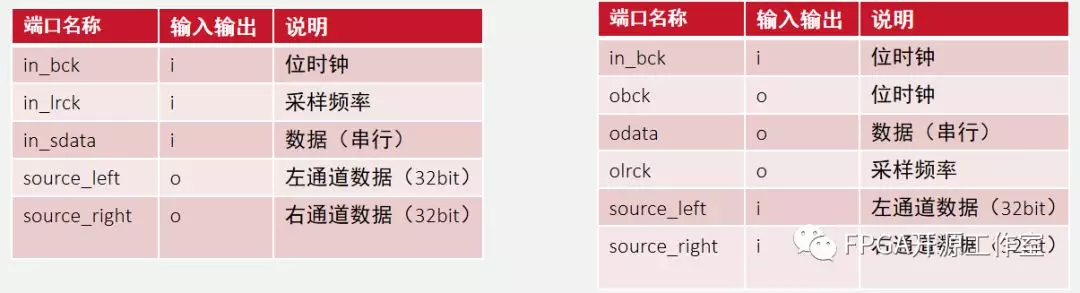

1.位時鐘 BICK(也叫串行時鐘SCLK),即對應數字音頻的每一位數據,BCLK都有1個脈沖。BCLK的頻率=2×采樣頻率×采樣位數。

2.幀時鐘LRCK,(也稱WS),用于切換左右聲道的數據。LRCK為“1”表示正在傳輸的是右聲道的數據,為“0”則表示正在傳輸的是左聲道的數據。LRCK的頻率等于采樣頻率。

3.串行數據SDATA,就是用二進制補碼表示的音頻數據。

有時為了使系統間能夠更好地同步,還需要另外傳輸一個信號MCLK,稱為主時鐘,也叫系統時鐘(Sys Clock),是采樣頻率的256倍或384倍。隨著技術的發展,在統一的 I2S接口下,出現了多種不同的數據格式。根據SDATA數據相對于LRCK和SCLK的位置不同,分為左對齊(較少使用)、I2S格式(即飛利浦規定的格式)和右對齊(也叫日本格式、普通格式)。

以下是I2S Sample rate 44.1Khz 和48Khz部分系列。

2 模式

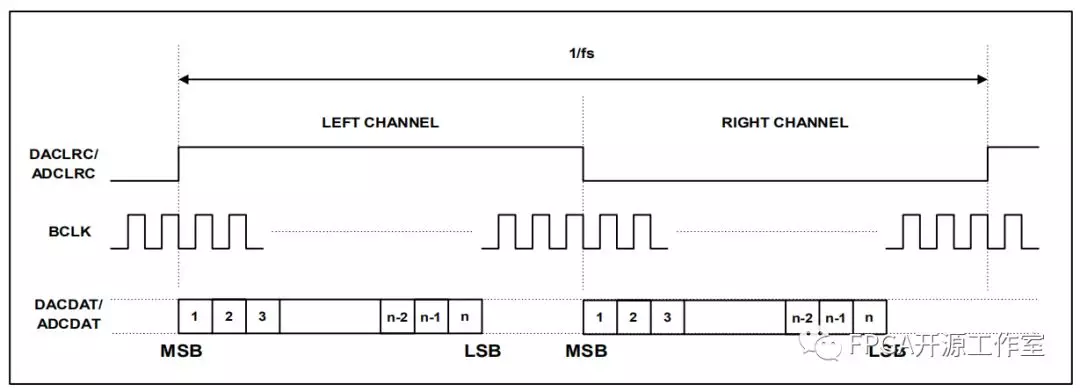

左對齊模式:SDATA 的MSB在BCLK的第一個上升獲得根據LRCK的傳輸。

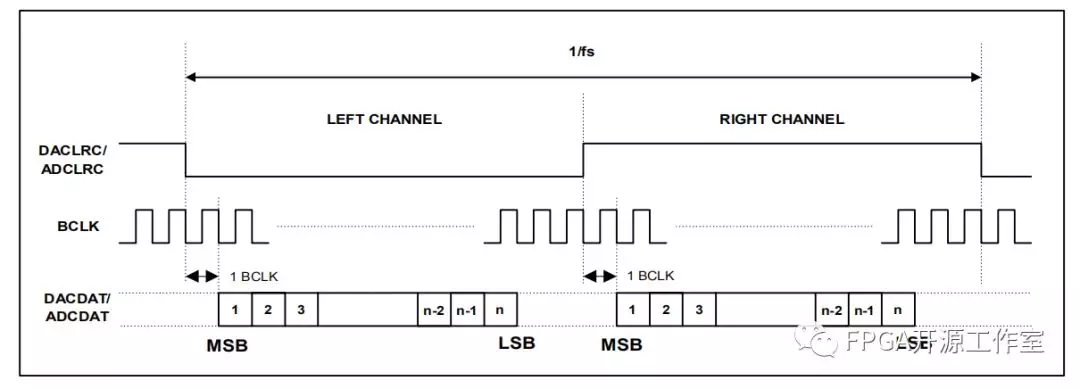

I2S模式:SDATA 的MSB在BCLK的第二個上升獲得根據LRCK的傳輸。

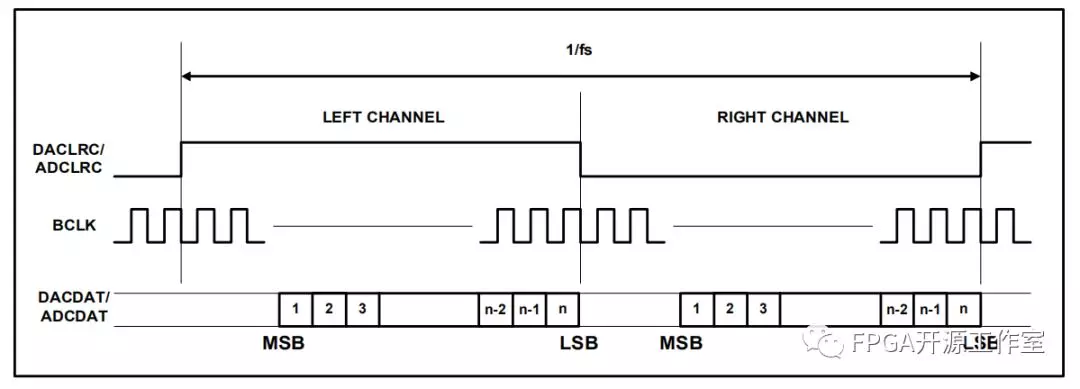

右對齊模式。

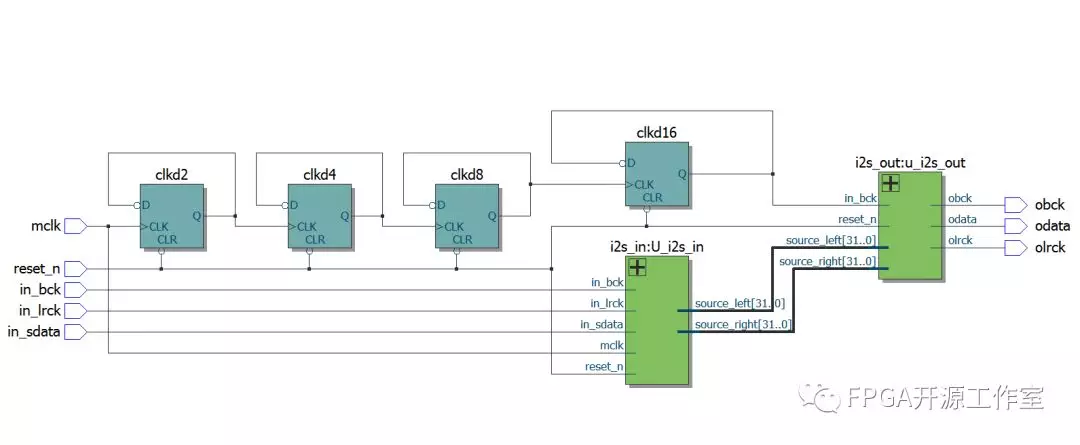

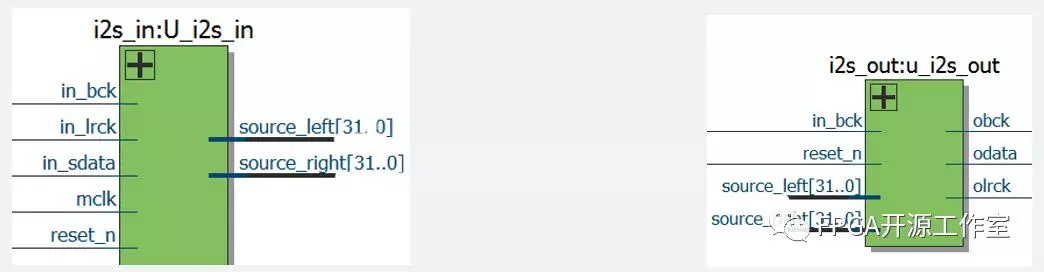

i2s_test模塊為i2s_in和i2s_out模塊的頂層,i2s_in模塊將輸入的串行數據轉換成并行的數據,然后i2s_out模塊將并行數據轉換成串行數據輸出。

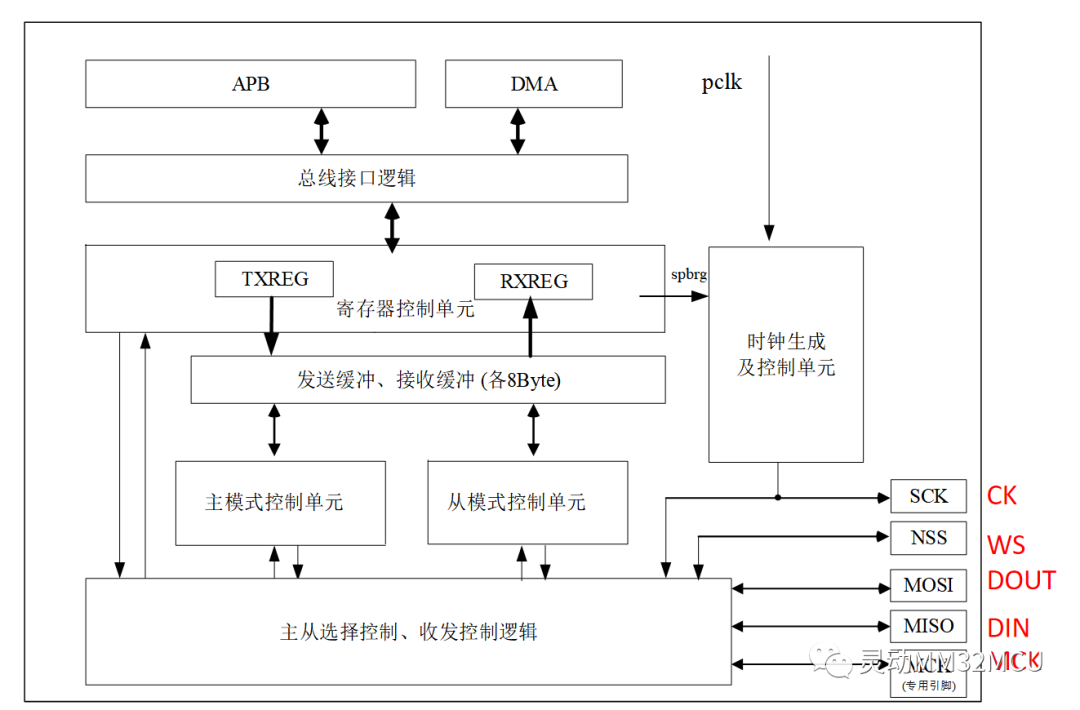

I2s_in模塊和I2s_out模塊的接口說明如下。

I2s test bench設計

讓i2s_out模塊將并行轉為串行,然后使用i2s_in模塊將串行轉為并行。驗證數據是否正確。

Test bench源碼:

1. // test bench

2.

3. `timescale 1ps/1ps

4.

5. module tb32bitmaster();

6.

7. initial begin #600000000 $finish; end //600us

8.

9. reg preset_n;

10. initial begin preset_n = 1; #10000 preset_n = 0; #100000 preset_n = 1; end

11.

12. reg pclk;

13. initial begin pclk = 0; #313333 pclk = 0; forever #11072.1 pclk = ~pclk; end

14.

15. reg start;

16. initial begin start = 0; #400000 start = 1; end

17.

18. reg clkd2, clkd4, clkd8, clkd16;

19. wire reset_n = preset_n;

20.

21. always @(posedge pclk or negedge reset_n)

22. if (0 == reset_n)

23. clkd2

24. else

25. clkd2

26.

27. always @(posedge clkd2 or negedge reset_n)

28. if (0 == reset_n)

29. clkd4

30. else

31. clkd4

32.

33. always @(posedge clkd4 or negedge reset_n)

34. if (0 == reset_n)

35. clkd8

36. else

37. clkd8

38. always @(posedge clkd8 or negedge reset_n)

39. if (0 == reset_n)

40. clkd16

41. else

42. clkd16

43.

44.

45. wire bck, lrck, sdata;

46. wire [31:0] y0, y1;

47.

48. i2s_in U_i2s_in(

49. .mclk(pclk),

50. .reset_n(reset_n),

51.

52. .in_bck(bck),

53. .in_lrck(lrck),

54. .in_sdata(sdata),

55. //controls

56. //output

57. .source_left(y0),

58. .source_right(y1)

59. );

60.

61. i2s_out u_i2s_out(

62. .in_bck(clkd16),

63. .reset_n(reset_n),

64. .source_left(32'h5555_aaaa),

65. .source_right(32'haaaa_5555),

66. .obck(bck),

67. .olrck(lrck),

68. .odata(sdata)

69. );

70. endmodule

71.

72. `include "i2s_out.v"

73. `include "i2s_in.v"

從仿真結果看我們的i2s_out和i2s_in模塊仿真設計成功。

編輯:hfy

-

FPGA

+關注

關注

1620文章

21510瀏覽量

598956 -

I2S

+關注

關注

1文章

59瀏覽量

41658

發布評論請先 登錄

相關推薦

全面解析I2S、TDM、PCM音頻總線

音頻接口I2S實驗

基于FPGA和AD1836的I2S接口設計

I2S設備和MSP430器件的連接指南

i2s音頻總線學習

幾種常見的I2S數據格式

音頻總線I2S協議:I2S收發模塊FPGA的仿真設計

音頻總線I2S協議:I2S收發模塊FPGA的仿真設計

評論