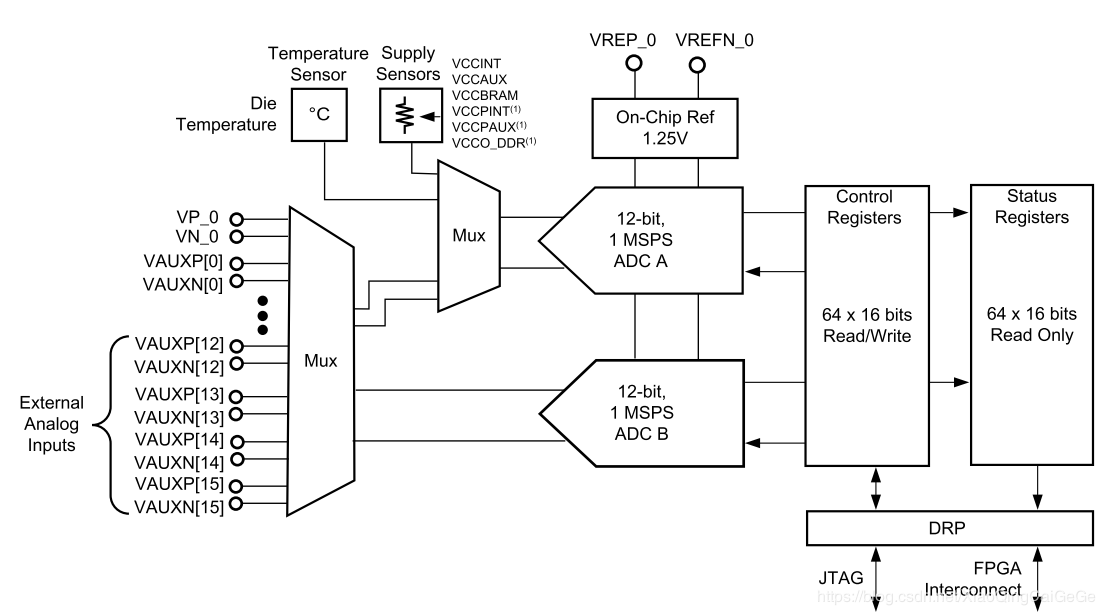

Xilinx 7系列FPGA全系內置了一個ADC,稱呼為XADC。

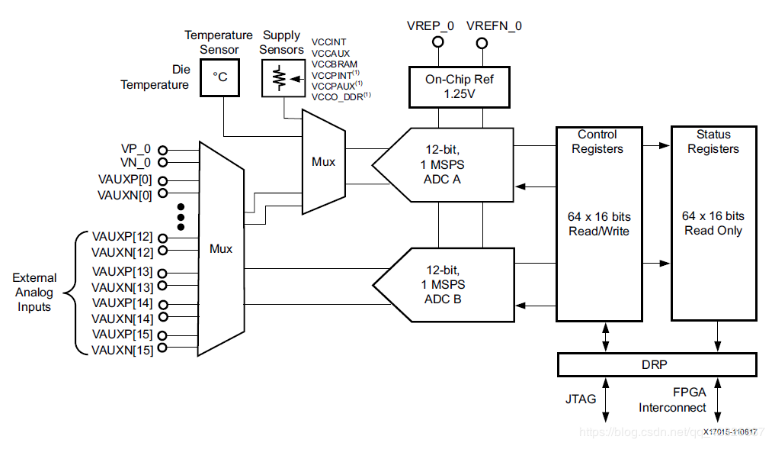

這個XADC,內部是兩個1mbps的ADC,可以采集模擬信號轉為數字信號送給FPGA內部使用。

XADC內部可以直接獲取芯片結溫和FPGA的若干供電電壓(7系列不包括VCCO),用于監控FPGA內部狀況。同時提供了17對差分管腳,其中一對專用的模擬差分輸入,16對復用的模擬差分輸入,不使用的時候可以作為普通的User I/O。

關于XADC具體的結構,功能和各個參數的含義,請參考相關文檔。這里不做詳細描述。另外有兩點需要注意。

1.關于參考電壓的設置,會影響誤差范圍及采樣值的計算公式。

2.模擬差分輸入對模擬信號幅值有要求,需要外邊模擬電路進行一定程度的轉換。

更多關于參考電壓和外部模擬電路的實現,請參考設計文檔UG480:http://link.zhihu.com/?target=https%3A//www.xilinx.com/support/documenta...

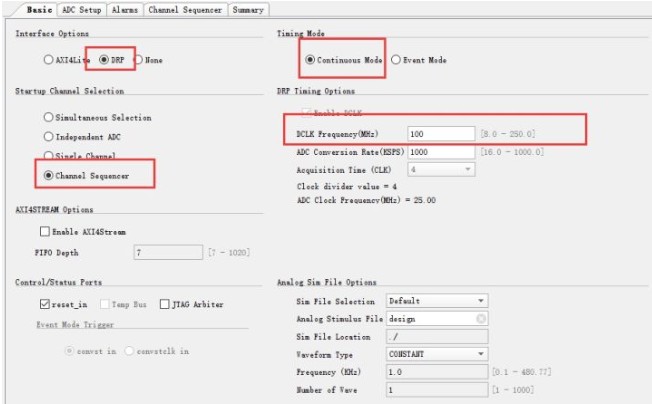

假設現在需要用XADC來獲取幾個模擬信號的信息,那么應該如何操作呢。下面解釋一種個人偏愛設置方式。

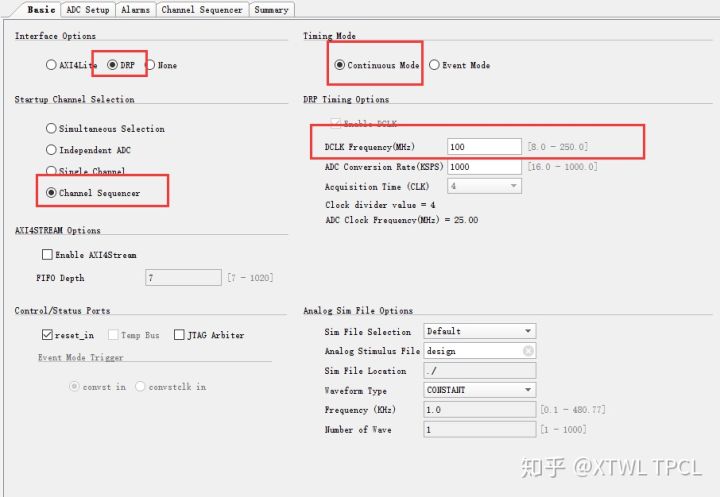

注意紅框中的幾點:

1.使用DRP端口獲取數字信號,這樣控制似乎更簡單一些。

2.使用連續采樣模式,ADC一直工作在數據采集模式,采集后就可以進行輸出。

3.使用Channel Sequencer模式,由于只有兩個XADC而需要采樣的數據過多,所以讓XADC依次陸續進行采樣。

4.設置好DRP端口的時鐘頻率。

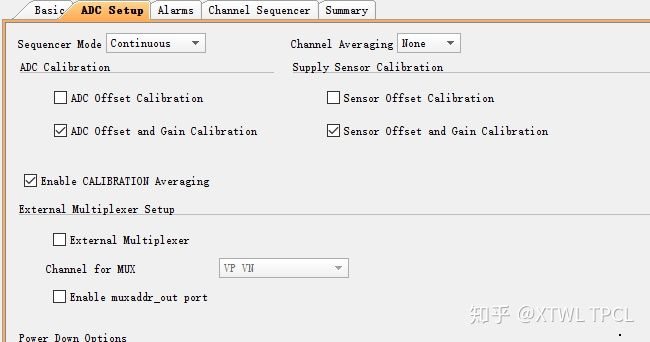

IP設置第二頁,主要是設置Calibration、平均值和外部MUX。這幾個可以暫時跳過,等熟悉XADC的使用后在進行深入了解。

第三頁設置告警參數,可以不用。如果需要的話,可以設置一下,便于使用。

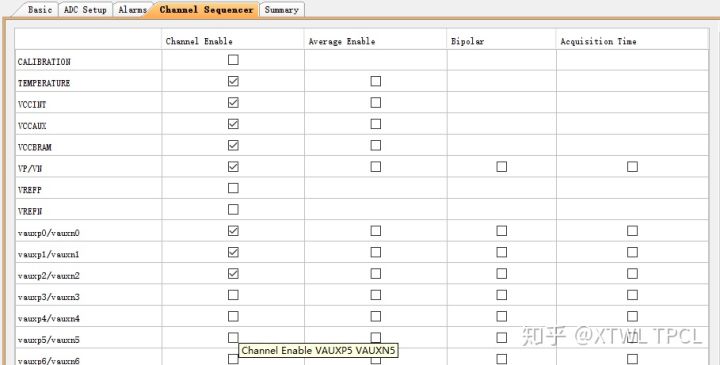

第四頁設置需要使用的通道,這里選擇溫度和三個供電電壓,并選擇一個專用的模擬輸入通道和前三個復用的模擬輸入通道。

最后一頁是Summary,可以看看設置是否有問題,沒有需要設置的地方。

這個時候最基本的一個多通道獲取數據的XADC設置好了,至于設置中沒有細說的地方,可以等熟練使用之后進行研究,找出最合適的使用模式。

下面是如何使用這個生成的IP。由于使用DRP端口來讀取數據,所以需要設計一個DRP讀寫控制器。不過由于XADC本身就提供了一些信號,所以這個設計其實非常簡單。

.di_in(di_in),

.daddr_in(daddr_in),

.den_in(den_in),

.dwe_in(dwe_in),

.drdy_out(drdy_out),

.do_out(do_out),

.dclk_in(dclk_in),

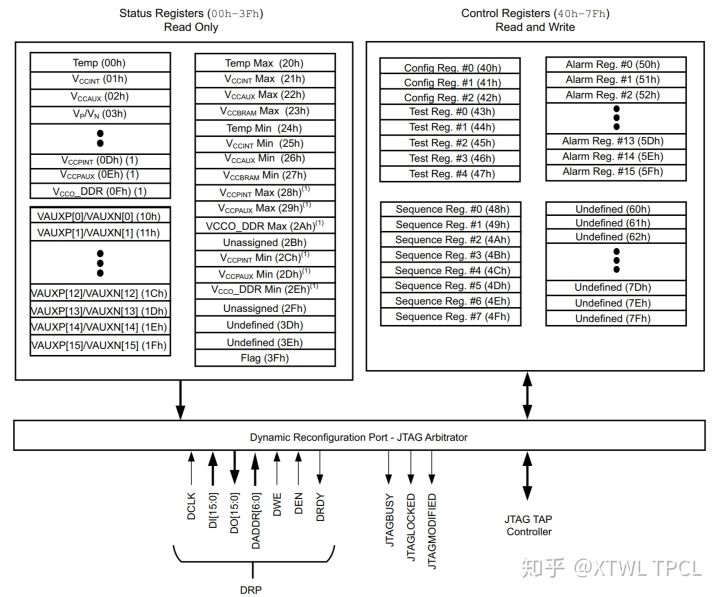

首先理一下DRP端口,主要7個信號。由于僅僅是讀取數據,所以輸入部分沒有使用的必要。

.di_in (16'b0),

.dwe_in (1'b0),

時鐘信號連接DRP所使用的時鐘即可,注意頻率需要和XADC IP中的設置一樣。

.daddr_in ({2'b00,CHANNEL_OUT}),

.den_in (EOC_OUT),

.do_out (DO_OUT),

.drdy_out (DRDY_OUT),

.eoc_out (EOC_OUT),

.channel_out (CHANNEL_OUT),

余下四個DRP端口,兩個輸出兩個輸入。兩個輸出直接引出來,其中do_out就是最終需要的數據。這個端口是16bit,取高12bit即可(對應XADC中宣稱的12位)。

XADC的IP端口中還有兩個,名為eoc_out和channel_out。將eoc_out連接到DRP端口的den_in端口,含義是當多路采樣的某一路完成采樣后,則啟動DRP端口操作,開始進行讀取數據。將channel_out補兩位之后送入daddr_in作為DRP端口操作的地址信號。這樣就完成了DRP的讀寫操作。

不過這樣輸出的數據,會周期性的在幾個端口數據之間變化。所以通常在后端加一個過濾設置,具體行為是,當代表DRP操作完成的drdy_out拉高的時候,根據channel_out的值來判斷是哪一個通道的。

always @(posedge clk)begin

if(DRDY_OUT == 1'b1 && CHANNEL_OUT ==5'd0)begin

Temperature end else begin

Temperature end

end

關于每個采樣通道的具體地址,可以參考手冊

至于模擬差分輸入Pin,直接送到頂層的相對應管腳即可。注意Vivado工具可能需要對復用的模擬Pin進行電平約束,根據VCCO的電壓值選擇相應的lvcmos即可,例如1.8V的VCCO就選擇lvcmos18即可。

這樣就可以獲取對應的模擬采樣數據了。由于絕大部分情況下需要檢測的模擬信號變化相對較慢,使用XADC是足夠用于檢測的。

涉及到XADC的使用問題還有MIG IP。MIG是Memory Interface的IP,也就是DDR3之類的DDR存儲器IP。由于此類接口一般速率過高,會需要溫度信息對接口做一定的矯正。在MIG IP的配置中,會默認啟動XADC。

此時的XADC僅僅需要提供溫度信息就可以了。當需要提供更多信息,就需要獨立配置XADC,這樣工程中就會生成兩個XADC;或者例化了兩個MIG IP,這樣各自就會需要一個XADC。由于硬件中只有一個XADC模塊,當發現工程中需要多個XADC模塊的時候,工具就會提示出錯。

解決方案也非常簡單,MIG IP中去掉XADC。然后在設計中獨立例化XADC IP。根據上文的做法獲取溫度信息后送往MIG。MIG IP去掉XADC后會生成一個溫度端口用來接收數據。這樣就不會發生沖突。

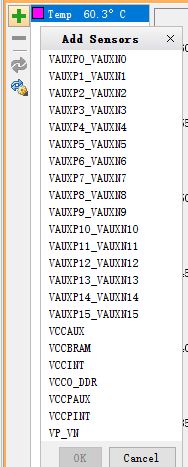

另外一個非常便捷的獲取溫度信息的方案就是使用Hardware Manager。在Hardware Manager中打開XADC就能看到溫度信息。

其實XADC所有通道數據都可以通過這個方法獲取。

更多的使用細節,可以參考UG480文檔。

編輯:hfy

-

FPGA

+關注

關注

1626文章

21678瀏覽量

602006 -

Xilinx

+關注

關注

71文章

2164瀏覽量

121038 -

模擬信號

+關注

關注

8文章

1120瀏覽量

52407

發布評論請先 登錄

相關推薦

xilinx FPGA的XADC怎么用?

基于FPGA的模擬信號源系統設計

Xilinx-ZYNQ7000:如何用XADC測外部溫度值

Xilinx 7系列FPGA內置ADC XADC獲取模擬信號

Xilinx 7FPGA XADC如何獲取模擬信號的信息

Xilinx 7FPGA XADC如何獲取模擬信號的信息

評論