有時,在區分為“慢”或“快”信號之間的區分似乎是任意的,并且可能取決于您詢問的人。一個相關的主題是PCB走線在電氣上是“短”還是“長”,您可能會在該主題上發現同樣多的分歧。無論您需要在PCB中路由慢速信號還是快速信號,您的走線都需要遵循一些PCB布線規則,以確保您的電路板按預期工作。

開始在組件之間路由信號之前,您需要查看您的設計規則,并將其調整為符合信號標準。在開始圍繞PCB布線信號之前,需要設置以下重要的PCB布線規則。

單端信號的PCB布線規則

關于PCB布線規則,最需要注意的一點是,布線標準不一定將自己定義為“低速”或“高速”。這種區別在很大程度上是由PCB設計人員創建和延續的,并且很大程度上是由于信號上升時間變得非常快(小于1 ns)時出現的信號完整性問題而引起的。因此,在設置設計規則時,了解信號標準中的約束更為重要,無論您要處理慢還是快的信號速度。

查找所需設計規則的第一個地方是信令標準的文檔。大多數標準的文檔可在線免費獲得。隨著創建更多設計,您將更加熟悉這些標準,并且知道在設計中設置哪些規則。適用于單端信號許多標準的一些最常見的PCB布線規則是:

匹配的長度。對于總線標準或帶有源同步時鐘的并行數據路由,您需要在一定容差范圍內對一組中的所有網絡強制執行長度匹配。在路由時,這是通過向網絡添加長度調整結構來完成的。

通過過渡。一些標準建議限制通孔過渡的數量,以防止過多的損耗,反射和其他寄生效應。

最大長度。有時會為給定的損耗正切值指定網的最大長度,以防止信號過度衰減。如果您使用的是低損耗層壓板,則可以根據損耗角正切值的差異來延長長度。

間隙。跡線需要與不屬于網絡的其他對象(焊盤,組件,平面等)保持分開。這樣可確保可制造性,減少不必要的寄生現象,并在高壓設計中提供ESD保護。

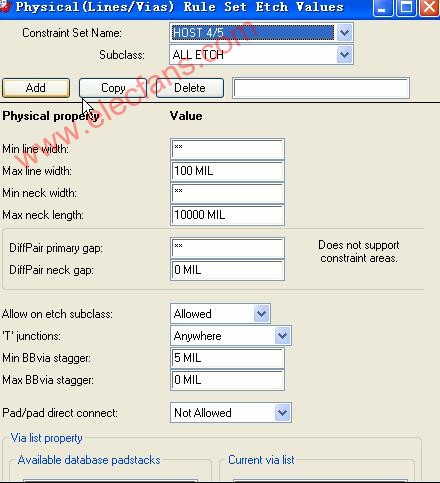

寬度和阻抗。這兩個量相互關聯,用于高速設計中的受控阻抗。了解如何將阻抗和走線寬度指定為PCB布線規則。

如果您需要為一組網絡分配相同的PCB布線規則(對于單端信號組非常常見),最快的方法是將一組中的所有網絡分配給一個網絡類別。您可以從“ PCB編輯器”窗口中的“設計”→“類”選項。將網絡分配給類別后,可以使用PCB規則和約束編輯器將設計規則分配給單個網絡或網絡類別。

其他可能不適用于特定信令標準的PCB布線規則也用于幫助確保您的設計井井有條。路由拓撲和路由層限制是兩個主要的示例。對于更高級的設計,例如具有BGA占用空間的組件,您可以使用設計規則來配置扇出策略。處理差分對需要一組自己的設計規則,如下一節所示。

差分對路由規則

差分對是唯一的,因為可以將慢速和快速信號作為差分對進行路由。無論信號是快還是慢,差分對仍然需要遵守一些通常針對單端信號實施的設計規則。差分對要考慮的四個重要設計規則是:

阻抗公差。即使您路由的長度小于臨界長度,也最好咬一下子彈,為差分對創建阻抗曲線,除非您的信令標準另有規定。其他幾何約束將取決于沿差分對的允許阻抗變化。

最大解耦長度。這告訴您最長的距離是差分對的兩側可以保持不耦合(即,相隔較大的距離)。這很重要,因為未耦合部分看起來像阻抗不連續,因此它必須足夠短。

長度匹配。請記住,差分信號是通過獲取兩個信號之間的差來讀取的,因此這兩個信號需要同時到達接收器。更快的信號需要更小的長度匹配容差。

最大凈長度。就像單端信號一樣,差分信令標準可能具有最大長度限制。以CAN總線為例;即使這是慢速標準,最大鏈接長度(PCB跡線+電纜)也將取決于您將在系統中使用的數據速率。

如果您使用的是高速差分對,則上面討論的任何其他標準高速設計規則都可以應用于差分對。注意,最簡單的方法是將相關的差分對分配給“差分對網絡類別”,然后選擇將由每個設計規則控制的類別。

如果在“對象匹配的地方”下拉菜單中未將設計規則配置為接受差分對網絡類,則可以使用查詢生成器創建自定義查詢。如下所示,用于為差分對網絡類分配最大長度(在PCB規則和約束編輯器的“高速”區域中找到)。

編輯:hfy

-

pcb

+關注

關注

4292文章

22768瀏覽量

393174 -

PCB走線

+關注

關注

3文章

133瀏覽量

13872

發布評論請先 登錄

相關推薦

Allegro布線規則的設置

單端信號的PCB布線規則

單端信號的PCB布線規則

評論