作者:小魚,Xilinx學術合作

一.概述

在文章《Verilog HDL入門思路梳理》我們說過應該如何去學習Verilog HDL描述。然而第一步,我們需要知道Verilog有哪些語法,它是否可以綜合,可以用這個語法來描述什么邏輯功能電路呢?

其實Xilinx已經貼心地準備好了答案,還給你準備了一堆參考實例。

二. Verilog行為級描述

資料名稱“Vivado Design Suite User Guide - Synthesis - UG901 (v2018.2) June 6, 2018”。(注:大家可以在Xilinx官網,或者安裝DocNav(Xilinx Documentation Navigator) 并在這里面找到這份資料。)

資料的第7章《Verilog Language Support》就是介紹在Vivado里,可綜合的Verilog描述語法以及描述方式。重點就是Verilog行為級描述(Behavioral Verilog)。

在了解了Vivado支持的可綜合的Verilog描述語法之后,我們就可以通過實例設計來加深理解。從哪里可以找到這些實例設計呢?在Vivado里面就有,下面告訴你們如何找到它們。

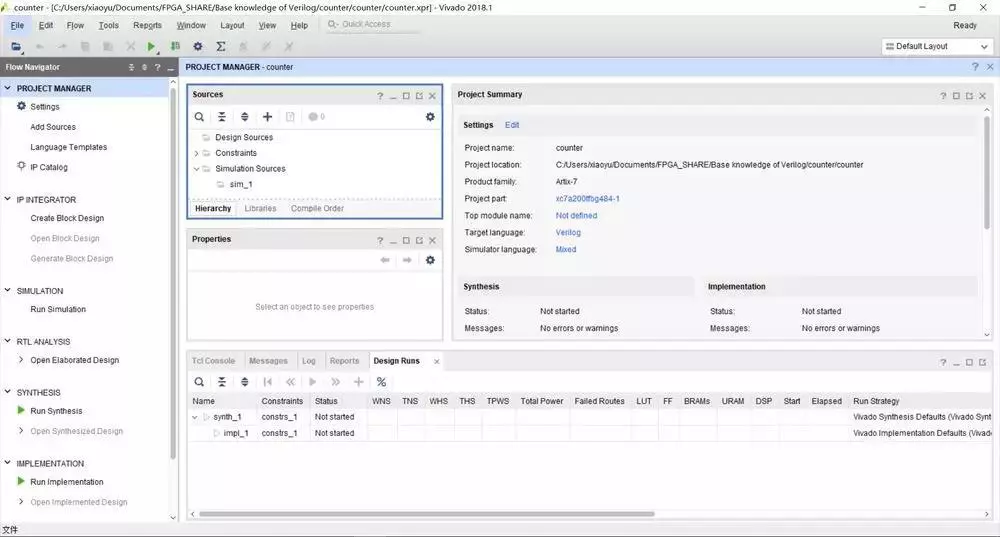

1.打開Vivado工具,先新建一個工程。然后進入下頁面。

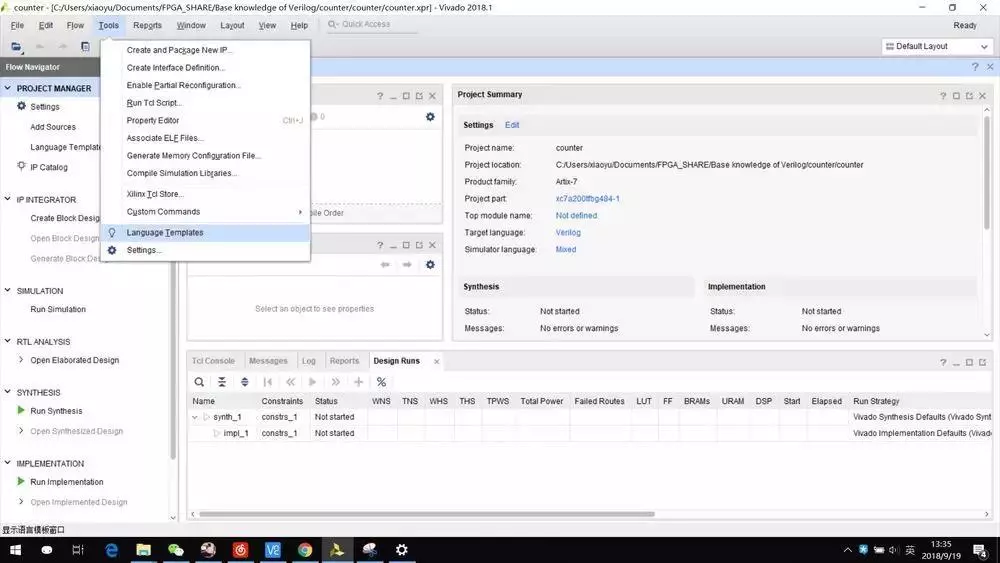

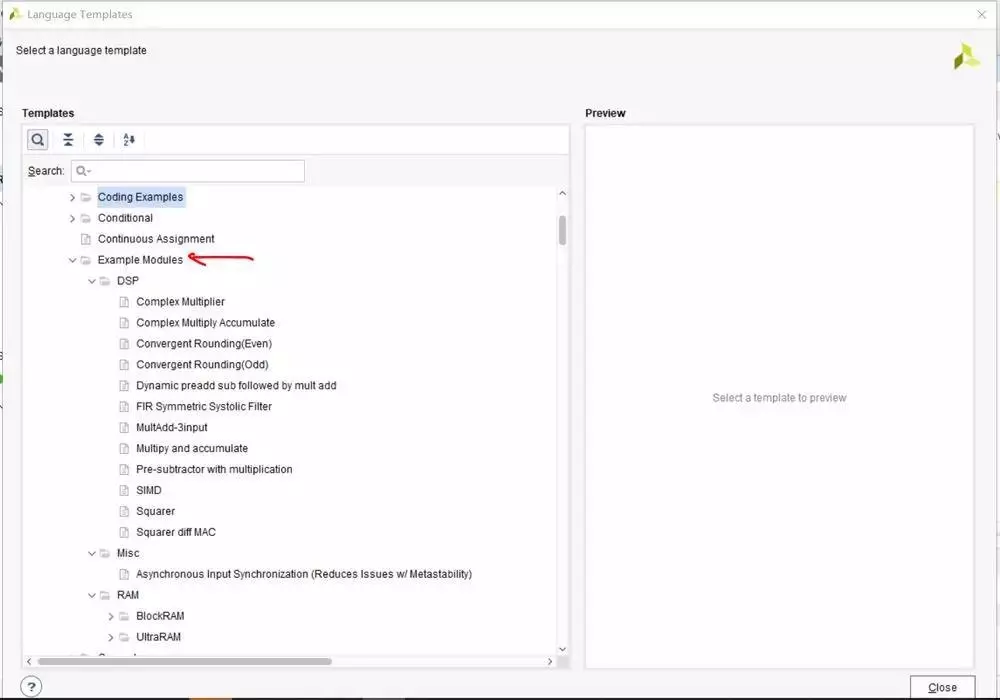

2. 在界面最上面一行菜單欄找到 “Tools”,點擊 Tools-> Language Templates

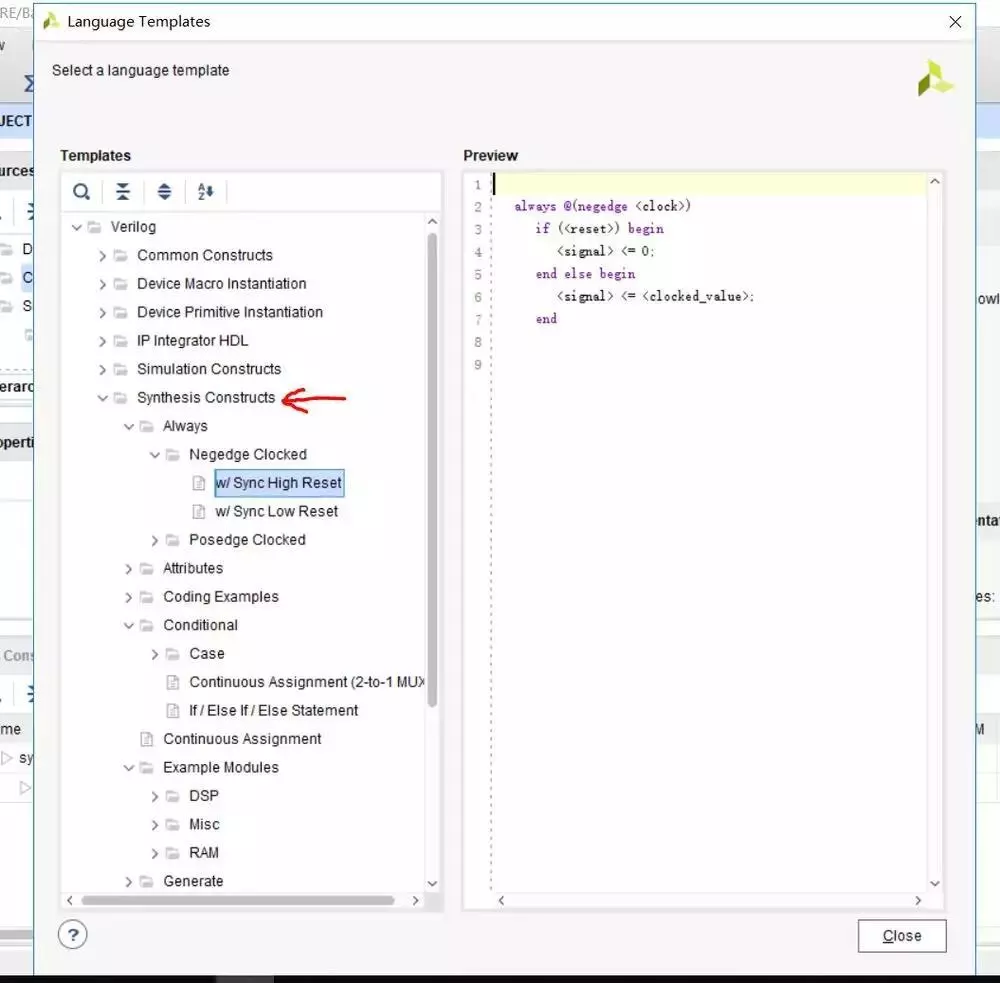

3. 將下圖中的Verilog欄展開,在Synthesis Constructs欄就是我們可綜合的常見Verilog描述。可以看到 Always ,Conditional里的case,條件選擇賦值語句,if-else等常見的語法模型他都列出來了。在Coding Example里面有一些基礎的電路模塊的Verilog描述示例。

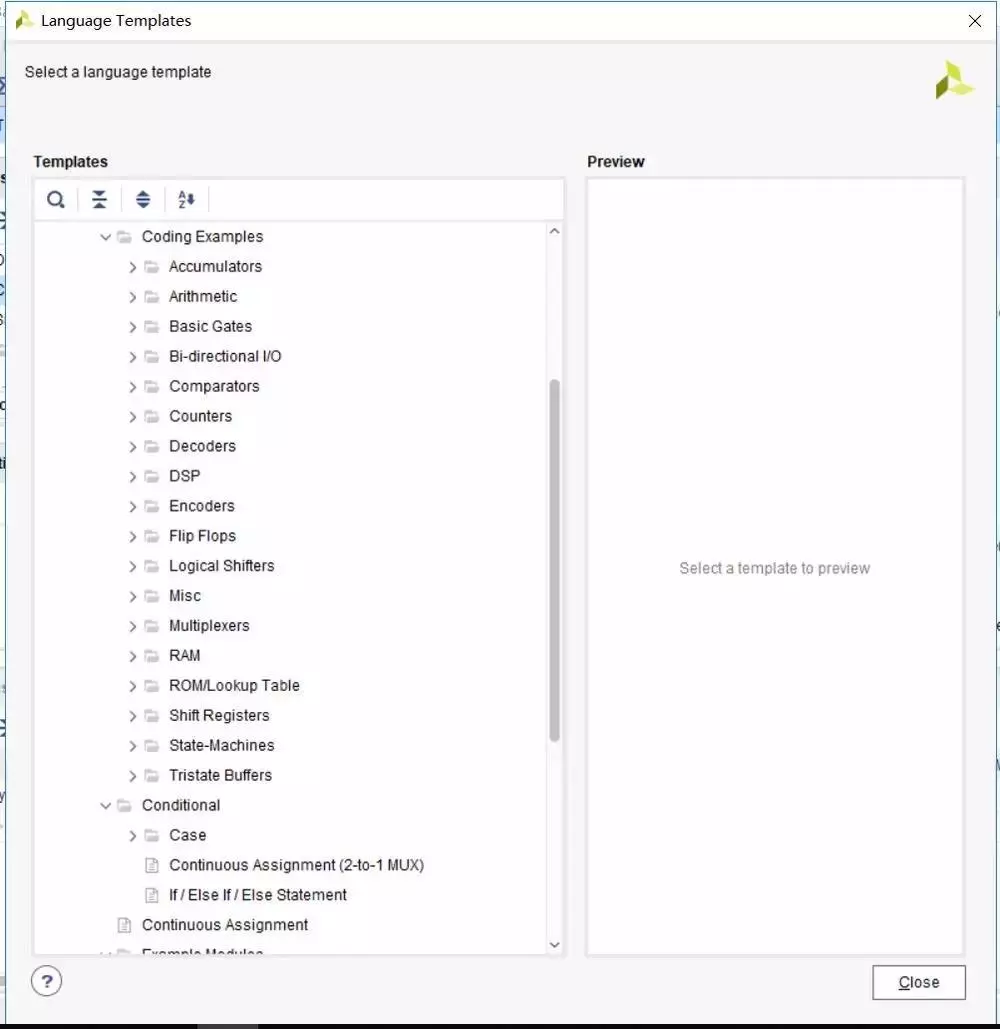

4. 展開Coding Example,可看到基礎的電路,如累加器,基礎算術電路,邏輯門,輸入輸出端口,比較器,計數器,解碼器,常見的數字信號處理電路,譯碼器,寄存器(flip flops),邏輯移位器,Misc(有七段式數碼管驅動,同步電路,防抖電路, 開漏輸出端口,脈沖調制電路),多路選擇器,RAM,ROM,移位寄存器,狀態機,三態緩沖器等等的Verilog描述示例。

對于初學者可以好好利用這些資料。把上面這些示例模板和示例設計學習并仿真一遍。主要是將Verilog描述與電路對應起來,在Vivado里面可以使用Schematic,把Verilog描述的電路原理圖顯示出來。

編輯:hfy

-

Verilog

+關注

關注

28文章

1343瀏覽量

109986 -

Vivado

+關注

關注

19文章

808瀏覽量

66326

發布評論請先 登錄

相關推薦

Verilog硬件描述語言參考手冊

FPGA學習筆記---基本語法

Verilog到VHDL轉換的經驗與技巧總結

如何快速入門FPGA

如何快速入門FPGA?

verilog與其他編程語言的接口機制

verilog調用模塊端口對應方式

verilog雙向端口的使用

verilog inout用法與仿真

verilog中for循環是串行執行還是并行執行

verilog function函數的用法

verilog同步和異步的區別 verilog阻塞賦值和非阻塞賦值的區別

FPGA入門篇:Verilog計數器

通過實例設計來加深Verilog描述語法理解

通過實例設計來加深Verilog描述語法理解

評論