互連是VLSI電路中的本地,中間和全局通信線路,其設計和物理狀態對于實現IC可靠性至關重要。互連線通常由金屬線制成,并且在傳輸電流時會暴露于電場中。電遷移(EM)和IR下降是兩個不可避免的人員傷亡,這使得互連易于退化。

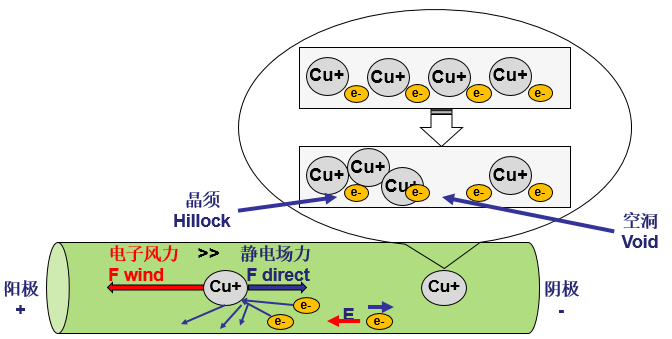

當經受高電流密度時,擁塞的互連在電子傳播方向上傳輸金屬離子。電遷移(EM)的過程會腐蝕并累積互連金屬,分別形成孔和分支。互連的較低幾何形狀和EM的影響會增強電阻,從而引起IR下降問題。互連中的EM和IR下降是造成可靠性問題并縮短深亞微米VLSI電路壽命的原因。在接下來的部分中,讓我們討論互連及其設計解決方案中一些由EM驅動的問題。

EM存在時IR下降加劇

隨著器件尺寸的減小,VLSI系統的速度和電流密度都有所提高。電源和時鐘信號互連到EM 的脆弱性在高密度IC封裝中更大。在EM的影響下,互連線在下游變窄,而上游的互連線和過孔則導致金屬沉積。

這些由EM引起的通斷會改變互連和過孔的電阻。通過電源互連的電流增加會導致IR下降,并影響設備性能。頻繁的開關活動加劇了時鐘互連中的IR下降,并降低了設備速度。如果您的IC設計包括具有不同寬度的多互連結構,則在減輕IR壓降方面會稍有成功。改進的互連設計可以減少VLSI電路塊之間的信號時間延遲,并很大程度地降低時鐘偏斜。

EM的其他后效應及其設計解決方案

如果您得到混亂的正式文件,您會保持冷靜嗎?同樣,信號傳播中的任何串擾或錯誤都會使VLSI電路正常工作。EM效應始于電路邏輯中的間歇性毛刺,隨后導致器件不穩定。EM的一些后遺癥是:

互連延遲:互連電容和電阻的增加延長了信號傳播中的RC時間延遲。互連延遲限制了IC速度及其性能特征。如果您不關心功耗,請嘗試插入互連中繼器以減少時間延遲。

通孔缺陷:隨著金屬在通孔中的衰減,會產生兩種類型的缺陷:

電阻性開路(ROP)缺陷,類似于應連接的兩個互連之間連接的缺陷電阻器。

卡塞開路(SOP)缺陷,這是應連接的兩個互連之間的開路。

單切口通孔替代多切口通孔在ROP和SOP缺陷期間提供了備用路徑。通孔的并行連接還有助于降低互連的有效電阻。

抗噪聲能力差:表面不平整,雜散阻抗,阻抗不匹配以及相鄰互連的鄰近度是影響芯片信號完整性的一些觸發因素。可以通過屏蔽互連來改善錯誤邏輯狀態的發生,降低的噪聲容限和降低的時鐘速度。

壽命縮短:在深亞微米VLSI技術中,互連質量的下降在縮短EM壽命方面起著關鍵作用。在電磁效應的作用下,空洞的尺寸和形成致命空洞的時間降低了,因此互連死亡率很高。下列IC設計修改可以提高EM壽命。

擴大互連寬度:縮小尺寸和納米級IC技術不切實際。

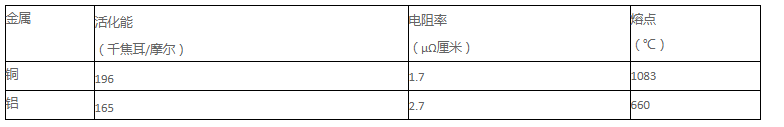

用銅(Cu)代替鋁(Al)互連:Cu具有較低的電阻率,較高的電導率和較高的熔點。根據布萊克方程式,平均失效時間(MTTF)取決于激活能量,電流密度和溫度。表1給出了Al和Cu在某些物理參數上的比較,并證明了Cu互連更好。

表1:在熔點估算的Cu和Al物理參數的比較

使用Al和Cu合金:通過使用Al-Cu合金互連,MTTF很高。它還可以在一定程度上防止互連結尖峰。

避免互連中的直角彎曲:因為實驗證明彎曲彎曲可以實現較長的芯片壽命并承受EM應力。

層間電介質:金屬互連線和低k 介電材料之間的粘附力減少了傳播延遲,并降低了基板金屬層中的內部電容和內部電容。

互連摻雜劑:將金,銀和錳等金屬作為摻雜劑引入互連金屬中。它改善了EM特性,例如EM應力,電阻和附著力,并最終改善了VLSI電路的EM預期壽命。

設計互連的簡便方法

在復雜的納米級VLSI技術中,短期可靠性是無法接受的特征。主流芯片制造行業忽視了后端(BEOL)元素(尤其是互連)的過度設計和欠設計之間的平衡。這種誘殺陷阱向IC設計工程師提出了挑戰,要求其在較小的占位面積內提供高性能和出色可靠性的新設計。在完成最壞情況的互連設計時,您需要進行幾次設計迭代,要設計出面積,電流密度,溫度,EM和IR壓降限制等約束條件。如果有簡單的出路,您喜歡走這條詳盡的道路嗎?

-

芯片制造

+關注

關注

9文章

612瀏覽量

28777 -

VLSI

+關注

關注

0文章

73瀏覽量

42895

發布評論請先 登錄

相關推薦

怎么將IR600系列路由器從DM4.0平臺遷移到InConnect平臺

IR900如何從DM4.0平臺遷移到InConnect平臺

IR900如何從shebeiyun.net平臺遷移到InConnect平臺

IR600怎樣從c.inhand.com.cn平臺遷移c.inhandcloud.com平臺

如何將IR912路由器從c.inhand.com.cn遷移至iot.inhand.com.cn平臺

淺談因電遷移引發的半導體失效

淺談因電遷移引發的半導體失效

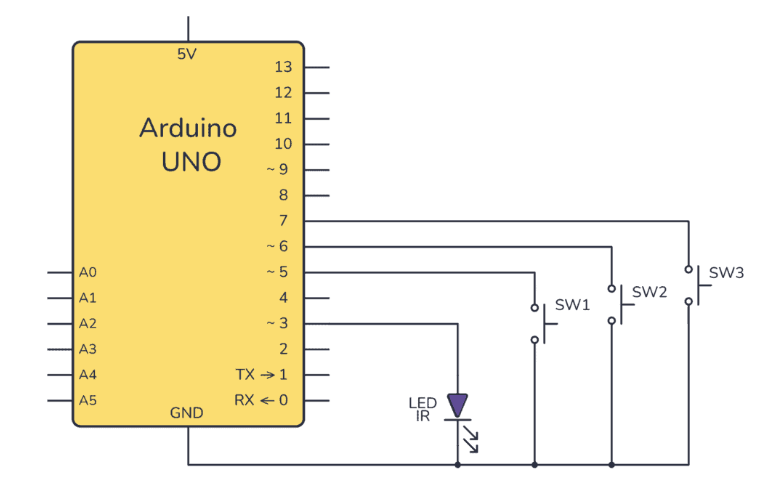

如何設置Arduino IR發射器電路

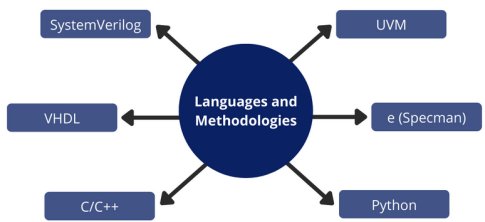

VLSI設計驗證及其方法的重要性

VLSI電路中電遷移(EM)和IR下降分析

VLSI電路中電遷移(EM)和IR下降分析

評論