實現(xiàn)一種基于Zynq-7000全可編程片上系統(tǒng)(AP SoC)的板級支持包(BSP)設計方法及應用流程。該BSP設計主要面向工業(yè)自動化監(jiān)測領域,提供了一種行之有效的嵌入式系統(tǒng)BSP實現(xiàn)流程,有利于提高工業(yè)自動化監(jiān)測系統(tǒng)的開發(fā)效率。針對使用串行通信方式的工業(yè)監(jiān)測設備,設計面向小型自動化監(jiān)測系統(tǒng)的FPGA工程,并使用專門針對基于FPGA的片上系統(tǒng)而設計的PetaLinx工具構建嵌入式Linux系統(tǒng)。最后通過自行研制的基于Zynq XC7Z010系列型號芯片的硬件平臺驗證了BSP設計的正確性及穩(wěn)定性。

0 引言

物聯(lián)網(wǎng)及嵌入式技術的發(fā)展推動了信息化與工業(yè)化的快速融合。作為一種新型產(chǎn)業(yè)模式,工業(yè)物聯(lián)網(wǎng)(Industrial Internet of Things,IIoT)在過去幾年的研究和實踐中受到很大關注[1-2]。IIoT的迅速發(fā)展使得自動化監(jiān)測系統(tǒng)的設計與研發(fā)成為新的科技熱點。IIoT將傳感器網(wǎng)絡與自動化系統(tǒng)相結合,已被用于多個行業(yè),以提高生產(chǎn)力和安全性[3-4]。自動化監(jiān)測系統(tǒng)在IIoT感知層與應用層間起著重要作用,隨著涉及的業(yè)務需求日益復雜,它的實現(xiàn)也變得越來越具挑戰(zhàn)性。在工業(yè)應用場景中軟件體系結構設計對于自動化系統(tǒng)的高效運行非常重要。先進的軟件工程解決方案對自動化系統(tǒng)設計的效率影響很大[5]。Xilinx Zynq AP SoC通過集成處理器的軟件可編程性與FPGA的硬件可編程性,實現(xiàn)了優(yōu)異的設計靈活性,可提供面向嵌入式領域可重配置的軟件工程解決方案,從而加速生產(chǎn)力。

BSP在嵌入式系統(tǒng)中扮演著關鍵角色,主要用來適配特定類型的硬件平臺。它通常包含了用來配置可定制電路的硬件比特流、引導加載操作系統(tǒng)的基礎支持代碼以及主板上所有設備的驅(qū)動程序。BSP開發(fā)目的在于屏蔽底層硬件,提供操作系統(tǒng)與硬件驅(qū)動,使操作系統(tǒng)能穩(wěn)定運行于主板環(huán)境[6-7]。由于傳統(tǒng)BSP設計存在不可或不易修改、難以復用以及設計流程復雜等問題,本文面向工業(yè)監(jiān)測領域中的自動化系統(tǒng),采用Xilinx提供的Vivado集成開發(fā)套件及用于構建和部署嵌入式系統(tǒng)到Xilinx全可編程處理器平臺的PetaLinux工具,完成了基于Zynq-7000 AP SoC的BSP設計與實現(xiàn)。

1 BSP總體結構

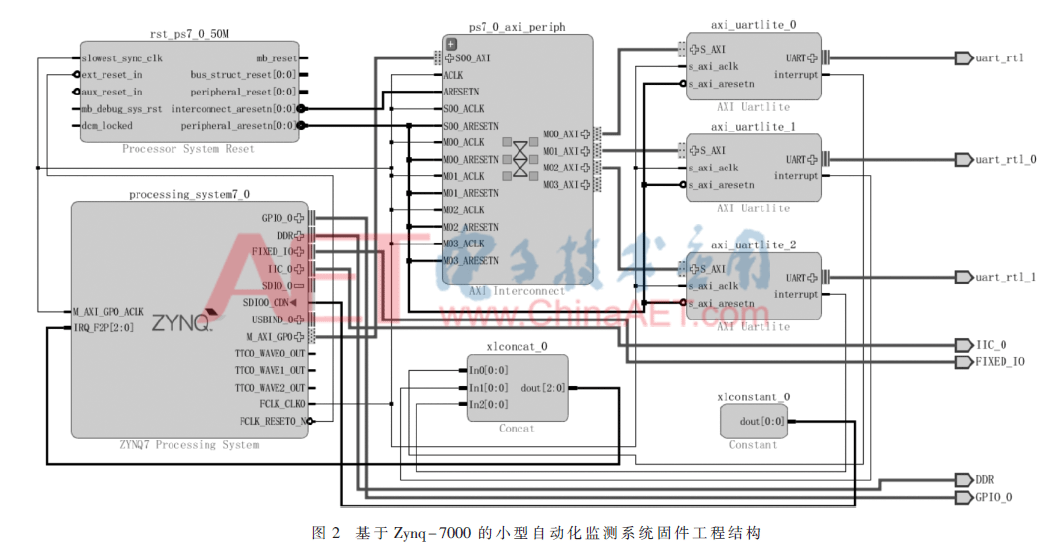

BSP設計最終生成對應用層提供支撐的鏡像文件為BOOT.BIN和image.ub。BSP的總體架構如圖1所示。BOOT.BIN啟動鏡像主要負責系統(tǒng)硬件部分配置,用于上電后配置Zynq芯片的處理器系統(tǒng)(Processing System,PS)及可編程邏輯(Programmable Logic,PL),并為Linux操作系統(tǒng)準備運行環(huán)境。image.ub支持內(nèi)核升級,功能可裁剪,由PeteLinux工具編譯打包生成。

第一階段引導加載器(First Stage Boot Loader,F(xiàn)SBL)在啟動存儲區(qū)之后運行,啟動存儲區(qū)在ARM核上電啟動時自動執(zhí)行,負責加載FSBL至片上存儲器(On Chip Memory,OCM)或在線性Flash存儲介質(zhì)上直接運行。對于運行在Zynq平臺的Linux系統(tǒng)而言,第二階段引導加載器(Second Stage Boot Loader,SSBL)即為通用引導加載器(Universal Boot Loader,U-Boot)。Xilinx提供了用于適配不同系列Zynq主板的U-Boot。基于Zynq-7000 AP SoC的BSP各個組成部分對應的功能說明如下:

(1)FSBL。FSBL負責初始化Zynq AP SoC PS端資源并使用硬件比特流文件配置PL端資源。

(2)硬件比特流。硬件比特流由Vivado集成開發(fā)工具構建的FPGA系統(tǒng)生成,包含F(xiàn)PGA編程信息,用于配置FPGA器件。

(3)SSBL。SSBL負責初始化內(nèi)存和必要的外設資源,設置Linux內(nèi)核的啟動參數(shù)以及加載Linux系統(tǒng)到內(nèi)存中運行。

(4)Linux內(nèi)核鏡像。Linux內(nèi)核鏡像是Linux操作系統(tǒng)的核心,提供硬件抽象層、進程及內(nèi)存管理、磁盤與文件系統(tǒng)控制等功能。

(5)根文件系統(tǒng)。根文件系統(tǒng)基于BusyBox源碼構建,負責管理Linux系統(tǒng)啟動及運行時所必需的目錄和關鍵性文件。

(6)設備樹。設備樹文件用于描述部分硬件信息并在Linux系統(tǒng)加載設備驅(qū)動時傳遞配置參數(shù)。

2 FPGA工程設計

傳統(tǒng)工業(yè)監(jiān)測設備中很多是符合RS232、RS422或RS485等串行數(shù)據(jù)通信標準的設備。對于自動化監(jiān)測系統(tǒng)而言,如何面向這些監(jiān)測設備提供可重配置的接口,成為一個需要解決的關鍵問題。許多傳統(tǒng)工業(yè)設備所提供的功能在出廠時便已在固件中完成燒錄定義,無法面向新的業(yè)務需求進行修改或擴展。然而,對于許多應用場景,固定功能的硬件會因為難以進行資源復用而導致成本提升。FPGA器件因為具有動態(tài)可重構的特性,被認為是數(shù)字可演化硬件系統(tǒng)一個很好的平臺[8]。Xilinx使用硅片堆疊技術設計出了高容量的FPGA,用于滿足低功耗、低延時及高帶寬的應用需求。

2.1 工程構建

在進行FPGA系統(tǒng)設計時往往需要重用已有的功能模塊,于是類似于軟件開發(fā)庫文件的IP核應運而生。IP核通常是預先設計好的電路功能模塊,主要被用于ASIC或FPGA系統(tǒng)。Xilinx提供了可連接到高級可擴展接口(Advanced eXtensible Interface,AXI)的通用異步收發(fā)器(Universal Asynchronous Receiver/Transmitter,UART)Lite。每一個AXI UART Lite IP核都可以實際對應一個串行通信接口,為工業(yè)監(jiān)測設備接入自動化監(jiān)測系統(tǒng)提供支持。AXI UART Lite IP核可以為異步串行數(shù)據(jù)傳輸提供控制器接口。它的設計目的在于和 AXI4-Lite協(xié)議實現(xiàn)連接。AXI UART Lite的主要性能和優(yōu)勢[9]如下:

(1)基于AXI4-Lite 規(guī)格的AXI 接口;

(2)一個發(fā)送通道和一個接收通道(全雙工);

(3)16個字符的發(fā)送和接收先進先出隊列(First Input First Output,F(xiàn)IFO);

(4)單個字符的數(shù)據(jù)比特位(5~8)數(shù)量可配置;

(5)校驗位(奇偶或無)可配置;

(6)波特率可配置。

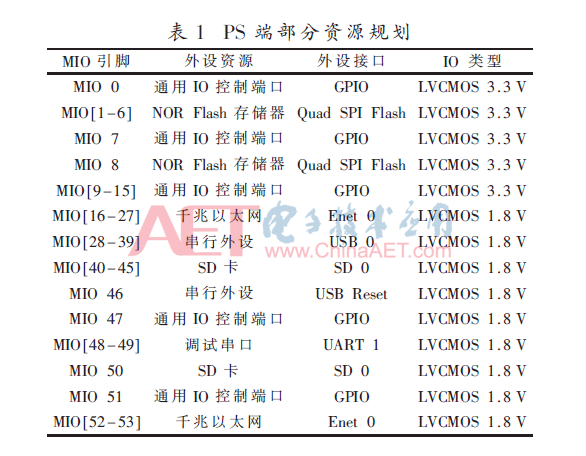

Xilinx提供了Zynq7處理器系統(tǒng)IP封裝,用于加速嵌入式系統(tǒng)的設計與配置。在Vivado集成開發(fā)環(huán)境中搭建基于Zynq-7000的小型自動化監(jiān)測系統(tǒng)FPGA工程,工程結構如圖2所示。工程中添加了ZYNQ7處理器系統(tǒng)模塊、3個AXI UART Lite模塊以及AXI互聯(lián)模塊等IP核,AXI Interconnect IP負責將一個或多個AXI存儲器映射的主器件連接到一個或多個存儲器映射的從器件。在進行FPGA系統(tǒng)設計時還預留了部分GPIO接口資源,方便對系統(tǒng)功能進行擴展。

2.2 資源配置

2.2.1 PS端資源配置

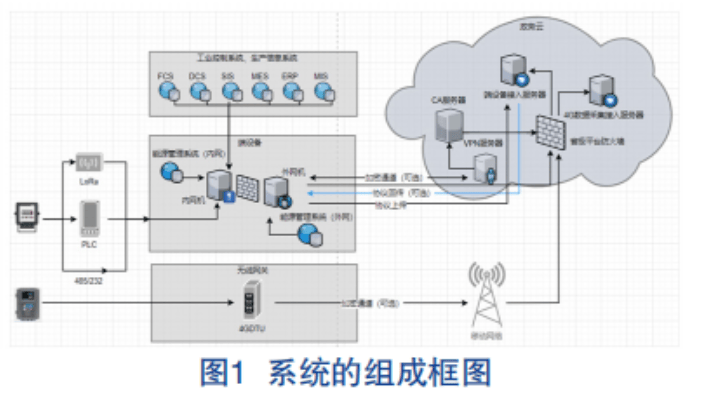

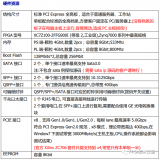

根據(jù)實際應用需求配置Zynq XC7Z010處理器系統(tǒng),并規(guī)劃XC7Z010的PS端MIO資源。MIO是I/O外設連接的基礎。XC7Z010芯片通過MIO最多可以引出54個三態(tài)通用輸入輸出(General Purpose Input Output,GPIO)引腳。這些GPIO引腳都是在程序上可控的,并且支持動態(tài)修改配置。它們可以單獨配置為輸入、輸出或中斷的功能。PS端部分資源規(guī)劃結果如表1所示。

2.2.2 PL端資源配置

Zynq中的PL主要用于擴展功能。通過使用多個特殊引腳和信號,可以將Zynq-7000內(nèi)的PS和PL緊密或松散地耦合在一起[10]。XC7Z010主芯片包含用于連接外設和某些特殊功能引腳的IO接口資源。 特殊引腳最主要用于實現(xiàn)復位、狀態(tài)指示、系統(tǒng)配置、模式配置等功能,通過特定引腳和功能復用引腳來實現(xiàn)。XC7Z010的主要特殊引腳的配置說明如表2所示。

3 PetaLinux工程設計

使用PetaLinux工具構建基于Zynq AP SoC的嵌入式Linux操作系統(tǒng)。PetaLinux工具包括定制的BSP生成工具、Linux配置工具以及軟件開發(fā)工具。使用這些工具可以實現(xiàn)引導加載程序、Linux內(nèi)核以及Linux應用程序的靈活配置,有利于開發(fā)者在Xilinx處理系統(tǒng)上定制、構建和調(diào)配嵌入式Linux解決方案。

3.1 系統(tǒng)頂層配置

基于Zynq工程模板創(chuàng)建PetaLinux工程,導入固件工程生成的硬件描述文件并進行系統(tǒng)頂層配置,系統(tǒng)頂層配置項包括Linux組件選擇、自動配置項設置、子系統(tǒng)硬件自動配置項設置、內(nèi)核引導參數(shù)設置、U-Boot設置、鏡像文件打包配置等。其中子系統(tǒng)硬件自動配置項設置為必選項,允許自定義系統(tǒng)范圍的硬件設置,如:以太網(wǎng)卡設置、Flash設置、串口設置、實時時鐘(Real-Time Clock,RTC)芯片設置、SD卡設置等。Petalinux工具將根據(jù)系統(tǒng)頂層配置解析硬件描述文件,以便更新設備樹所需的硬件信息。

3.2 Linux內(nèi)核配置

Linux內(nèi)核主要提供五大功能,分別為虛擬文件系統(tǒng)、網(wǎng)絡服務、內(nèi)存管理、進程管理和設備管理。Xilinx 提供了免費的PetaLinux開發(fā)工具,使開發(fā)人員可以輕松在Zynq AP SoC上配置、構建和部署Linux系統(tǒng)及應用,提高軟硬件設計開發(fā)效率。Linux內(nèi)核配置基于Linux 4.6.0內(nèi)核進行,主要包括USB串口驅(qū)動配置、以太網(wǎng)驅(qū)動配置、GSM和CDMA調(diào)制解調(diào)器的USB驅(qū)動配置、Xilinx-uartlite串口驅(qū)動配置、DS18B20溫度傳感器驅(qū)動配置、GPIO支持等。PetaLinux工程基于開源的協(xié)作軟件Yocto創(chuàng)建。Yocto致力于創(chuàng)建可定制的嵌入式產(chǎn)品和統(tǒng)一嵌入式Linux系統(tǒng)的開發(fā)標準,它提供了許多模板、工具和方法,使得開發(fā)者無需關心硬件體系,避免許多重復工作,從而提高開發(fā)效率和產(chǎn)品質(zhì)量。Linux內(nèi)核的更新以打補丁的方式實現(xiàn),內(nèi)核源碼的更新不影響已修改的系統(tǒng)配置項。

3.3 設備樹配置

Linux內(nèi)核通過設備樹文件獲取板級硬件的細節(jié)信息從而加載設備驅(qū)動。設備樹可以對硬件進行規(guī)范化描述,支持多平臺內(nèi)核鏡像,具備簡化的板卡端口,使用更少的平臺描述代碼以及更精簡的設備驅(qū)動代碼[11]。PetaLinux設備樹配置關聯(lián)文件主要有pcw.dtsi、plnx_aarch64-system.dts、system.dts、system-conf.dtsi、system-top.dts。這些文件統(tǒng)一由PetaLinux工程自動生成,開發(fā)者通過修改system-top.dts文件來滿足特定的系統(tǒng)需求。基于Zynq-7000的小型自動化監(jiān)測系統(tǒng)具備網(wǎng)口調(diào)試、RTC時鐘支持、溫濕度監(jiān)測、網(wǎng)絡數(shù)據(jù)傳輸?shù)裙δ堋P枰趕ystem-top.dts文件中進行相應節(jié)點信息的修改或添加新的硬件描述節(jié)點。例如在設備樹配置文件system-top.dts中添加RTC時鐘硬件描述信息及修改后的網(wǎng)卡芯片節(jié)點信息如下:

&i2c0 {

status = "okay";

rtc@51 {

compatible = "nxp,pcf8563";

reg = <0x51>;

};

};

&gem0 {

compatible = "cdns,zynq-gem", "cdns,gem";

status = "okay";

phy-mode = "rgmii-id";

xlnx,ptp-enet-clock = <0x69f6bcb>;

local-mac-address = [00 0a 35 00 1e 53];

};

4 BSP總體測試

在基于XC7Z010的硬件平臺中對BSP進行總體測試,設備上電后,處理器自動執(zhí)行片內(nèi)BootROM中的代碼,初始化CPU和一些外圍設備,以便讀取燒錄在NOR Flash中的BOOT.BIN引導鏡像,BOOT.BIN引導鏡像加載存儲在eMMC上image.ub到DDR3中運行。然后,文件系統(tǒng)中的mystartup.sh腳本啟動存儲在eMMC中的系統(tǒng)初始化腳本文件,執(zhí)行系統(tǒng)初始化配置。PetaLinux系統(tǒng)部分啟動信息如圖3所示。

圖3(a)為PL部分擴展的AXI UART Lite模塊注冊加載信息,在Linux下作為標準串口分別對應設備文件描述符ttyUL1、ttyUL2及ttyUL3。圖3(b)為內(nèi)存技術設備(Memory Technology Device,MTD)驅(qū)動加載信息,MTD是用于訪問存儲介質(zhì)的Linux的子系統(tǒng),此處表示NOR Flash存儲器,共創(chuàng)建了boot、bootenv、kernel以及spare 4個MTD子分區(qū),其中spare分區(qū)為空閑分區(qū),可用于燒錄設備唯一序列號。圖3(c)為GSM模塊USB接口連接檢測信息及網(wǎng)口芯片啟動狀態(tài)信息,其中GSM模塊對應Linux系統(tǒng)下的設備文件描述符ttyUSB0、ttyUSB1、ttyUSB2、ttyUSB3及ttyUSB4。

5 結論

本文實現(xiàn)一種面向自動化監(jiān)測系統(tǒng)的BSP設計方法,并完成了面向小型微型自動化監(jiān)測系統(tǒng)的BSP設計與實踐。用于評測BSP功能及性能的硬件平臺選用Xilinx Zynq XC7Z010芯片作為硬件系統(tǒng)主控制器,BSP部分針對自動化監(jiān)測系統(tǒng)應具備的基本功能在嵌入式Linux系統(tǒng)中添加了相應的設備驅(qū)動,可充分滿足工業(yè)監(jiān)測領域的業(yè)務需求。實際測試結果表明,該BSP具有開發(fā)便捷、通用性強、便于進行功能擴展和Linux內(nèi)核升級、運行穩(wěn)定等特點,驗證了基于Zynq-7000的自動化監(jiān)測系統(tǒng)BSP設計的可行性與正確性,對于工業(yè)自動化系統(tǒng)的BSP設計與實現(xiàn)有一定的參考價值和實際指導意義。由于自動化監(jiān)測系統(tǒng)的功能日益復雜,該BSP設計仍需在實踐中不斷進行完善。

編輯:hfy

-

Linux

+關注

關注

87文章

11230瀏覽量

208931 -

監(jiān)測系統(tǒng)

+關注

關注

8文章

2677瀏覽量

81256 -

Zynq

+關注

關注

9文章

608瀏覽量

47128

發(fā)布評論請先 登錄

相關推薦

當ADC3663的LVDS輸出給到ZYNQ-7000的LVDS接收這兩者之間可以直連嗎?

小型氣象自動監(jiān)測站

zynq7000 BSP無法在u-boot加載運行怎么解決?

zynq7000 BSP無法在u-boot加載運行,為什么?

隧道安全監(jiān)測自動化系統(tǒng)解決方案

淺談企業(yè)能耗在線監(jiān)測系統(tǒng)在電氣自動化管理中的應用

微型導軌在自動化制造中有哪些優(yōu)勢?

簡談Xilinx Zynq-7000嵌入式系統(tǒng)設計與實現(xiàn)

Xilinx ZYNQ 動手實操演練

Zynq-7000為何不是FPGA?

自動化水質(zhì)監(jiān)測系統(tǒng)解決方案

簡談Xilinx Zynq-7000嵌入式系統(tǒng)設計與實現(xiàn)

沙特stc和華為商用核心網(wǎng)自動化實踐榮獲“年度最佳自動化項目獎”

基于IMX214+ZYNQ XC7Z100的1080P雙目視覺智能平臺

基于Zynq-7000面向小型微型自動化監(jiān)測系統(tǒng)的BSP設計與實踐

基于Zynq-7000面向小型微型自動化監(jiān)測系統(tǒng)的BSP設計與實踐

評論