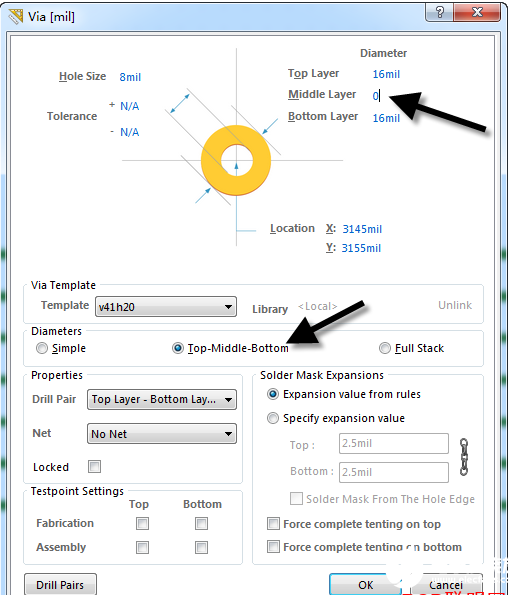

有時(shí)候?yàn)榱嗽龃髢?nèi)層的敷銅面積,特別是BGA區(qū)域,尤其在高速串行總線日益廣泛的今天,無(wú)論是PCIE、SATA,還是GTX、XAUI、SRIO等串行總線,都需要考慮走線的阻抗連續(xù)性及損耗控制,而對(duì)于阻抗控制主要是通過(guò)減少走線及過(guò)孔中的Stub效應(yīng)對(duì)內(nèi)層過(guò)孔進(jìn)行削盤處理。過(guò)孔的削盤處理如圖1所示,雙擊過(guò)孔,設(shè)置其屬性,選擇“TOP-Middle-Bottom”模式,把內(nèi)層焊盤的大小設(shè)置為“0”即可,多選擇過(guò)孔的話可以批量處理。

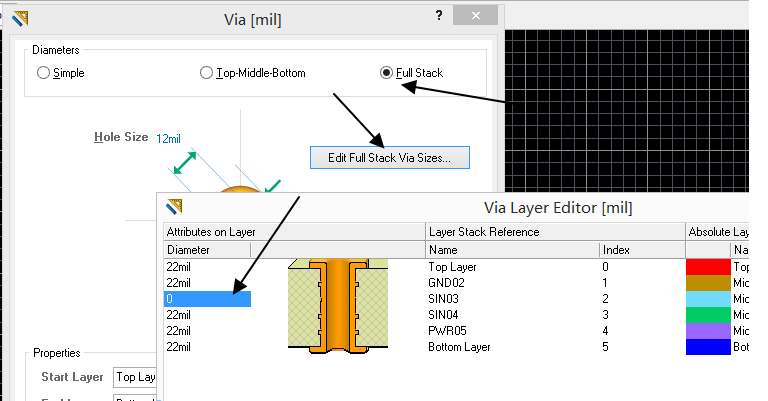

如果是行單獨(dú)對(duì)某個(gè)層進(jìn)行削盤 可以選擇FUll stack 的選項(xiàng),想對(duì)應(yīng)的層設(shè)置為0mil即可

編輯:hfy

-

pcb

+關(guān)注

關(guān)注

4317文章

23006瀏覽量

396305 -

BGA

+關(guān)注

關(guān)注

4文章

536瀏覽量

46732 -

過(guò)孔

+關(guān)注

關(guān)注

2文章

197瀏覽量

21839 -

阻抗控制

+關(guān)注

關(guān)注

1文章

55瀏覽量

10643

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

雙面板 板厚1.6 層疊結(jié)構(gòu)中的 TOP BOTTOM 和中間層的厚度多少

PADS過(guò)孔:有什么辦法設(shè)置使得中間層的keepout只比鉆孔大6mil

PROTEL99 的中間層為什么不能完整覆銅

pads layout中間層無(wú)法鋪銅,請(qǐng)教是怎么回事?

多層PCB設(shè)計(jì)的中間層創(chuàng)建設(shè)置

請(qǐng)問(wèn)PCB設(shè)計(jì)中文字放在中間層會(huì)有什么問(wèn)題出現(xiàn)?

嵌入式系統(tǒng)結(jié)構(gòu)硬件層中間層系統(tǒng)軟件層

PCB四層板的中間層能走信號(hào)線嗎?

基于NDIS中間層的包過(guò)濾的研究與設(shè)計(jì)

Al合金接觸反應(yīng)釬焊接頭力學(xué)響應(yīng)及中間層厚度的確定

Altium-Designer-Duplicate-Net-Names-Wire-XXX解決辦法

Altium-Designer規(guī)則設(shè)計(jì)技巧過(guò)孔和焊盤

Altium Designer規(guī)則設(shè)計(jì)技巧之過(guò)孔和焊盤

Altium處理過(guò)孔中間層削盤的解決辦法

Altium處理過(guò)孔中間層削盤的解決辦法

評(píng)論