如果您閱讀了許多PCB設計指南,尤其是有關并行協議和差分對布線的指南,則將看到很多關于走線長度匹配的內容。當您需要進行跡線長度匹配時,您的目標是最大程度地減少串行協議中的差分對,并行協議中的多個對(例如PCIe),并行協議中的多個跡線/對或使用以下協議的任何協議之間的時序差異源同步時鐘。CAD工具使您可以輕松地考慮一次發生的情況。但是,在其他頻率下會發生什么。更具體地說,寬帶信號會發生什么?

所有數字信號都是寬帶信號,其頻率內容從DC擴展到無窮大。由于數字信號的帶寬很大,跡線長度匹配應使用哪個頻率?不幸的是,用于跡線長度匹配的頻率是模棱兩可的,因此設計人員需要了解如何應對PCB跡線長度匹配與頻率的關系。為了更好地理解這一點,我們需要研究寬帶設計中使用的技術,以及如何在走線長度匹配中考慮整個信號帶寬。

差分對的PCB走線長度匹配與頻率的關系

正確進行跡線長度與頻率的匹配需要考慮到跡線上傳播信號的整個帶寬。在過去的幾年中,這一直是差分串行協議的研究主題,諸如USB 4之類的標準對寬帶信號完整性指標提出了特定要求。一些示例寬帶信號完整性指標是:

集成差分串擾

積分差分插入損耗

積分差分回波損耗

積分差分阻抗偏差

所謂“集成”,是指信號完整性的特定方面適用于整個相關頻率范圍。換句話說,如果以差分串擾為例,我們希望將兩個差分對之間的差分串擾最小化到某個極限以下,這在信令標準中已指定。我們馬上將看到為什么這對于跟蹤長度匹配很重要。

分散

在時域中,我們只關心差分對的兩端在同一時刻跨過HI和LOW狀態(假設為二進制)之間的中途過渡。顯然,抖動在這里造成了一個問題,即它會將您的走線長度限制在一定的最小容限范圍內,因此,您永遠不會在同一時刻使一對線的兩端完美過渡。在頻域中,我們需要考慮以下來源的色散:

幾何色散:這是由于互連的邊界條件和幾何形狀而引起的,然后,邊界和幾何形狀決定了互連的阻抗隨幾何形狀的變化。

介電擴散: 這發生在PCB基板中,并且與PCB上互連的幾何形狀無關。它包括Dk的色散和損耗。

粗糙度色散:由于銅粗糙度模型的因果關系以及高頻下的趨膚效應,會產生這種額外的色散來源。

纖維編織的色散:PCB層壓板中的纖維編織在整個互連中產生周期性的色散變化。

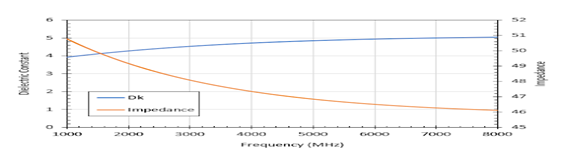

因為這些色散源始終存在于走線中,所以它們會導致實際PCB走線的阻抗,速度和所有其他信號完整性指標是頻率的函數。下面顯示了一個示例,該示例顯示了Dk實部中的色散如何影響微帶走線的阻抗。

信號速度

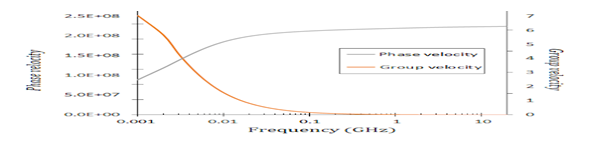

如果您熟悉傳輸線理論,那么您就會知道阻抗和信號速度密切相關。讓我們以PCB走線的信號速度為例。下圖顯示了具有粗糙度和色散的模擬帶狀線的組速度和相速度。

帶銅粗糙度和介電色散的示例帶狀線上信號的群速度和相速度。

在這里我們可以看到,相速度在很寬的頻率范圍內變化很大,從1 MHz到20 GHz達到2倍的變化。相速度的變化在這里是重要的參數,因為這是不同頻率分量沿互連線傳播的速率。通過這種變化,我們可以看到對于實際互連而言,PCB跡線長度匹配與頻率之間的匹配變得多么困難。我們需要某種方式來考慮所有頻率,而不僅僅是任意選擇的單個頻率。

寬帶長度匹配與頻率

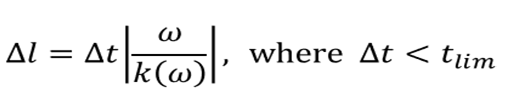

為了制定長度匹配的度量,我們需要考慮給定信令標準的最小允許長度偏差。我們將此最小時間偏差稱為tlim。我們可以寫出以下有關長度公差和允許的時序失配的方程:

根據允許的時序變化的長度變化。

在此,函數k只是互連上信號的傳播常數,這也是由于色散引起的頻率的函數。我們可以采用統計方法使用稱為“ Lp范數”的方法來處理允許的長度不匹配。無需太過深入地研究所涉及的數學,只需知道該度量等效于計算函數和某個平均值(它們之間僅相差一個常數)之間的RMS差異即可。因此,這使其成為解決某些目標設計值和信號完整性度量(阻抗,脈沖響應衰減/延遲,串擾強度等)之間變化的理想數學工具。

使用Lp范數,我們可以根據時序不匹配限制tlim定義的一些上限來重寫允許的長度不匹配:

根據允許的時序變化的長度變化。

當使用寬帶信號完整性指標進行PCB設計時,可以將上述方程式視為一個約束條件:在確定傳輸線的尺寸時,這可能會影響差分對的兩端之間或中的任意兩條走線之間的總允許長度偏差。高速并行協議。只要您知道傳輸線的傳播常數,積分就很容易計算。然后,可以使用場求解器來計算此值,具有標準傳輸線幾何形狀的分析模型來手動計算。

只是為了給計算提供一些數字,如果我使用上面顯示的模擬帶狀線的相速度,我們會發現,如果允許的最大最大值,則平行的兩條單端完全隔離的跡線之間的最大允許長度不匹配為2.07 mm時序不匹配為10 ps。請注意,對于10 ps,這是許多高速數字信號的邊沿速率的很大一部分。對于我上面模擬的帶狀線,這等于1.3041毫米的允許長度不匹配。

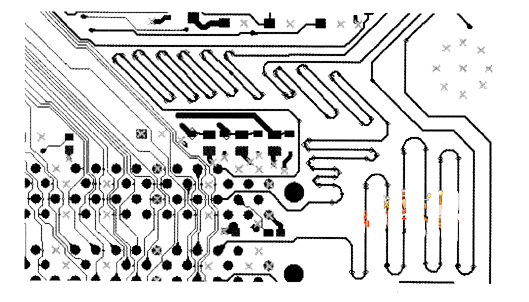

總而言之,我們已經證明,使用Lp范數可以將PCB跡線長度匹配與頻率的關系降低為單個度量。如果您是PCB設計人員,則無需手動執行此計算,而只需要使用正確的PCB布線工具集即可。

編輯:hfy

-

pcb

+關注

關注

4317文章

23014瀏覽量

396380 -

寬帶信號

+關注

關注

1文章

17瀏覽量

11246

發布評論請先 登錄

相關推薦

PCB板上的差分傳輸線長度匹配問題

高速信號的走線長度如何控制?

如何在PADS9.2里生成走線長度報表?

如何實現Altium PCB設計中的內部走線長度?

Technical Note--Allegro中走線長度的設

如何預防走線長度引起的電磁場

如何用LOTO示波器TDR方法測試電線長度?

高速PCB設計調整走線長度

pcb如何在走線長度匹配中考慮整個信號帶寬

pcb如何在走線長度匹配中考慮整個信號帶寬

評論