前言:

芯粒逐漸成為半導體業界的熱詞之一,它被認為是一種可以延緩摩爾定律失效、放緩工藝進程時間、支撐半導體產業繼續發展的有效方案。

摩爾定律的演變

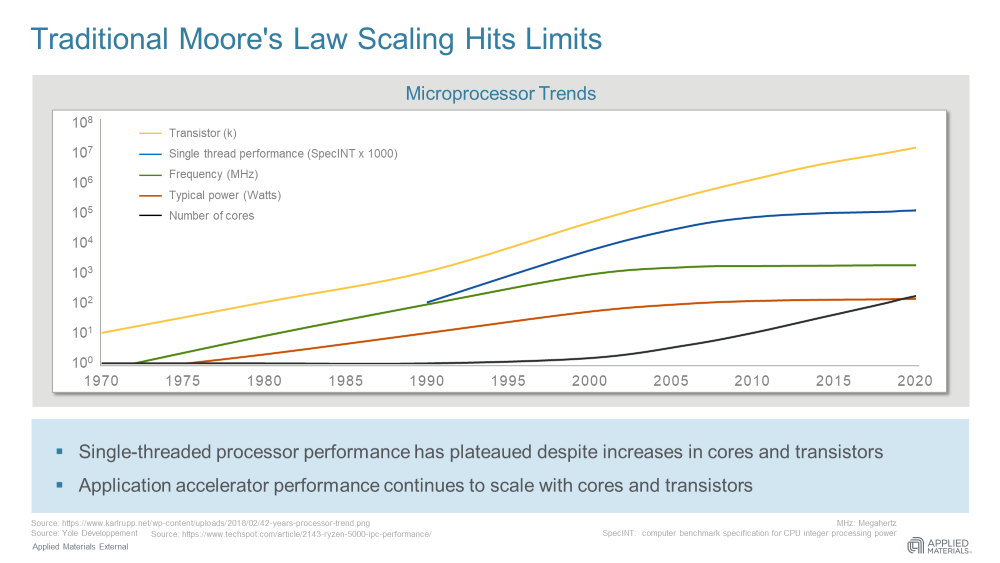

即便不是IT從業人士,想必也會聽說過著名的“摩爾定律”:1965年,英特爾創始人戈登·摩爾提出,在至多十年內,集成電路的集成度會每兩年翻一番,后來這個周期被縮短為18個月。當時摩爾先生僅僅是將摩爾定律的適用時間限定在“十年內”,但實際上處理器技術的發展令人咋舌,至今這條在當時遭到無數人質疑的奇妙定律仍舊在生效,基本上每兩年制程工藝都會進入一個新的臺階。

但是,如今主流的處理器制程已經發展到22nm,而更先進的14nm、10nm工藝也已經進入了芯片制造商的產品藍圖,硅片晶體管的尺寸有著其物理極限,美國國防先進研究項目局主任Robert Colwell先生曾表示,半導體技術不斷發展,制造工藝已經達到 7nm,依靠縮小線寬已無法同時滿足性能、功耗、面積以及信號傳輸速度等多方面的要求,越來越多的半導體廠商開始把注意力放在系統集成層面,亟需發掘新的材料和芯片技術,成為硅晶體管技術的替代品。然而這是一種超越摩爾定律,是通過系統集成單顆芯片或是多芯片堆疊的方式實現,希望能做到更多的功能。

后摩爾時代的技術明星——芯粒

近年來,半導體廠商發現芯粒可以被認為延緩摩爾定律失效,放緩工藝進程時間,支撐半導體產業繼續發展的有效方案。那什么是芯粒呢?理論上,芯粒模式是一種,開發周期短且成本較,低的方法,提供了先進工藝和主流成熟工藝選擇的靈活性,芯粒技術就是像搭積木一樣,可以將不同節點工藝(10nm、14/16nm及22nm)、不同材質(硅、砷化鎵、碳化硅、氮化鎵)、不同功能(CPU、GPU、FPGA、RF、I/O、存儲器)、不同半導體公司的芯片封裝在一起。

后摩爾時代保鮮劑芯粒的優點

后摩爾時代的單片集成向多片異構封裝集成技術“改道”是重要趨勢,相對于以往的軟 IP 形式,芯粒則是經過硅驗證的裸芯片。芯粒能在實現高效能運算的同時,提供更高的帶寬、更低的功率、更低的成本和更靈活的形狀因子等優勢。

目前,已經有很多公司創建了自己的芯粒生態系統。隨著芯片制程從10nm7nm到,5nm再到未來的3nm,每一次制程縮減所需要的成本和開發時間都在大幅提升。而且,當芯片制程接近1nm時,就將進入量子物理的世界,現有的工藝制程會受到量子效應的極大影響。

未來,以芯粒模式集成的芯片會是一個“超級”異構系統,為IC產業帶來更多的靈活性和新的機會。

后摩爾時代保鮮劑芯粒的優點

芯粒模式成功的關鍵在于芯粒的標準和接口。但作為一種創新,芯粒模式存在多種挑戰。

① 技術層面

芯粒的組裝或封裝尚缺乏統一的標準。目前各大玩家都有自家的方案,盡管各家的名稱不同,但歸總離不開硅通孔、硅橋和高密度FO技術,不管是裸片堆疊還是大面積拼接,都需要將互連線將變得更短,要求互連線做到100%的無缺陷,否則整個芯片無法工作。

② 質量保障問題

相對傳統軟IP,芯粒是經過硅驗證的裸芯片,可以保證物理實現的正確性。但如果其中的一個裸芯片有問題,則整個系統都會受影響,代價很高。因此要保證芯粒100%無故障。當然這其中也包括集成后的測試,封裝后,可能有部分芯粒可能完全無法直接從芯片外部管腳直接訪問,給芯片測試帶來的新的挑戰。

③ 散熱問題

幾個甚至數十個裸芯片封裝在一個有限的空間中,互連線非常短,讓散熱問題變得更為棘手。

④ 芯片網絡問題

盡管每個芯粒本身設計不會發生死鎖,其通信系統都可以很好地工作,但是當它們全部連接在一起形成芯片網絡時,就可能出現了交通死鎖與流量堵塞問題。超微半導體研究人員最近提出一種消除死鎖難題的方案,如果能夠徹底解決死鎖問題,那么芯粒將為未來計算機設計的發展帶來新的動力。

⑤ 供應鏈重塑問題

在芯粒模式下,EDA工具提供商、芯片提供商、封測提供商都要有所改變。比如芯粒模式中出現的問題可能最終都需要通過EDA工具的改進來給出答案,需要EDA工具從架構探索、到芯片實現、甚至到物理設計提供全面支持。還有來自不同的芯片提供商的裸芯片進入封裝提供商工廠的進度同步問題。

結尾

芯粒將驅動半導體工業的未來,而這是一場即將到來的MCP海嘯。大型芯片制造商也正在轉向芯粒,若干年后是否會形成一個開放的產業生態、是否要建立芯粒生態推進聯盟是值得行業思考的問題。

編輯:hfy

-

處理器

+關注

關注

68文章

19160瀏覽量

229115 -

eda

+關注

關注

71文章

2708瀏覽量

172868 -

芯片制程

+關注

關注

0文章

51瀏覽量

4667 -

芯粒

+關注

關注

0文章

58瀏覽量

122

發布評論請先 登錄

相關推薦

擊碎摩爾定律!英偉達和AMD將一年一款新品,均提及HBM和先進封裝

強勢入局芯粒技術鏈 東方晶源PanSys產品重磅發布

“自我實現的預言”摩爾定律,如何繼續引領創新

封裝技術會成為摩爾定律的未來嗎?

摩爾定律的終結:芯片產業的下一個勝者法則是什么?

英特爾CEO基辛格:摩爾定律放緩,仍能制造萬億晶體

英特爾CEO基辛格:摩爾定律仍具生命力,且仍在推動創新

奇異摩爾以互聯解決方案,共建可持續、開放的芯粒生態

摩爾定律的演變 后摩爾時代的芯粒技術

摩爾定律的演變 后摩爾時代的芯粒技術

評論