在一些應(yīng)用中,有些特定的信號(hào)我們需要保留,用于進(jìn)行采集檢測,而綜合器會(huì)自動(dòng)優(yōu)化把它綜合掉,那么,應(yīng)該怎樣告訴綜合器,不讓它優(yōu)化掉我們需要保留的信號(hào)呢?

對(duì)這種情況的處理是增加約束,共有2種情況:

1、需要保留的信號(hào)是引線

Verilog HDL—定義的時(shí)候在后面增加/* synthesis keep */。

例如:wire keep_wire /* synthesis keep */;

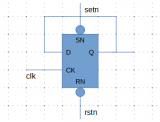

2、需要保留是的寄存器

跟reg相關(guān)的synthesis attribute,共有兩種,分別是/*synthesis noprune*/和/*synthesis preserve*/,兩者的差別如下:

/*synthesis noprune*/ 避免 Quartus II 優(yōu)化掉沒output的reg。

/*synthesis preserve*/避免 Quartus II 將reg優(yōu)化為常數(shù),或者合并重復(fù)的reg。

定義的時(shí)候在后面增加相關(guān)的約束語句。

例如:reg reg1 /* synthesis noprune*/;或者 reg reg1 /* synthesis preserve */;

將/*synthesis noprune*/等synthesis attribute 語句放在module后面,這樣整個(gè)module的reg將不被最佳化,從而不用再一一寄存器指定。

注意:以上所提到的synthesis attribute必須寫在結(jié)束分號(hào)前面,寫在分號(hào)后面只相當(dāng)于注釋:

正確:reg reg1 /* synthesis preserve */;

錯(cuò)誤:reg reg1 ;/* synthesis preserve */

-

FPGA

+關(guān)注

關(guān)注

1626文章

21675瀏覽量

601982 -

FPGA設(shè)計(jì)

+關(guān)注

關(guān)注

9文章

428瀏覽量

26489

原文標(biāo)題:FPGA設(shè)計(jì)中如何保持信號(hào)不被綜合

文章出處:【微信號(hào):HXSLH1010101010,微信公眾號(hào):FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

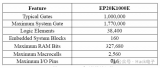

FPGA門數(shù)的計(jì)算方法

保持FPGA設(shè)計(jì)信號(hào)不被綜合的方法

保持FPGA設(shè)計(jì)信號(hào)不被綜合的方法

評(píng)論