為了向當今的大電流,低壓PCB上的負載提供指定的電源電壓,設計人員必須通過了解可用的解決方案及其權衡因素,將IR壓降降低。

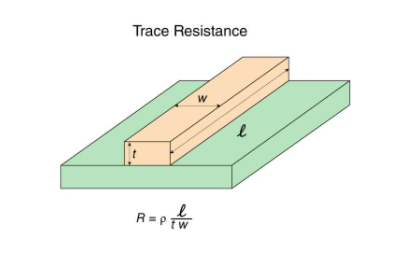

盡管低功耗組件的大量使用,但當今的印刷電路板(PCB)仍需要大量電流,而常用的電路板消耗50、100甚至200 A的電流。每當電流傳遞給負載時,都會存在基于IR的壓降,設計人員在對電路板進行布局以及放置電源,直流電源軌和負載時必須考慮這一損耗。為了保持一致和可靠的運行,重要的是要確保該壓降不會將這些直流電源電壓推到其頻帶的下限。通常,它是標稱值的正負幾個百分點。諸如FR-4之類的PCB層壓板上的銅(之所以稱呼是因為每平方英尺重1盎司),厚度為35 μm;2盎司 當然,銅的厚度是原來的兩倍,而“薄”的銅則只有一半。使用1盎司。銅作為一個例子,一個10厘米長,1毫米寬的跟蹤將具有約50μm的電阻Ω(銅的電阻率是1.74 × 10 -8 Ω?m在20 ° C)。有許多方便的在線電阻計算器,例如Trance-Cat的 計算器(圖1)。

圖1

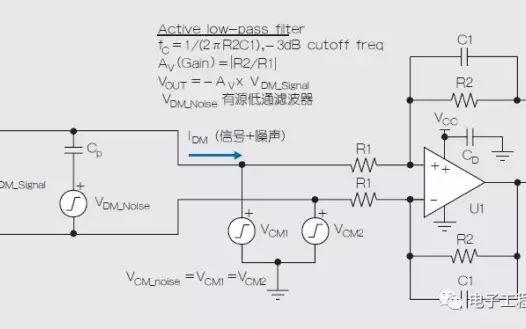

如果通過該走線提供10 A電流,則IR壓降約為500 mV(0.5 V),這是很大的。這意味著負載處的直流電源電壓比電源電壓低一半,而且還浪費了功率(I 2 R)和伴隨的散熱。請注意,壓降不是電源軌標稱電壓值的函數,它僅取決于電流和電阻。因此,一個15 V的電源軌的損耗與一個3 V的電源軌相同,但是在較低的電壓下,比例損耗要大得多。情況可能變得更糟。某些設計將低電阻接地層(通常作為獨立的PCB層)用于模擬和數字信號接地以及dc電源返回接地。但是,許多設計都受益于(或要求使用)信號和電源接地的單獨接地路徑,以降低噪聲,甚至可以使用單獨的直流回路。在這種情況下,IR壓降實際上增加了一倍,其中一個壓降使電源輸出軌負載,而第二個壓降使負載電流返回電源。

克服紅外壓降

設計人員有多種選擇可降低IR壓降:在中間總線轉換器(IBC)布置中使用較高電壓的直流電源軌,例如48 V或12/12 V dc,然后在靠近各自的位置放置多個本地負載點(PoL)dc-dc轉換器負載。這解決了IR下降問題(并且還大大減少了導軌中的噪聲吸收),但是卻增加了DC-DC轉換器和PCB面積的成本。盡管如此,它還是一種較多使用且有效的解決方案。調整直流標稱電源值以預補償IR壓降。這是一種有效的“解決方法”,但同時也帶來了一些風險。

-某些其他非常好或偏愛的耗材無法調節,因此必須排除在外。

-如果在使用過程中負載電流需求下降(幾乎總是如此),則IR下降也將下降,并且電源實際上可能會提供過高的電源電壓。

-如果必須在現場更換電源,則可能無法將補償設置為補償電壓或調整不當,從而導致電路無法正常工作或電路斷斷續續。

使用遠程感測,這是某些耗材支持的開爾文感測的一種變體。電源具有兩條額外的引線,因此,即使IR下降和負載發生漂移,它也可以檢測負載處的電壓并動態調整其輸出以保持該值。這是有效的,但也有缺點:

-傳感反饋回路的動態響應可能不夠快而無法補償,或者可能太快,過沖和振蕩。

-感測引線形成物理上較大的反饋環路,可能會吸收系統噪聲,從而導致電源誤讀所感測的值;再次,這甚至可能引起供電軌的振蕩。

考慮其他解決方案

所有這些選項都在使用中,并且它們都可以在定義明確且受控的條件下工作,但是它們都是“解決方法”和“補丁”,它們是從技術上更強大,更可靠的解決方案,其減少了跌落。同樣,還有選擇和權衡:

使用較厚的銅包層;2盎司 甚至3盎司 可用。厚度加倍會使電阻減半,但這樣做會增加原始PCB材料的成本并增加板重;將更多的銅放到不需要的地方;并且由于化學蝕刻或附加電鍍所需的額外時間而增加了制造時間,這是可以創建PCB銅路徑的兩種方式。

使用更寬的PCB走線;同樣,將寬度加倍會使阻力減半。但是,成本是這些直流電源軌及其接地回路的額外PCB“不動產”。一些先進的布局會盡可能使用較寬的走線,但也會通過縮小走線來避開板上的障礙物和狹窄的間隙區域。如果10厘米的行程僅在行程的一厘米處狹窄,則電阻的增加顯然僅發生在該短段上。

使用立式母線(也拼寫為母線或母線)來布線電源,從而使用未使用的z軸(高度)尺寸。即使該板是薄型SMT設計,通常也會留有相對較厚的薄型母線的凈空,因此它提供了低電阻的直流路徑。這些桿中有許多是作為兩層(或多層)結構提供的,一層用于一個或多個供電軌,另一層用于接地回路。成本只是BOM組件成本,對PCB本身的影響很小,因為它們不需要更厚的銅,更寬的走線或其他解決方法。

母線的厚度,高度層,引腳間距和長度范圍很廣。例如,E-Fab提供的一個母線具有兩個銅層,這些銅層被絕緣體隔開(圖2)。這些層具有交錯的PCB引腳配置,以便引腳交替供電和接地。

圖2

母線排提供了另一個“免費”的好處:它們使PCB變硬以防撓曲,這是大型板或在振動環境(軍用/航空,汽車和許多其他應用)中要考慮的問題。某些設計僅將母線用于較高電流的負載,例如MOSFET或IBGT。這樣可以降低其適度的成本,并減輕與電池條相關的布局問題(如果有),同時提高其有效性。

結論

從純電氣的角度來看,確保來自電源的全部標稱電壓到達負載,并以不明顯的IR電壓損耗或I 2R功耗達到負載,這對于可靠的非間歇性能至關重要。每個問題的解決方案都需要權衡,沒有標準答案,但是每個問題的缺點都應仔細理解和評估。

編輯:hfy

-

pcb

+關注

關注

4317文章

23007瀏覽量

396311 -

印刷電路板

+關注

關注

4文章

774瀏覽量

35108 -

DC-DC轉換器

+關注

關注

10文章

614瀏覽量

55514 -

總線轉換器

+關注

關注

0文章

9瀏覽量

9670

發布評論請先 登錄

相關推薦

PCB設計:降低噪聲與電磁干擾的24個竅門

講講電源壓降的一些問題

PCB設計的電源壓降是什么?

如何將手頭的Protel設計移植到Cadence PCB設計軟件中?

降低噪聲與電磁干擾的PCB設計24個竅門

使用3D Layout功能確定PCB上存在的壓降問題

PCB檢查-allegro PDN進行簡單電源直流壓降分析

電源DC壓降仿真分析流程詳解

通過PCB設計降低PCBA成本的方法

如何將Pytorch自訓練模型變成OpenVINO IR模型形式

怎么降低同軸分流器在等效串聯電感上的壓降對測量結果的影響呢?

PCB設計上如何將IR壓降降低

PCB設計上如何將IR壓降降低

評論