01

射頻板疊層結構

RF PCB單板的疊層結構除了要考慮射頻信號線的阻抗以外,還需要考慮散熱、電流、器件、EMC、結構和趨膚效應等問題,通常我們在多層印制板分層及堆疊中遵徇以下一些基本原則: A) RF PCB的每層都大面積鋪地,沒有電源平面,RF布線層的上下相鄰兩層都應該是地平面。 即使是數模混合板,數字部分可以存在電源平面,但是 RF 區仍然要滿足每層都大面積鋪地的要求。

B) 對RF雙面板來說,頂層為信號層,底層為地平面。 四層RF單板,頂層為信號層,第二層和第四層為地平面,第三層走電源、控制線。特殊情況在第三層可以走一些RF 信號線。更多層的RF單板,以此類推。 C) 對于RF背板來說,上下兩表面層都是地面,為了減小過孔及連接器的引起的阻抗不連續性,第二、三、四、五層走數字信號。 而其它靠底面的帶狀線層都是 底面 信號層。同樣,RF 信號層上下相鄰兩層該是地面,每層都應該大面積鋪地。

D) 對于大功率、大電流的射頻板應該將RF 主鏈路放置到頂層并且用較寬的微帶線連接。 這樣有利于散熱和減小能量損耗,減少導線腐蝕誤差。

E) 數字部分的電源平面應靠近接地平面,并且安排在接地平面之下。 這樣可以利用兩金屬平板間的電容作電源的平滑電容,同時接地平面還對電源平面上分布的輻射電流起到屏蔽作用。 具體疊層方法和平面分割要求可以參照EDA 設計部頒布的《20050818 印刷電路板設計規范——EMC 要求》,以網上標準為準。

02

射頻板布線要求

2.1 轉角

射頻信號走線如果走直角,拐角處的有效線寬會增大,阻抗不連續而引起反射。故要對轉角進行處理,主要為切角和圓角兩種方法。 (1) 切角適用于比較小的彎角,切角的適用頻率可達10GHz。

(2) 圓弧角的半徑應足夠大,一般來說,要保證:R>3W。

2.2 微帶線布線

PCB頂層走射頻信號,射頻信號下面的平面層必須是完整的接地平面,形成微帶線結構。要保證微帶線的結構完整性,有以下要求: (1) 微帶線兩邊的邊緣離下方地平面邊緣至少要有3W 寬度。且在3W 范圍內,不得有非接地的過孔。

(2) 微帶線至屏蔽壁距離應保持為2W 以上。(注:W 為線寬)。

(3) 同層內非耦合微帶線要做包地銅皮處理并在地銅皮上加地過孔,孔間距小于λ/20,均勻排列整齊。 地銅箔邊緣要光滑、平整、禁止尖銳毛刺。建議包地銅皮邊緣離微帶線邊緣大于等于1.5W的寬度或者3H的寬度,H 表示微帶襯底介質的厚度。

(4) 禁止 RF 信號走線跨第二層的地平面縫隙。

2.3 帶狀線布線

射頻信號有時要從PCB的中間層穿過,常見的為從第三層走,第二層和第四層必須是完整的接地平面,即偏心帶狀線結構。應保證帶狀線的結構完整性須要求:

(1) 帶狀線兩邊的邊緣離上下地平面邊緣至少3W寬度,且在3W范圍內,不得有非接地的過孔。

(2) 禁止RF帶狀線跨上下層的地平面縫隙。

(3) 同層內帶狀線要做包地銅皮處理并在地銅皮上加地過孔,孔間距小于λ/20,均勻排列整齊。地銅箔邊緣要光滑、平整、禁止尖銳毛刺。 建議包地銅皮邊緣離帶狀線邊緣大于等于1.5W的寬度或者3H的寬度,H 表示帶狀線上下介質層總厚度。

(4) 如果帶狀線要傳輸大功率信號,為了避免50歐姆線寬過細,通常要將帶狀線區域的上下兩個參考平面的銅皮做挖空處理,挖空寬度為帶狀線的總介質厚度的5倍以上,如果線寬仍然達不到要求,則再將上下相鄰的第二層參考面挖空。

-

連接器

+關注

關注

98文章

14326瀏覽量

136173 -

布線

+關注

關注

9文章

766瀏覽量

84294 -

射頻板

+關注

關注

0文章

5瀏覽量

6654

原文標題:細數射頻板疊層結構以及布線要求

文章出處:【微信號:gh_454737165c13,微信公眾號:Torex產品資訊】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

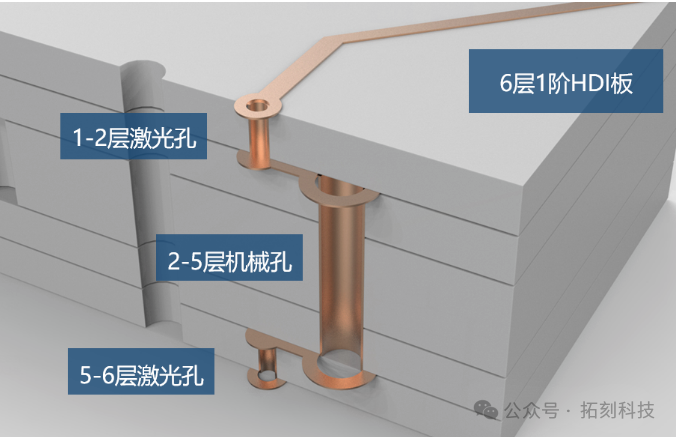

HDI的疊層結構設計

如何根據貼片疊層電感參數進行選型

PCB多層板為什么都是偶數層?奇數層不行嗎?

谷景揭秘貼片疊層電感精度是不是越高越好

鈣鈦礦疊層電池:Topcon與HJT底電池性能對比研究

PCB疊層結構與阻抗計算筆記分享

PCB疊層設計優化ESD性能設計

射頻板疊層結構及布線要求

射頻板疊層結構及布線要求

評論