I2C是一種同步,多主控,多從屬串行接口,允許微芯片相互通信。作為漏極開路/集電極開路的通信標準,即使集成電路使用不同的電壓軌,I2C也允許集成電路(IC)進行通信。

I2C標準的四種速度

I2C標準具有四種運行速度:

標準模式:100 kHz

快速模式:400 kHz

快速模式加:1 MHz

高速模式:3.4 MHz

I2C總線:串行數據和串行時鐘的 I2C總線使用兩根線串行數據(SDA)和串行時鐘(SCL) -和所有I2C主從設備僅通過這兩條線相連接。每個設備既可以是發射機,也可以是接收機。

SDA和SCL信號都是雙向的。每個器件的SDA和SCL引腳均為漏極開路引腳。它們具有連接到其的上拉電阻以獲得邏輯1。邏輯1取決于電源電壓;邏輯1取決于電源電壓。沒有標準的總線電壓。

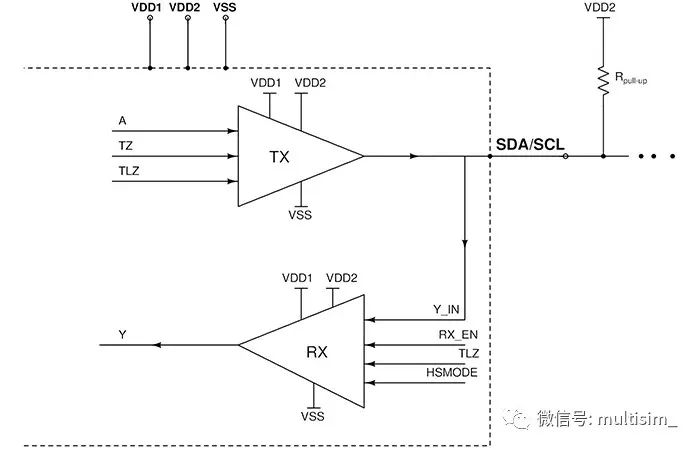

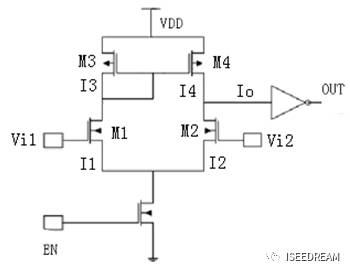

I2C細胞結構讓我們討論集成在IC中的I2CI / O單元結構。I2CI / O單元結構的框圖如圖1所示。

圖1.I2CI / O驅動器框圖在發送時間范圍內使能TX塊,而在接收時間范圍內使能RX塊。

VDD1和VDD2是主器件和從器件工作的兩個不同的電壓軌。VDD1是內部操作的芯片電源,而VDD2是外部系統使用的電源電壓。為了支持不同的電壓軌,需要一個電平轉換器將信號從一種電源電壓轉換為另一種電源電壓。

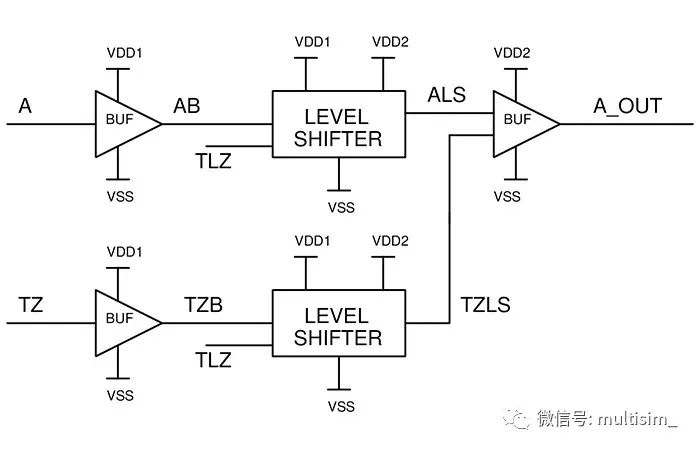

I2C模塊中的發送器電路發送器電路框圖如圖2所示。

圖2.發送器框圖

A是要在引腳SDA / SCL上發送出去的數據信號。VDD1掉電期間,TLZ是三態控制。TZ從VDD1移位到VDD2,以使能A_OUT的輸出漏極開路緩沖器。

如果在系統運行過程中有意或無意地使VDD1掉電,而VDD2仍處于活動狀態,則TZ使能信號變低或不確定。這可以使輸出緩沖器為A_OUT。

TLZ信號用作故障安全機制。TLZ在掉電期間被拉低,從而將TZ信號拉高。此時,不再啟用輸出緩沖區。當VDD1掉電時,漏極開路緩沖器將處于三態狀態。

要了解有關使用I2C緩沖器的用例,好處和應用的更多信息,請查閱AAC關于何時使用I2C緩沖器的技術文章。

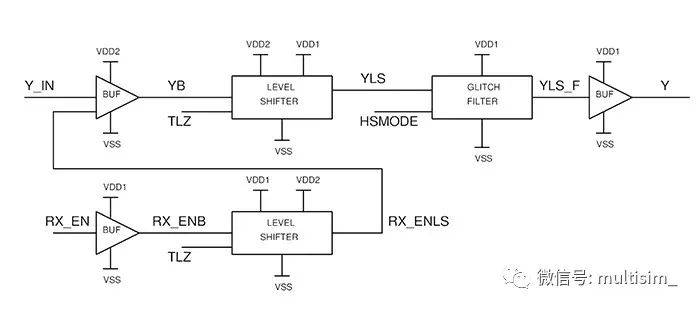

I2C模塊中的接收器電路接收器電路框圖如圖3所示。

圖3.接收器框圖

接收器電路通過RX_EN信號使能。TLZ具有與發射器塊相同的功能。HSMODE信號啟用高速模式。

RX_EN信號從VDD1到VDD2進行電平轉換,以使能接收Y_IN信號的緩沖器。然后,電平轉換器將緩沖的Y_IN信號移至VDD1電壓軌。

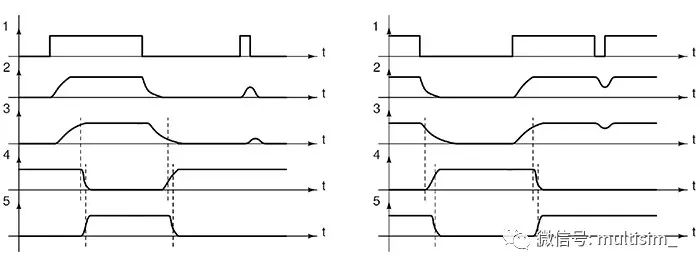

使用故障過濾器I2C信號容易受到噪聲和干擾。結果,您需要一個毛刺濾波器來濾除所有不需要的毛刺,并僅允許有效信號通過。在標準/快速模式下,<= 50ns的毛刺被抑制。在高速模式下,抑制毛刺<= 10ns。?

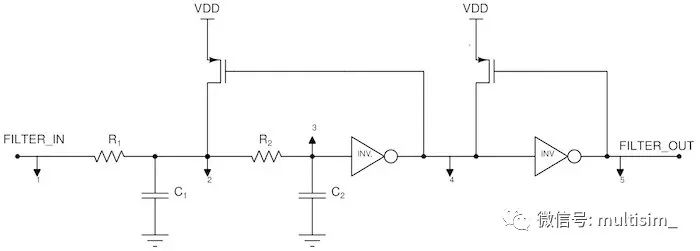

毛刺濾波器的設計如圖4所示,時序圖如圖5所示。

圖4.毛刺濾波器設計

圖5.毛刺濾波器的時序圖

RC時間常數會延遲通過信號并抑制任何毛刺。R1,C1,R2,C2的組合確定要抑制的毛刺的脈沖寬度。根據I2C規范,接收器應能夠抑制標準和快速模式下<= 50ns的毛刺脈沖,以及在高速模式下<= 10ns的毛刺脈沖。?

來自毛刺濾波器的輸出信號被緩沖,并被IC處理以進行進一步的操作。

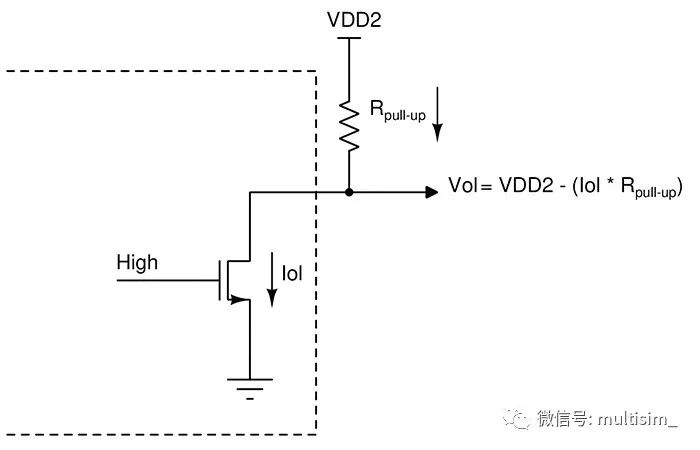

開漏配置的上拉電阻I2C線路上的輸出緩沖器采用漏極開路配置,我們將在有關I2C總線所需硬件的文章中對此進行詳細討論。任何I2C器件只能在這些I2C線上驅動低電平或使其處于三態。為了獲得邏輯高電平,需要在三態條件下將上拉電阻器將其拉至電壓軌。

當器件驅動為低電平時,這些上拉電阻通過NMOS汲取電流,如圖6所示。

圖6.開漏配置

上升時間取決于上拉電阻和寄生電容的時間常數,通常比下降時間更長,因為下降是由器件(即由NMOS)驅動的。因此,對于不同的工作速度,需要使用不同的上拉電阻。

責任編輯:xj

原文標題:設計集成電路I2C模塊的I / O驅動器

文章出處:【微信公眾號:multisim】歡迎添加關注!文章轉載請注明出處。

-

集成電路

+關注

關注

5365文章

11159瀏覽量

358339 -

I2C

+關注

關注

28文章

1452瀏覽量

122235

原文標題:設計集成電路I2C模塊的I / O驅動器

文章出處:【微信號:A1411464185,微信公眾號:multisim】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

遠程I/O模塊在不同領域的應用

PLC的I/O點數是什么意思

2.4GHz無線MCU芯片手冊解讀:Ci2451和Ci2454有何不同?

便攜儲能中種類豐富的I/O接口芯片

軟件可配置模擬 I/O 的設計理念

程序中USB的DP和DM IO配置為50Mhz,需要打開I/O補償單元來減少噪音嗎?

FANUC外部I/O點數不夠用了怎么辦?可以擴展I/O點數嗎?

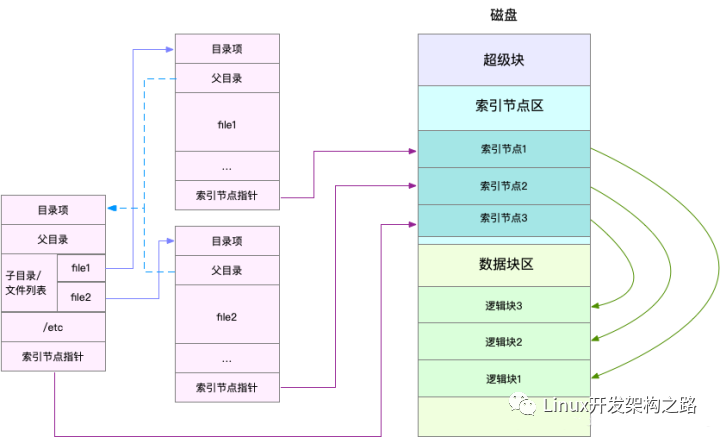

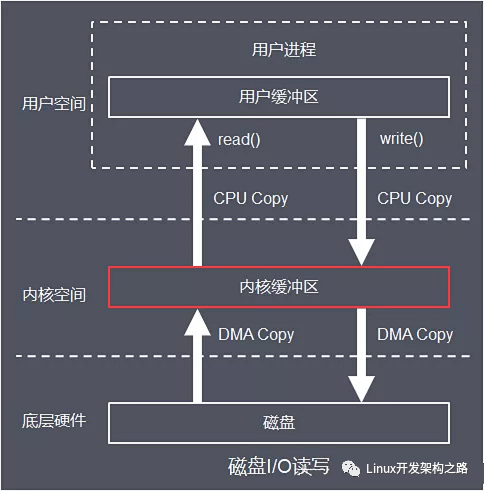

磁盤I/O是怎么工作的

集成在IC中的I2CI / O單元結構

集成在IC中的I2CI / O單元結構

評論