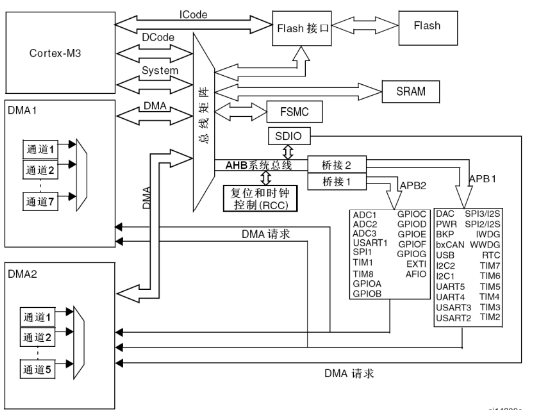

在小容量、中容量和 大容量產品中,主系統由以下部分構成:

● 四個驅動單元:

─ Cortex-M3內核DCode總線(D-bus),和系統總線(S-bus)

─ 通用DMA1和通用DMA2

● 四個被動單元

─ 內部SRAM

─ 內部閃存存儲器

─ FSMC

─ AHB到APB的橋(AHB2APBx),它連接所有的APB設備

這些都是通過一個多級的AHB總線構架相互連接的,如下圖所示:

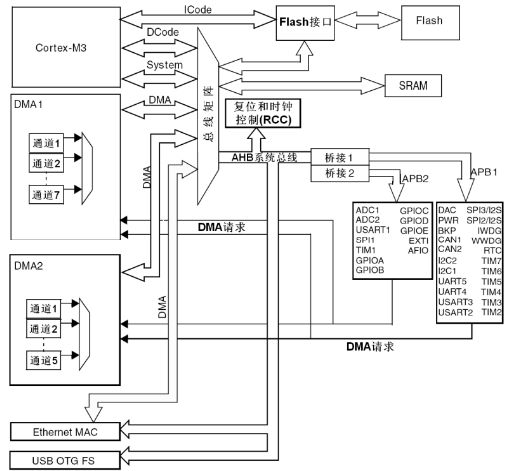

在互聯型產品中,主系統由以下部分構成:

● 五個驅動單元:

─ Cortex-M3內核DCode總線(D-bus),和系統總線(S-bus)

─ 通用DMA1和通用DMA2

─ 以太網DMA

● 三個被動單元

─ 內部SRAM

─ 內部閃存存儲器

─ AHB到APB的橋(AHB2APBx),它連接所有的APB設備

這些都是通過一個多級的AHB總線構架相互連接的,如下圖所示:

ICode總線

該總線將Cortex-M3內核的指令總線與閃存指令接口相連接。指令預取在此總線上完成。

DCode總線

該總線將Cortex-M3內核的DCode總線與閃存存儲器的數據接口相連接,常量加載和調試訪問。

系統總線

此總線連接Cortex-M3內核的系統總線(外設總線)到總線矩陣,總線矩陣協調著內核和DMA間的訪問。

DMA總線

此總線將DMA的AHB主控接口與總線矩陣相聯,總線矩陣協調著CPU的DCode和DMA到SRAM、閃存和外設的訪問。

總線矩陣

總線矩陣協調內核系統總線和DMA主控總線之間的訪問仲裁,仲裁利用輪換算法。在互聯型產品中,總線矩陣包含5個驅動部件(CPU的DCode、系統總線、以太網DMA、 DMA1總線和DMA2總線)和3個從部件(閃存存儲器接口(FLITF)、 SRAM和AHB2APB橋)。

在其它產品中總線矩陣包含4個驅動部件(CPU的DCode、系統總線、 DMA1總線和DMA2總線)和4個被動部件(閃存存儲器接口FLITF、 SRAM、 FSMC和AHB2APB橋)。

AHB外設通過總線矩陣與系統總線相連,允許DMA訪問。

AHB/APB橋(APB)

兩個AHB/APB橋在AHB和2個APB總線間提供同步連接。APB1操作速度限于36MHz, APB2操作于全速,最高72MHz。在每一次復位以后,所有除SRAM和FLITF以外的外設都被關閉,在使用一個外設之前,必須設置寄存器RCC_AHBENR來打開該外設的時鐘。當對APB寄存器進行8位或者16位訪問時,該訪問會被自動轉換成32位的訪問:橋會自動將8位或者32位的數據擴展以配合32位的向量。

-

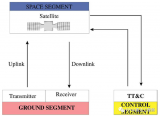

以太網

+關注

關注

40文章

5374瀏覽量

171094 -

存儲器

+關注

關注

38文章

7452瀏覽量

163598 -

STM32

+關注

關注

2266文章

10871瀏覽量

354789

原文標題:STM32系統架構

文章出處:【微信號:c-stm32,微信公眾號:STM32嵌入式開發】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

STM32項目實戰:基于STM32U5的智能大棚溫控系統(LVGL),附項目教程/源碼

STM32項目實戰:基于STM32U5的火災報警系統(LVGL),附項目教程/源碼

STM32項目實戰:基于STM32F4的智能燈光控制系統(LVGL),附項目教程/源碼

MES系統的功能、架構及應用價值

龍芯CPU統一系統架構規范及參考設計下載

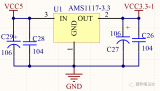

STM32單片機最小化系統設計原理

基于STM32的植物澆水系統開發

STM32系統架構

STM32系統架構

評論