目前,臺積電的2nm工藝已經提上日程。

而那邊,臺積電已經宣布了2nm工藝取得了重大突破,預計在2024年投入量產。

在失去華為這個重要客戶之后,臺積電并沒有像預想那樣受到影響,反倒依靠手里5nm工藝這張王牌,在市場上遙遙領先于競爭對手三星。

而在未來的芯片制程上,臺積電的研發進度也比預期來得快很多。

10nm、7nm、5nm、3nm、2nm……在摩爾定律進展放緩的同時,臺積電突破半導體工藝進步的腳步卻從未放慢。

5nm芯片、一顆要2900元

本月蘋果秋季發布會,沒了萬眾期待的iPhone 12系列,性能強大的A14處理器便成了主角。使用5nm制程工藝的A14到底有多強大——封裝118億個晶體管;性能比上一代提升40%;16核神經網絡引擎,每秒可執行11萬億次操作。

但在強大性能的背后,受制于5nm工藝的高成本和較低的成品率,5nm芯片的產能十分有限。媒體報道表示,今年臺積電最多只能代工7400萬顆A14處理器,這還是在動用全部5nm產能下能夠完成的數量。

在美國對華為制裁禁令的生效之后,臺積電已無法再為華為代工麒麟芯片,此前華為給臺積電的訂單是1500萬顆麒麟5nm芯片,但因為生產時間十分有限,最終也只在9月15日之前生產了880萬顆處理器,占據全部訂單的60%左右。在這之后,臺積電也將全部產能投入到A14處理器的生產中。

目前,臺積電每月僅能生產5萬片晶圓,這個產能遠遠不能滿足蘋果需求。

5nm芯片的成本到底有多高?

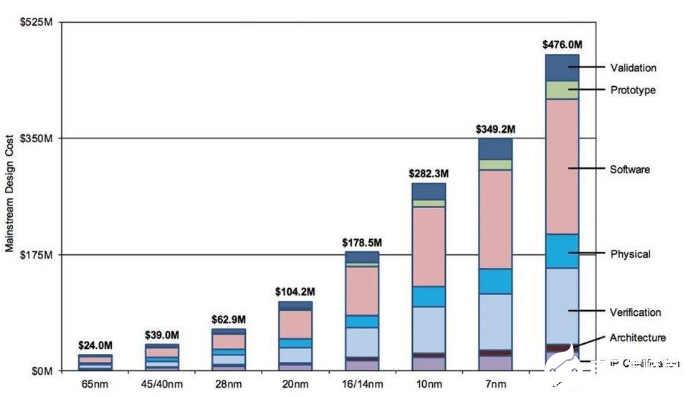

昂貴的設備和工藝成本,推動了芯片價格的上漲,這是無法避免的。正如2018年的時候,臺積電官方表示,預計在5nm工藝上總共投資了250億美元,其中5nm芯片設計成本將增至4.76億美元。也就是說,像設計一款A14或者麒麟5nm芯片,總成本可能高達近5億美元。

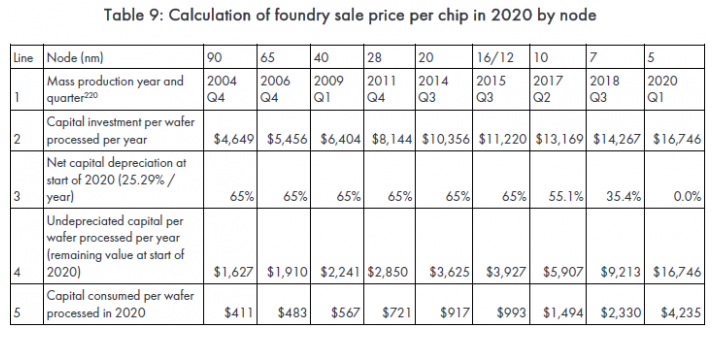

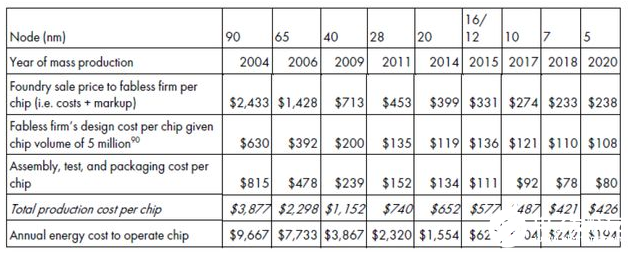

在美國研究機構CSET的兩位作者編寫的一份題為《AI Chips: What They Are and Why They Matter》的報告中,他們借助模型預估得出,臺積電5nm制造的12吋晶圓成本約為16988美元,遠高于7nm約為9346美元的成本。

如果換算成單顆5nm芯片的制造成本,同樣也十分昂貴。每片300mm直徑的晶圓只可以制造71.4顆5nm芯片,平攤單顆芯片成本將高達238美元(約合1600元人民幣)。

報告以英偉達P100 GPU為例,這款產品采用臺積電的16nm節點處制造,包含了153億個晶體管,裸片面積為610平方毫米。

事實上這還只是晶圓制造成本,而一顆芯片的誕生還需要包含設計成本和封裝、測試成本,這部分的成本也是非常高的,每顆芯片的設計和封裝、測試成本,分別為108美元和80美元。

如果這份研究報告的準確性高的話,那么意味著一顆5nm芯片支付的總成本將可能達到426美元(約為2929元)。

當然,這么估算也只是最理想的狀態,考慮到5nm工藝才開始正式量產,所以可能會有比較高的損耗,同時光刻機的成本也極高,因為要重度依賴極紫外光EUV技術,而一臺EUV光刻機的價格高達1.2億美元。

實際上麒麟9000的成本可以并不需要這么多。此前有人透露,12吋晶圓大概能夠切割出400顆麒麟9000芯片。若按此計算,單顆制造成本為42美元,約合287元人民幣,加上設計和封裝、測試成本,一顆芯片的最終成本可能在230美元左右,也就是1570元人民幣。

但不可否認,今年蘋果和華為的旗艦機注定不會再便宜。

未來,瞄準更先進制程

市場研究機構International Business Strategies (IBS)給出的數據顯示,28nm之后芯片的成本迅速上升。28nm工藝的成本為0.629億美元,到了7nm和5nm,芯片的正本迅速暴增,5nm將增至4.76億美元。三星稱其3nm GAA 的成本可能會超過5億美元。

并且,隨著半導體復雜性的增加,對高端人才的需求也不斷增長,這也進一步推高了先進制程芯片的成本。報告中指出,研究人員的有效數,即用半導體研發支出除以高技能研究人員的工資,從1971年到2015年增長了18倍。

換句話說,摩爾定律延續增加大量的投入和人才。

為了支撐先進制程,臺積電十年內研發人數增加了三倍,2017年研發人員將近6200人,比2008年多了近兩倍,這6200人只從事研發,不從事生產。

從臺積電的消息還顯示,接下來其將繼續完善推進相應技術。

目前,臺積電披露了旗下的又一大新研發進展,即3nm工藝。這一工藝臺積電去年就開始著手,目前進展順利。

與5nm相比,3nm可以在相同的功率水平下提高10-15%的性能,或者在相同的晶體管速度下降低25-30%的功率。其計劃在2021年進入風險生產,2022年下半年進入量產。

臺積電在2nm半導體制造節點方面取得重大研究突破,有望在2023年中期進入2nm工藝試生產階段,并在一年后開始批量生產。目前,臺積電的最新制造工藝是5nm工藝,已用于生產A14仿生芯片。

據悉,臺積電的2nm工藝將采用差分晶體管設計,采用環繞閘極(GAA)制程為基礎的MBCFET架構,解決FinFET因制程微縮產生電流控制漏電的物理極限問題。而在極紫外光微顯影技術方面的進步讓臺積電的 納米片(Nano Sheet)堆疊關鍵技術更為成熟,良品率的提升比預期的順利許多。

該設計被稱為多橋溝道場效應(MBCFET)晶體管,它是對先前FinFET設計的補充。值得注意的是,這也是臺積電第一次將MBCFET設計用于其晶體管。

臺積電一位高管對外表示,“我們樂觀預計2023年下半年風險試產收益率將達到90%,這將有助于我們未來繼續贏得蘋果、匯達等主要廠商的大訂單”。同時,他還提到,量產將于2024年開始。

臺積電去年成立了2nm項目研發團隊,尋找可行的發展路徑。考慮到成本、設備兼容性、技術成熟度和性能等條件,2nm采用了基于環繞門(GAA)工藝的MBCFET。

該結構解決了FinFET工藝收縮引起的電流控制泄漏的物理限制。

這方面最早的仍然是三星,三星已經準備在 3nm 工藝的時候引入 GAA 技術。基于全新的GAA晶體管結構,三星通過使用納米片設備制造出了MBCFET(Multi-Bridge-Channel FET,多橋-通道場效應管),3nm 工藝可將核心面積減少 45%,功耗降低 50%,性能提升 35%。

至于臺積電,最新消息顯示,臺積電很有可能在 2nm 的時候在引入 GAA 技術。根據 Digitimes 報道,臺積電 2nm GAA 工藝研發進度提前,目前已經結束了路徑探索階段。

責編AJX

-

臺積電

+關注

關注

44文章

5609瀏覽量

166112 -

摩爾定律

+關注

關注

4文章

632瀏覽量

78930 -

晶圓

+關注

關注

52文章

4839瀏覽量

127795

發布評論請先 登錄

相關推薦

3nm、2nm……在摩爾定律進展放緩時,臺積電突破的腳步卻從未放慢

3nm、2nm……在摩爾定律進展放緩時,臺積電突破的腳步卻從未放慢

評論