幾十年來使用的三種最常見的多線串行數據傳輸格式是I2C,UART和SPI。本文著眼于串行外設接口(SPI)總線,該總線已擺脫了顯式的標準化,因此在實現協議之前,請始終檢查要使用的集成電路的數據表。

能力和特點

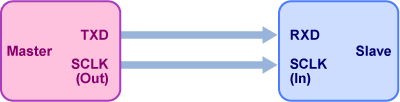

串行外圍設備接口總線使用四個數據線在主設備和從設備之間提供全雙工同步通信。

基本主從配置

串行外設接口允許將數據位從主設備移出到從設備中,同時,還可以將位從從設備移出到主設備中。

動畫1顯示了數據從microchipA移入microchip B,又從Microchip B移入MicrochipA。

動畫2顯示了兩個微芯片之間SPI事務的虛擬4通道示波器軌跡。由馬克·休斯(Mark Hughes)用Mathematica創建

由于SPI尚未標準化,因此可能會遇到先傳輸最高有效位(MSb)或最低有效位(LSb)的情況。檢查設備的數據表并相應地設置數據處理例程。如果您使用的是Arduino,則可以參考此頁面以獲取有關配置SPI端口的信息。

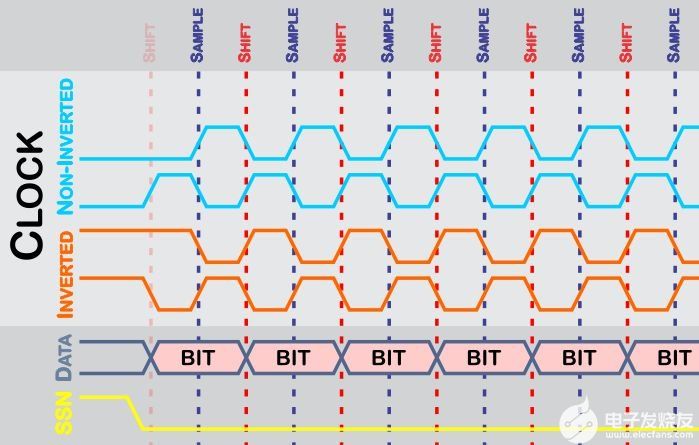

時鐘極性和相位

時鐘轉換控制數據的移位和采樣。SPI具有四種模式(0、1、2、3),分別對應四種可能的時鐘配置。

在時鐘周期的上升沿采樣的位在時鐘周期的下降沿移出,反之亦然。

當從選擇線被驅動至邏輯低電平(從選擇通常為低電平有效信號)時,每個事務開始。從選擇線,數據線和時鐘線之間的確切關系取決于如何配置時鐘極性(CPOL)和時鐘相位(CPHA)。

在時鐘極性不變的情況下(即,當從器件選擇轉換為邏輯低電平時,時鐘處于邏輯低電平):

模式0:配置時鐘相位,以便在時鐘脈沖的上升沿采樣數據,并在時鐘脈沖的下降沿移出數據。這對應于上圖中的第一個藍色時鐘軌跡。注意,數據必須在時鐘的第一個上升沿之前可用。

模式1:配置時鐘相位,以便在時鐘脈沖的下降沿采樣數據,并在時鐘脈沖的上升沿移出數據。這對應于上圖中的第二條藍色時鐘軌跡。

在時鐘極性反轉的情況下(即,當從器件選擇轉換為邏輯低電平時,時鐘處于邏輯高電平):

模式2:配置時鐘相位,以便在時鐘脈沖的下降沿采樣數據,并在時鐘脈沖的上升沿移出數據。這對應于上圖中的第一個橙色時鐘軌跡。注意,數據必須在時鐘的第一個下降沿之前可用。

模式3:配置時鐘相位,以便在時鐘脈沖的上升沿采樣數據,并在時鐘脈沖的下降沿移出數據。這對應于上圖中的第二個橙色時鐘軌跡。

關鍵參數

CLK:串行時鐘。由主設備控制。每個時鐘周期都會移出一個新的數據位。

SSN:從機選擇(“ N”將其標識為低電平有效信號)。由主設備控制。激活的從設備選擇線指示主機正在向相應的從設備發送數據或從其請求數據。

MOSI:主輸出?從輸入。數據離開主設備并進入從設備。芯片A上的MOSI線連接到芯片B上的MOSI線。

MISO:主機輸入?從機輸出。數據離開從設備并進入主設備(或以菊花鏈配置的另一個從設備;請參閱下一節)。芯片A上的MISO線連接到芯片B上的MISO線。

CPOL:時鐘極性。這支配時鐘信號的初始邏輯狀態。有關更多信息,請參考上一節。

CPHA:時鐘相位。這支配了數據轉換和時鐘轉換之間的關系。有關更多信息,請參考上一節。

從選擇和菊花鏈

多從選擇配置

在標準的SPI安排中,主設備可以通過啟用設備(即,將相應設備的從選擇線設置為邏輯低電平)向共享公共數據線的單個設備寫入數據或向其請求數據。注意不要同時啟用多個從站,因為返回到主站的數據將由于MISO線之間的驅動程序爭用而損壞。某些應用程序不需要將數據返回給主服務器;在這種情況下,如果主機希望將相同的數據發送到多個從機,則可以同時尋址多個從機。

在多從站選擇配置中,每個從站都需要來自主站的唯一從站選擇線。如果主站沒有足夠的I / O引腳來滿足所需數量的從站,則可以通過合并解碼器/多路分解器來實現I / O擴展,例如74HC(T)238(PDF)(3至8行)解碼器/解復用器)。

菊花鏈配置

在此配置中,數據從一臺設備移動到另一臺設備。最終的從設備可以將數據返回給主設備。

在菊花鏈配置中,所有從機共享一條公共的從機選擇線。數據從主機轉移到第一個從機,然后從第一個從機轉移到第二個,依此類推。數據沿線級聯直至該系列中的最后一個從機,然后可以使用其MISO線將數據發送到主設備。

這種配置非常適合節日期間流行的可單獨尋址的LED燈串。

結論

串行外設接口已經存在了數十年,沒有理由期望它會很快消失。雖然I 2 C和UART可能會更受歡迎,但SPI是一種通用且直接的串行通信接口,非常適合某些應用。

-

SPI

+關注

關注

17文章

1701瀏覽量

91345

發布評論請先 登錄

相關推薦

scsi接口是串行還是并行

串行接口PCB設計指南:優化布局與布線策略

串行接口與并行接口的區別

串行接口的工作原理和結構

TUSB2046x 4端口集線器,用于帶可選串行EEPROM接口的通用串行總線數據表

串行音頻接口(SAI)中slot是什么意思?

什么是I2C接口?什么是I3C接口?I2C與I3C的區別

串行外圍接口簡介

串行外圍接口簡介

評論