來源:互聯(lián)網(wǎng)

在電路中加上拉電阻或下拉電阻的目的是確定某個狀態(tài)電路中的高電平或低電平。

上、下拉電阻的作用

提高電路穩(wěn)定性,避免引起誤動作。一些情況下按鍵如果不通過電阻上拉到高電平,那么在上電瞬間可能發(fā)生誤動作,因為在上電瞬間單片機的引腳電平是不確定的,上拉電阻R12的存在保證了其引腳處于高電平狀態(tài),而不會發(fā)生誤動作。

提高輸出管腳的帶載能力。受其他外圍電路的影響單片機在輸出高電平時能力不足,達不到VCC狀態(tài),這會影響整個系統(tǒng)的正常工作,上拉電阻的存在可以使管腳的驅(qū)動能力增強。這里特別強調(diào)如下:帶片上I2C資源的單片機,其SCL和SDA引腳是開漏引腳,如果當做普通的GPIO來用的話,你會發(fā)現(xiàn)該引腳輸出高電平極不穩(wěn)定甚至因為負載的關系都無法正常輸出高電平,這時候需要在這兩個引腳上加上拉電阻了。

下面舉幾個例子進行講解:

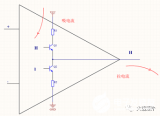

按鍵檢測中的上拉電阻

增加上拉電阻的目的是使當按鍵斷開時,KeyIn1處于高電平狀態(tài),若無上拉,懸空,狀態(tài)無法確定。斷開為1,閉合為0,數(shù)字邏輯關系明確。

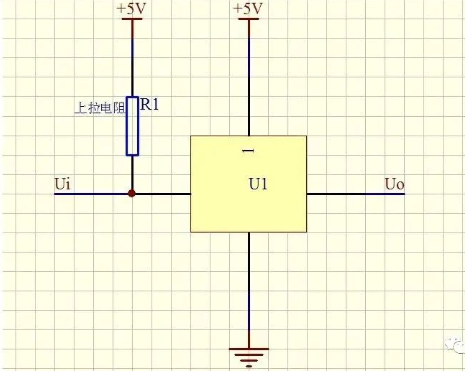

比較器輸出加上拉電阻

當比較器反相輸入端電壓>同相輸入端電壓時,比較器輸出低電平(地),沒問題;

當比較器反相輸入端電壓<同相輸入端電壓時,若無上拉電阻,比較器是不會輸出高電平的,而是相當于懸空狀態(tài)的導線,只有增加上拉電阻才會輸出高電平。

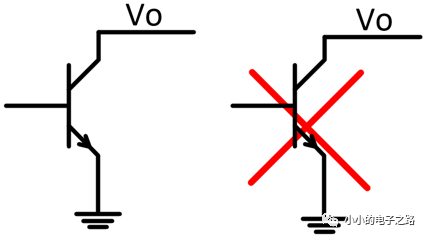

三極管、MOS管等控制端上拉或下拉

三極管和MOS管當開關使用時,控制端加上拉或下拉電阻的目的是當沒有輸入信號時,使控制極處于穩(wěn)定電平狀態(tài),確保三極管或MOS管截止。

還有處理器IO口、光耦輸出、某些反相器等增加上拉或下拉電阻的目的也是一樣的,為了確定電平狀態(tài),減少干擾和誤差。

審核編輯 黃昊宇

-

上拉電阻

+關注

關注

5文章

351瀏覽量

30406 -

下拉電阻

+關注

關注

4文章

143瀏覽量

20403 -

電路設計

+關注

關注

6629文章

2376瀏覽量

200194

發(fā)布評論請先 登錄

相關推薦

下拉電阻的作用有哪些

最全講解上下拉電阻 上下拉電阻的選擇與上下拉電阻的應用

上拉電阻和下拉電阻是什么

電阻是如何實現(xiàn)上下拉功能的呢?

電路板中上拉電阻和下拉電阻所起的作用

AD1674想獲得一個穩(wěn)定的輸出狀態(tài),能否加上10k下拉電阻?

電阻上下拉功能實現(xiàn)原理詳解

如何計算IC內(nèi)部的上拉/下拉電阻值?

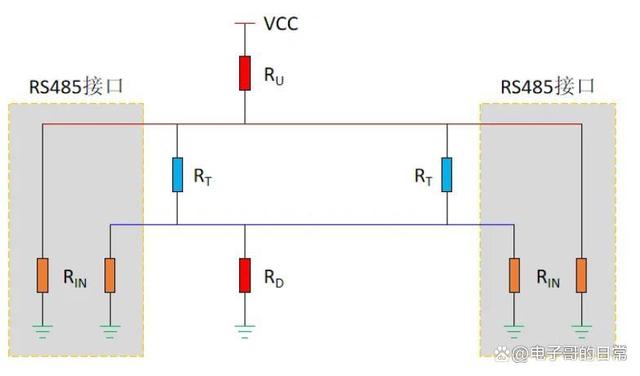

RS485為什么要加上下拉電阻?

科普:電路設計為什么要加上、下拉電阻

科普:電路設計為什么要加上、下拉電阻

評論