任正非,這個70余歲的老人,在過去的幾十年中一直比較低調、不怎么輕易公開發言,但在2019年后遇到難以想象的生存困境后,他接受了國內外總計37次媒體專訪,自華為1987年成立以來的前31年里,任正非有官方記錄的采訪僅為6次,這反差著實巨大。

但是在即將過去的2020年里,任正非似乎又開始逐漸淡出公共媒體,據華為心聲論壇記錄,自3月開始,任正非就再未接受過媒體的采訪,這位老人的行蹤我們只能從他的公開發言中去探索和找尋。

騰訊科技梳理了任正非2020年的公開演講,數據分析了他近10萬字演講和回答,挑選了其中的高頻詞匯,希望借此一窺這位華為掌門人在2020年都有哪些態度和改變呢?

這里的重點高頻詞匯是什么意思?這里的高頻詞匯主要來自兩個渠道,一是被提問,二是任正非主動提及。一邊是代表著媒體和社會的關注點,一邊代表任正非和華為的聚焦點。

“美國”是回答中出現最多的詞

在任正非的所有回答中,“美國”是出現頻次最多的國家名(200次),其次是“中國”(75次),這也可以看出過去幾年中美國和華為之間的“恩怨糾葛”。

“技術”在任正非的話語中出現次數排在前三,結合“發展”、“戰略”、“學習”等關鍵詞來看,在2020年,技術發展已經成為華為堅定的目標方向。

新的時代更加重視基礎教育和學習

從華為200萬年薪招聘天才少年,到幾乎把C9聯盟高校跑了個遍,2020年的任正非似乎更將重心放在了下一代中。

學習、人才、教育、開放也是任正非今年提及多次的字眼,從中也可以看出任正非對于走開放道路、堅持合作的愿望和決心,也表示未來的華為將更多心力傾注于人才培養及自主創新之上。

華為被斷供以前,任正非曾在7月29日至7月31日連續訪問4所院校,依次是上海交通大學、復旦大學、東南大學和南京大學,在11月更是連跑清華北大,并邀約各院校去華為參觀,與院校專家進行了座談,期間,任正非多次表示希望加深校企合作,將科研與產業深度融合,培育基礎研究人才等。他在上海交通大學說,希望大學像“燈塔”,照亮自己,也照亮別人;他在復旦大學說:未來我們拼什么,就是拼教育、拼人才;他在東南大學說:教授甘坐冷板凳,這就是中國的希望。

而華為的“天才少年”計劃,也從側面驗證了這個事實。任正非曾在華為內部講話中說過,將從全世界招進20~30名的“天才少年”,并對2019屆頂尖學生實行了年薪制管理,這批入職的8位頂尖學生都是博士,年薪最低89.6萬元,最高201萬元。

技術助力芯片自主、計算戰略等

從任正非所探訪的大學學科背景來看,任正非此行或有意為華為人工智能、計算戰略、芯片自主等鋪路。

據公開信息,上海交通大學在計算機領域有獨特優勢,知名機構發布統計數據顯示,2019年中國躋身世界大學計算機排名前4的高校分別是:清華大學(第20名)、北京大學(第32名)、浙江大學(第45名)和上海交通大學(第49名),特別是近年來交大在人工智能領域發展迅猛。

從關鍵詞背后的隱藏屬性來看,5G、現代化、芯片、人工智能等詞也“順利”進入到了前列。

更重要的,在任正非與各高校的溝通中,透露出兩個重要信號:其一,上海將成為華為發展的重要戰略之地;其二,華為正計劃通過高校等挖掘、儲備各業務領域人才,助力芯片自主、人工智能產業壯大等。

如今華為因為各種國際局勢變動,勢必要走全面的自主自研自產之路,所以必須有大量的人才儲備,才能有實現這一道路的可能。

任正非說,對未來的不確定性,可以從孩子們的教育抓起,中國的未來與振興要靠孩子,靠孩子唯有靠教育。“多辦一些學校,實行差別教育,啟發他們的創新精神,就會一年比一年有信心,一年一年地逼近未來世界的大門”。

任正非的2020,背后潛藏著的其實是一顆布局未來,蓬勃發展的雄心。

編輯:hfy

-

人工智能

+關注

關注

1791文章

46896瀏覽量

237667 -

任正非

+關注

關注

6文章

271瀏覽量

31015 -

騰訊科技

+關注

關注

0文章

11瀏覽量

2868 -

鴻蒙系統

+關注

關注

183文章

2634瀏覽量

66224

發布評論請先 登錄

相關推薦

digiPCBA元件庫下載(轉化)本地,下載后的集成庫信息無法批量隱藏屬性信息

科技看點:任正非回應華為員工提問 蔚來回應建立中東團隊 英特爾股價盤后大漲15%

淺析2024年半導體行業的兩大關鍵詞

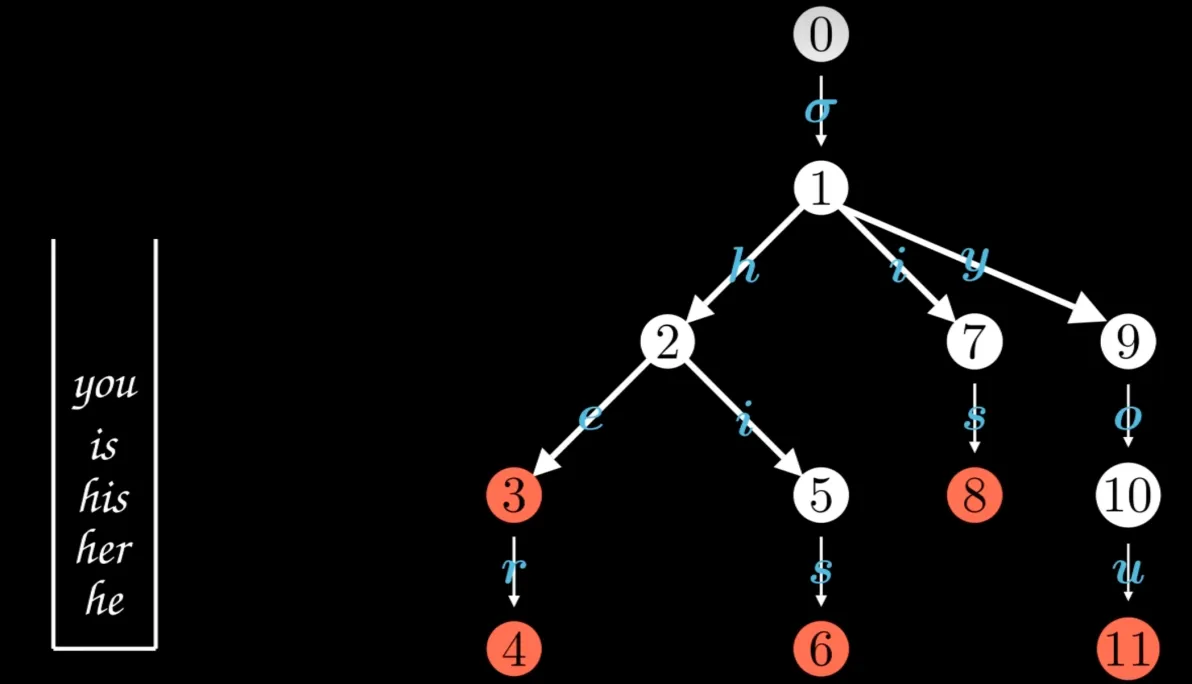

探索AC自動機:多關鍵詞搜索的原理與應用案例

中國信通院發布“2024云計算十大關鍵詞”

全網熱搜的關鍵詞,芯訊通也被@了

微軟Edge瀏覽器將引入PDF閱讀器,實現關鍵詞自動生成功能

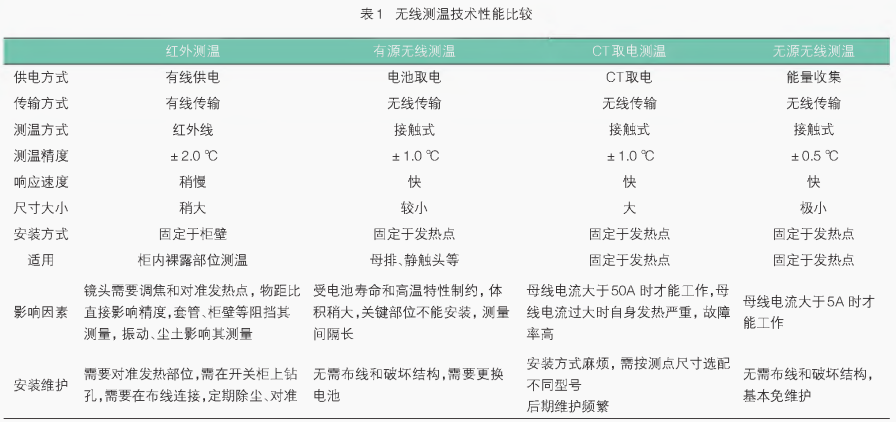

淺談無線測溫系統在電廠的研究和應用

深開鴻用三個關鍵詞,為你解讀《2023 OpenHarmony 年度運營報告》

西門子博途:塊屬性- 隱藏塊參數

淺談任正非關鍵詞背后的隱藏屬性

淺談任正非關鍵詞背后的隱藏屬性

評論