該篇將分析對(duì)象限定為一個(gè)DAC,其中的輸出緩沖器在正常模式下被加電:零量程或中量程。文章將分析一下DAC輸出在高阻抗模式中被加電的情況。同時(shí)提出一個(gè)針對(duì)加電毛刺脈沖的數(shù)學(xué)模型,隨后給出一個(gè)盡可能減少此毛刺脈沖的電路板級(jí)解決方案。

原理

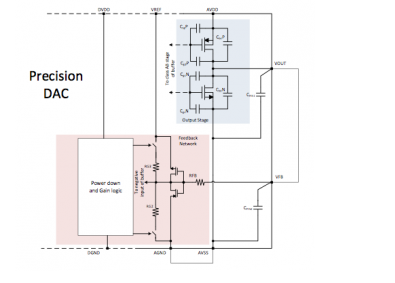

圖1:DAC8760高精度DAC輸出級(jí)

這個(gè)分析與沒有加電毛刺脈沖減少 (POGR) 電路的DAC有關(guān)。第一部分列出了影響加電毛刺脈沖的因素。當(dāng)DAC在電源斜升期間加電至高阻抗模式時(shí),這個(gè)加電毛刺脈沖也可被視為一個(gè)在DAC的電壓輸出 ( ) 引腳上逐步累積形成的瞬態(tài)電荷。這個(gè)電荷積聚是由電源引腳,通過芯片內(nèi)部和外部的寄生電容,到

) 引腳上逐步累積形成的瞬態(tài)電荷。這個(gè)電荷積聚是由電源引腳,通過芯片內(nèi)部和外部的寄生電容,到 引腳的電容耦合造成的。需要注意的是,與加電毛刺脈沖相比(第一部分),這個(gè)毛刺脈沖本質(zhì)上說是AC毛刺脈沖。因此,它的幅度取決于電源斜升時(shí)間。在大多數(shù)多電源芯片中,數(shù)字電源和基準(zhǔn)引腳有一個(gè)到

引腳的電容耦合造成的。需要注意的是,與加電毛刺脈沖相比(第一部分),這個(gè)毛刺脈沖本質(zhì)上說是AC毛刺脈沖。因此,它的幅度取決于電源斜升時(shí)間。在大多數(shù)多電源芯片中,數(shù)字電源和基準(zhǔn)引腳有一個(gè)到 引腳比較弱的寄生路徑。因此,這些引腳不是造成加電/斷電毛刺脈沖的主導(dǎo)原因。

引腳比較弱的寄生路徑。因此,這些引腳不是造成加電/斷電毛刺脈沖的主導(dǎo)原因。

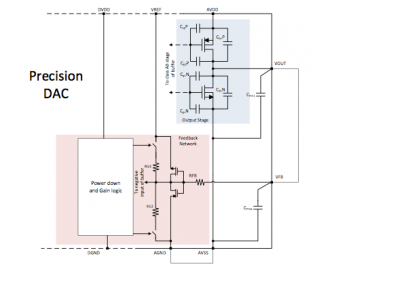

圖2:高精度DAC輸出級(jí)模型

DAC輸出級(jí)中的NFET/PFET晶體管的尺寸要遠(yuǎn)遠(yuǎn)大于其它開關(guān),這是因?yàn)檫@個(gè)輸出級(jí)被設(shè)計(jì)用于特定的負(fù)載驅(qū)動(dòng)。因此,這些FET的寄生電容要遠(yuǎn)高于其它片上組件的寄生電容。圖1顯示的是一個(gè)典型高精度DAC輸出級(jí) (DAC8760) 的簡(jiǎn)化圖。在這個(gè)圖中,假定輸出級(jí)和芯片的數(shù)字內(nèi)核分別具有單獨(dú)的電源。反饋節(jié)點(diǎn)上放置的二極管用來保護(hù)增益/斷電網(wǎng)絡(luò)中的晶體管。

數(shù)學(xué)分析

如圖所見,進(jìn)入 引腳的主要寄生電容是VOUT 結(jié)合線、引線和輸出FET的寄生電容的組合值。在這個(gè)假設(shè)下,DAC輸出引腳可被建模為一個(gè)簡(jiǎn)單的電容分壓器。圖2中的經(jīng)簡(jiǎn)化模型在反饋節(jié)點(diǎn)和VREF/AGND之間使用2個(gè)二極管。由于這些二極管代表了一個(gè)FET(圖1),在以后的分析中,這些二極管上的壓降可被忽略不計(jì)。

引腳的主要寄生電容是VOUT 結(jié)合線、引線和輸出FET的寄生電容的組合值。在這個(gè)假設(shè)下,DAC輸出引腳可被建模為一個(gè)簡(jiǎn)單的電容分壓器。圖2中的經(jīng)簡(jiǎn)化模型在反饋節(jié)點(diǎn)和VREF/AGND之間使用2個(gè)二極管。由于這些二極管代表了一個(gè)FET(圖1),在以后的分析中,這些二極管上的壓降可被忽略不計(jì)。

被放置在反饋節(jié)點(diǎn)與VREF/GND之間的反饋電阻器 (RFB) 和FET限制了毛刺脈沖數(shù)量級(jí)的上限和下限。在這個(gè)條件下,可被觀察到的最大加電/斷電毛刺脈沖被限制在VREF和GND之間。

盡可能減少加電/斷電毛刺脈沖

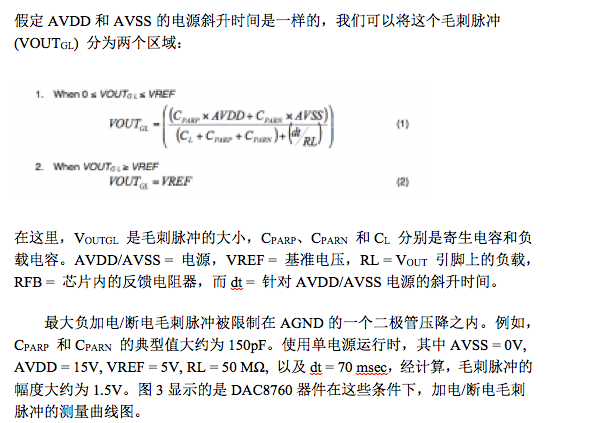

圖3:DAC8760 VOUT加電毛刺脈沖,無負(fù)載。

讓我們來深入研究一下盡可能減少加電/斷電毛刺脈沖的一些方法。在方程式 (1) 和 (2) 中,我們看到這些方程式中的某些項(xiàng)是常量。例如,寄生電容是器件寄生效應(yīng)的函數(shù)。電源電壓由應(yīng)用需求決定。斜升時(shí)間由電源設(shè)計(jì)確定。剩下的數(shù)據(jù)項(xiàng)只有相對(duì)于電源的負(fù)載阻抗和VREF的排序。這就形成了減少加電/斷電毛刺脈沖的2個(gè)主要方法:電源排序與負(fù)載。

電源排序

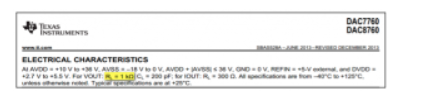

圖4:數(shù)據(jù)表技術(shù)規(guī)格示例

電源排序是指以特定的順序,用不同的電源為芯片加電/斷電。對(duì)于DAC8760來說,由于加電/斷電毛刺脈沖直接與VREF成比例,在AVDD/AVSS之后為VREF加電可以極大地減少這個(gè)毛刺脈沖。這個(gè)解決方案可以在對(duì)電源和基準(zhǔn)電壓進(jìn)行單獨(dú)控制時(shí)使用。

外部阻性負(fù)載

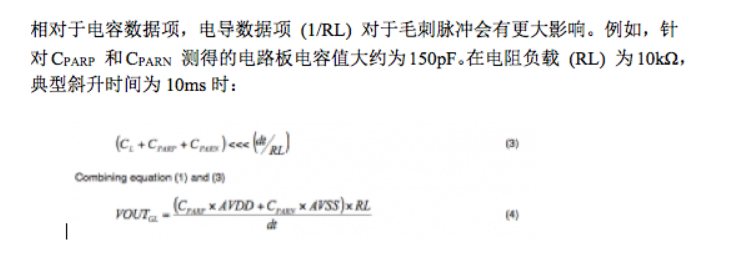

方程式 (1) 中的分母由一個(gè)電容數(shù)據(jù)項(xiàng) (CPARP + CPARN + CL) 和一個(gè)電導(dǎo)數(shù)據(jù)項(xiàng) (1/RL) 組成。這就形成了幾個(gè)盡可能減少毛刺脈沖的方法:增加電容負(fù)載 (CL)、或者減少阻性負(fù)載 (RL)。增加電容負(fù)載會(huì)對(duì)整個(gè)系統(tǒng)的帶寬產(chǎn)生不利影響。它還會(huì)影響輸出放大器的穩(wěn)定性。因此,不建議使用這個(gè)方法來實(shí)現(xiàn)毛刺脈沖最小化。

在選擇使用一個(gè)小值阻性負(fù)載時(shí),方程式 (4) 可以將加電/斷電毛刺脈沖數(shù)量級(jí)減少到mV以下級(jí)別。這會(huì)導(dǎo)致大電流流經(jīng)輸出緩沖器,從而使 精度技術(shù)規(guī)格降級(jí),比如說偏移、增益、線性等。因此,要根據(jù)數(shù)據(jù)表技術(shù)規(guī)格來選擇

精度技術(shù)規(guī)格降級(jí),比如說偏移、增益、線性等。因此,要根據(jù)數(shù)據(jù)表技術(shù)規(guī)格來選擇 引腳上的阻性負(fù)載。例如,DAC8760數(shù)據(jù)表規(guī)定了負(fù)載為1k?時(shí)的精度參數(shù)(圖4)。

引腳上的阻性負(fù)載。例如,DAC8760數(shù)據(jù)表規(guī)定了負(fù)載為1k?時(shí)的精度參數(shù)(圖4)。

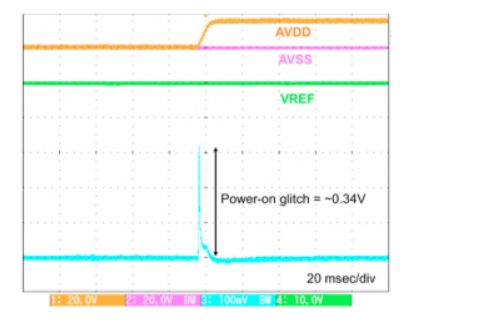

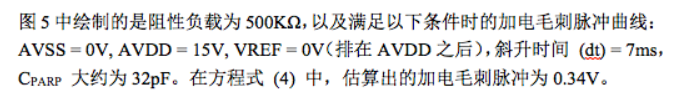

圖5:DAC8760  加電毛刺脈沖 – RL = 500K?

加電毛刺脈沖 – RL = 500K?

結(jié)論

加電/斷電毛刺脈沖對(duì)系統(tǒng)十分有害。它們的影響只有在系統(tǒng)設(shè)計(jì)好、進(jìn)行測(cè)試時(shí)才會(huì)顯現(xiàn)出來。因此,有一點(diǎn)很關(guān)鍵,那就是通過仔細(xì)檢查組件,并使用這篇文中給出的技巧來設(shè)計(jì)系統(tǒng),以盡可能減少這些毛刺脈沖。我們已經(jīng)討論了形成這些毛刺脈沖的根本原因,并且提出了一個(gè)盡可能減少這些毛刺脈沖的板級(jí)解決方案。

編輯:hfy

-

二極管

+關(guān)注

關(guān)注

147文章

9576瀏覽量

165948 -

dac

+關(guān)注

關(guān)注

43文章

2272瀏覽量

190848 -

晶體管

+關(guān)注

關(guān)注

77文章

9639瀏覽量

137870 -

毛刺脈沖

+關(guān)注

關(guān)注

0文章

2瀏覽量

4596

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

請(qǐng)問DAC38J82如何開啟NRZ輸出模式?

DAC3162EVM的輸入阻抗不是高阻態(tài),怎么連接比較器和DAC呀?

DAC3174 DAC1 DAC2模擬輸出信號(hào)不同步是怎么回事?

DAC8830輸出30Hz的方波信號(hào),為什么電平由高到低時(shí),或者由低到高時(shí)失真?

采用STM32F103單片機(jī)的12位DAC打點(diǎn)輸出波形經(jīng)過電容到TPA3111D的INP腳,有時(shí)出現(xiàn)上電異響嘯叫怎么解決?

tlv320dac3100的speaker輸出需要加電感和電容嗎?有沒有推薦參數(shù)?

DAC輸出需要加一個(gè)低通平濾波器,這個(gè)濾波器該怎么設(shè)計(jì)?

DAC輸出如何加大帶載能力?

DAC11001B高電壓輸出數(shù)模轉(zhuǎn)換器(DAC)數(shù)據(jù)表

DAC輸出在高阻抗模式中被加電的問題分析

DAC輸出在高阻抗模式中被加電的問題分析

評(píng)論