時序分析的基本步驟

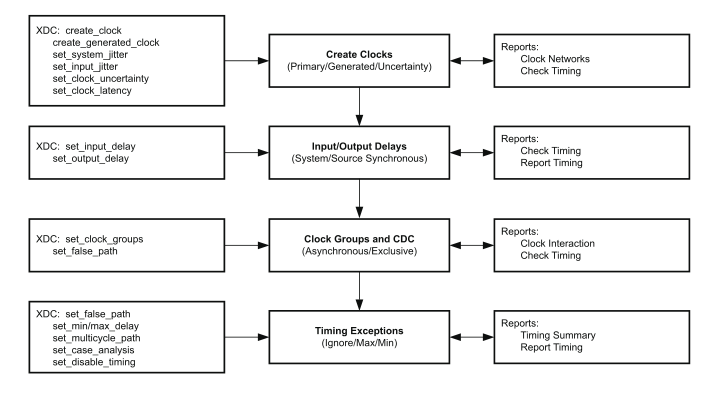

一個合理的時序約束,可以分為以下步驟:

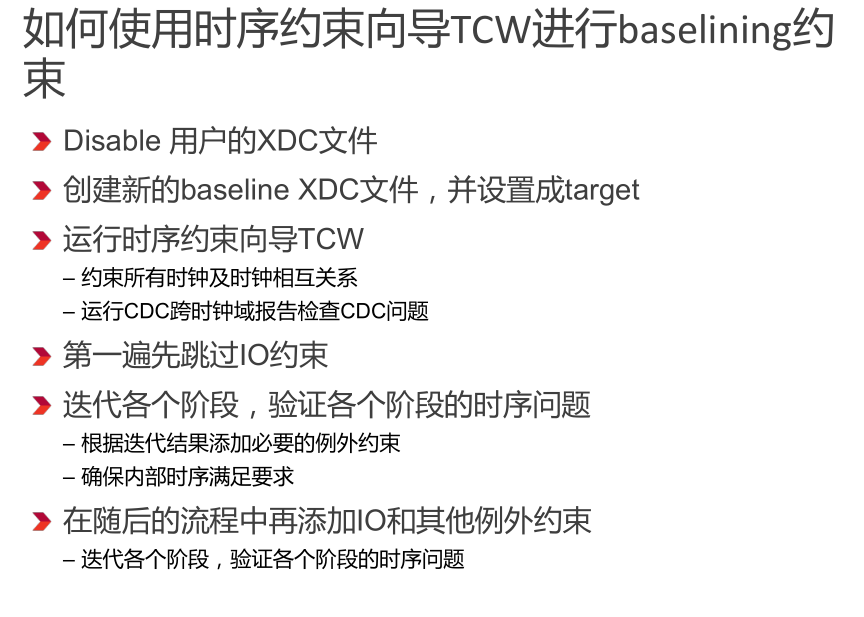

時序約束整體的思路與之前我說的方法基本一致。整體的思路如下:

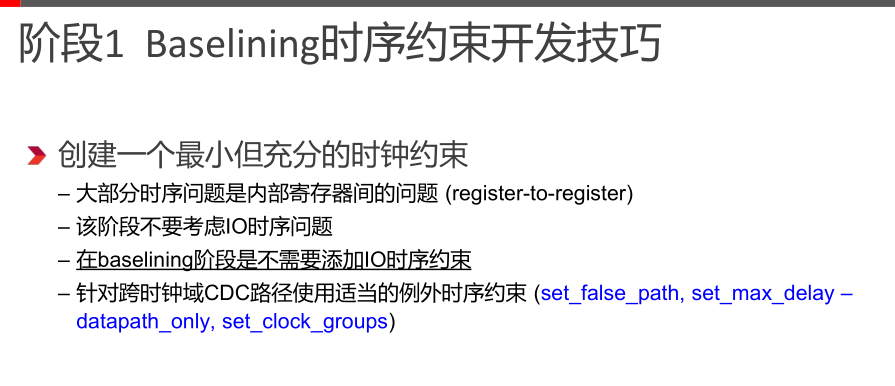

1. 先是約束時鐘,讓軟件先解決內部時序問題;(在這一步驟中可以適當加入時序例外,以便時序通過)

2. 然后再加入IO的延遲約束;

3. 最后針對沒有過的時序,添加時序例外。

在《vivado使用誤區與進階》中,提到了一種叫 UltraFAST 的設計方法。針對下圖中所說的根據迭代結果添加必要的例外約束(步驟1),為什么是添加必要的呢?是因為雖然是跨時鐘域,但是有時候就算不約束,時序也能過。當碰到時序不過的時候,現階段可以去針對該部分路徑進行時序例外約束,以便后續繼續分析。需要注意的是,就算沒有報時序為例,現階段也一定要去留意那些跨時鐘的路徑(通過clock_interaction),確認代碼有沒有做相應的跨時鐘域處理。針對跨時鐘域的代碼處理后面會提到。

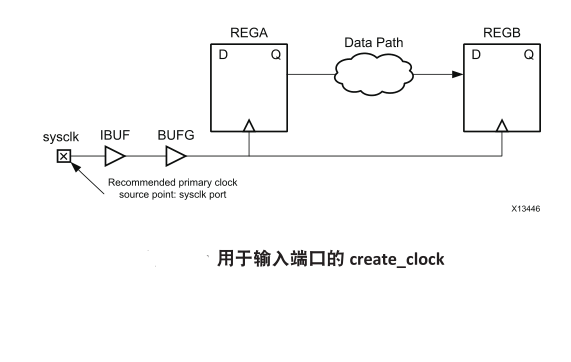

定義時鐘約束

時鐘主要可以分為主時鐘以及衍生時鐘。

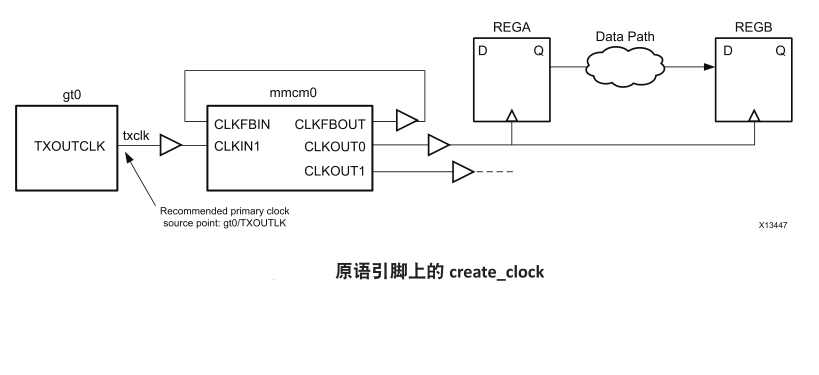

創建主時鐘。典型的主時鐘根包括有以下幾種情況:輸入端口、千兆位收發器輸出引腳以及某些硬件原語輸出管腳。

約束實例 :

create_clock -name SysClk -period 10 -waveform {0 5} [get_ports sysclk]

GT 收發器輸入引腳,例如已恢復的時鐘。

約束實例 :

create_clock -name txclk -period 6.667 [get_pin gt0/TXOUTCLK]

創建生成時鐘

自動衍生時鐘

大部分生成時鐘都由 Vivado 設計套件時序引擎自動衍生獲得,該引擎可識別時鐘修改模塊 (CMB)及其對主時鐘所執行的變換。賽靈思 7 系列器件中,CMB 是 :

? MMCM*/ PLL*

? BUFR

? PHASER*

如果 Vivado 設計套件時序引擎所選擇的自動衍生時鐘名稱并不合適,您可以使用 create_generated_clock 命令強行定義自己的名稱,此時無需指定波形轉換。該約束應剛好位于約束文件中定義主時鐘的約束之后。例如,由 MMCM 實例生成的時鐘的默認名稱是 net0,您可以添加如下約束強制將其設定為自己的名稱(例如fftClk):

create_generated_clock -name fftClk [get_pins mmcm_i/CLKOUT0]

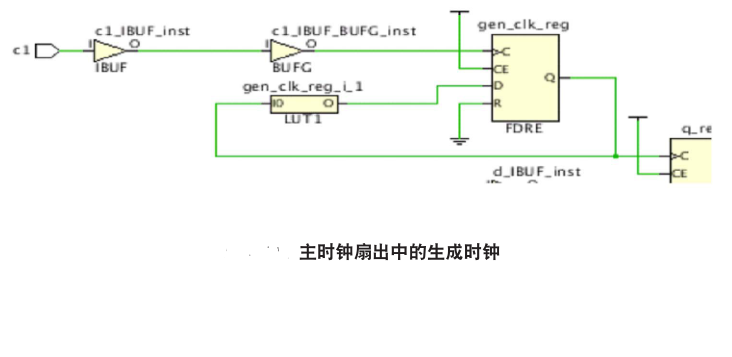

生成時鐘源自另一個現有時鐘(主時鐘)。通常用來描述由邏輯模塊在主時鐘上執行的波形變換。由于生成時鐘的定義取決于主時鐘特性,因此必須首先定義主時鐘。要明確定義生成時鐘,必須使用 create_generated_clock 命令。

create_generated_clock -name GC1 -source [get_pins gen_clk_reg/C] -divide_by 2 [get_pins gen_clk_reg/Q]

跨時終域處理

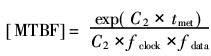

跨時鐘域處理,主要是為了避免亞穩態的傳播(注意亞穩態不能消除,但是可以采用一定的方式,降低其傳播的風險)。觸發器進入亞穩態的時間可以用參數MTBF(Mean Time Between Failures)來描述,MTBF即觸發器采樣失敗的時間間隔,表示為:

例如針對單bit數據的跨時鐘域處理,是為了讓MTBF增大,使得進入一個可接受范圍。

*跟大家探討一個問題,為什么打兩拍就可以降低亞穩態的傳播呢?

我想到的一個場景如下:

信號a經過跨時鐘處理后變成了a’;這樣就可以確保在時序滿足的前提下,同一個時鐘域中的1、2、3模塊接收到的a’的值是一致的,如果不做跨時鐘域處理,由于布局布線的延遲不一樣,不能確保到達1、2、3模塊的值是一致的,從而導致邏輯混亂,引起系統的不穩定現象。

IO的延遲約束

輸入延遲

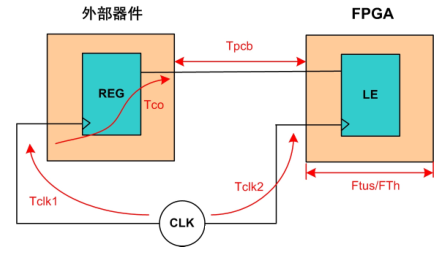

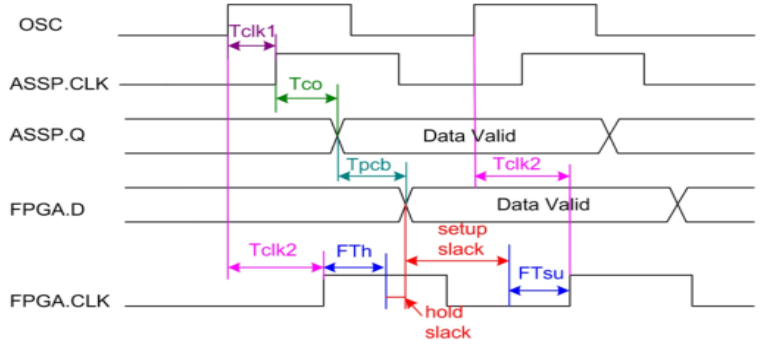

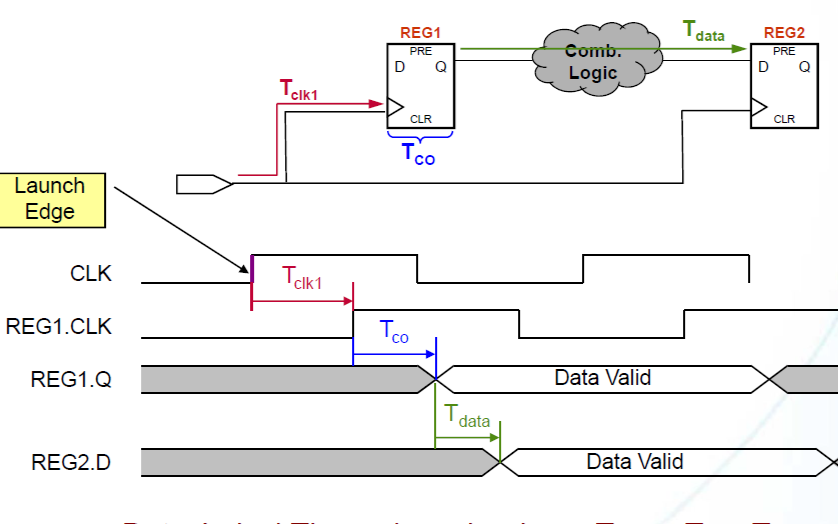

外部器件發送數據到FPGA系統模型如下圖所示。對FPGA的IO口進行輸入最大最小延時約束是為了讓FPGA設計工具能夠盡可能的優化從輸入端口到第一級寄存器之間的路徑延遲,使其能夠保證系統時鐘可靠的采到從外部芯片到FPGA的信號。

輸入延時即為從外部器件發出數據到FPGA輸入端口的延時時間。其中包括時鐘源到FPGA延時和到外部器件延時之差、經過外部器件的數據發送Tco,再加上PCB板上的走線延時。如下圖所示,為外部器件和FPGA接口時序。

最大輸入延時(input delay max)為當從數據發送時鐘沿(lanuch edge)經過最大外部器件時鐘偏斜(Tclk1),最大的器件數據輸出延時(Tco),再加上最大的PCB走線延時(Tpcb),減去最小的FPGA時鐘偏移(FTsu)的情況下還能保證時序滿足的延時。這樣才能保證FPGA的建立時間,準確采集到本次數據值,即為setup slack必須為正,計算公式如下式所示:

Setup slack =(Tclk + Tclk2(min))–(Tclk1(max)+Tco(max)+Tpcb(max)+FTsu)≥0(1)

最小輸入延時(input delay min)為當從數據發送時鐘沿(lanuch edge)經過最小外部器件時鐘偏斜(Tclk1),最小器件數據輸出延時(Tco),再加上最小PCB走線延時(Tpcb),此時的時間總延時值一定要大于FPGA的最大時鐘延時和建立時間之和,這樣才能不破壞FPGA上一次數據的保持時間,即為hold slack必須為正,計算公式如下式所示:

Hold slack =(Tclk1(min)+ Tco(min)+ Tpcb(min))–(FTh + Tclk2(max))≥ 0(2)

我們很容易就可以從公式(1)和(2)推到出(3)

Tclk – Ftsu ≥Tclk1 -Tclk2 + Tco+ Tpcb ≥ FTh(3)

在公式(3)中,我們發現Tclk 、Ftsu以及FTh,對于工具來說是已知的,而Tclk1 - Tclk2 + Tco + Tpcb正是我們需要告知綜合工具的延遲量。

從我們推到出的公式,我們可以得到:

Input_delay_max = Tclk – Ftsu;

Input_delay_min = FTh;

輸出延遲

FPGA輸出數據給外部器件模型如下圖所示。對FPGA的IO口進行輸出最大最小延時約束是為了讓FPGA設計工具能夠盡可能的優化從第一級寄存器到輸出端口之間的路徑延遲,使其能夠保證讓外部器件能準確的采集到FPGA的輸出數據。

輸出延時即為從FPGA輸出數據后到達外部器件的延時時間。其中包括時鐘源到FPGA延時和到外部器件延時之差、PCB板上的走線延時以及外部器件的數據建立和保持時間。如所示,為FPGA和外部器件接口時序圖。

最大輸出延時(output delay max)為當從FPGA數據發出后經過最大的PCB延時、最小的FPGA和器件時鐘偏斜,再加上外部器件的建立時間。約束最大輸出延時,是為了約束IO口輸出,從而使外部器件的數據建立時間,即為setup slack必須為正,計算公式如下式所示:

Setup slack =(Tclk + Tclk2(min))–(Tclk1(max)+FTco(max)+Tpcb(max)+Tsu)≥0(4)

最小輸出延時(output delay min)為當從FPGA數據發出后經過最小的PCB延時、最大的FPGA和器件時鐘偏斜,再減去外部器件的建立時間。約束最小輸出延時,是為了約束IO口輸出,從而使IO口輸出有個最小延時值,防止輸出過快,破壞了外部器件上一個時鐘的數據保持時間,導致hlod slack為負值,不能正確的鎖存到數據,最小輸出延時的推導計算公式如下式所示:

Hold slack =(Tclk1(min)+ FTco(min)+ Tpcb(min))–(Th + Tclk2(max))≥ 0(5)

我們很容易就可以從公式(4)和(5),發現這兩條公式與前面推導輸入延遲如出一轍。只不過現在FPGA變成了輸出器件,而Tsu、Th是下游器件的參數,綜合工具并不知情,需要我們告訴他。除了FTco以外,其他參數都需要我們告訴工具。

由公式(4)我們可以推導出:

FTco(max)+ Tpcb(max)–(Tclk2(min)– Tclk1(max)+Tsu ≤Tclk

那么output delay max= Tpcb(max)–(Tclk2(min)– Tclk1(max)+Tsu

同理我們由公式(5)可以推導出:

FTco(min)+ Tpcb(min)–(Tclk2(max)– Tclk1(min))– Th ≥ 0

那么output delay min =Tpcb(min)–(Tclk2(max)– Tclk1(min))– Th

為了幫助學員能夠更深入地掌握FPGA系統設計與實際應用。編者給大家準備了FPGA系列學習電子書籍,包括了CPLD/Verilog編程語言基礎與設計,數字IC、基本邏輯、組合邏輯等基礎電路,Vivado平臺開發與調試、集成開發環境使用及相關技巧,FPGA數字信號處理、數字圖像處理及各種FPGA實戰項目設計案例等等。

1.Verilog數字系統設計教程

本書從算法和計算的基本概念出發,講述如何用硬線邏輯電路實現復雜數字邏輯系統的方法。全書共分三部分。部分內容共18章;二部分共12個上機練習實驗范例;三部分是Verilog硬件描述語言參考手冊,可供讀者學習、查詢之用。本書2版后,在語法篇中增加了IEEE Verilog1364-2001標準簡介,以反映Verilog語法的新變化。

2.數字電路與邏輯設計

本書系統地闡述了邏輯電路的基礎理論--邏輯函數及其數學工具;重點討論了邏輯電路的設計方法和分析方法;詳細介紹了通用性強的幾類中、大規模集成器件,并結合實例介紹了它們在各領域中的應用;對可編程邏輯器件及其硬件描述語言也進行了系統介紹。

全書共10章,主要內容有:邏輯函數、集成邏輯門、組合邏輯電路、集成觸發器、時序邏輯電路、硬件描述語言、半導體存儲器、可編程邏輯器件、脈沖單元電路、模數及數模轉換技術等。各章均附有內容提要、小結、思考題和習題。

3.Vivado從此開始

本書涵蓋了Vivado的四大主題:設計流程、時序約束、設計分析和Tcl腳本的使用,結合實例深入淺出地闡述了Vivado的使用方法,精心總結了Vivado在實際工程應用中的一些技巧和注意事項,既包含圖形界面操作方式,也包含相應的Tcl命令。本書語言流暢,圖文并茂。全書共包含405張圖片、17個表格、172個Tcl腳本和39個HDL代碼,同時,本書配有41個電子教學課件,為讀者提供了直觀而生動的資料。本書可供電子工程領域內的本科高年級學生和研究生學習參考,也可供FPGA工程師和自學者參考使用。

4.Xilinx新一代FPGA設計套件Vivado應用指南

本書系統論述了新一代FPGA設計套件Vivado的性能、使用方法以及FPGA的開發方法。全書內容包括Vivado設計套件的特性,全面可編程FPGA器件的架構,使用Vivado套件創建復雜數字系統設計項目,仿真系統功能,RTL分析產生網表文件,性能要求的時序約束及綜合,布局布線及靜態時序分析和生成位流文件等全部設計過程,基于項目和非項目批作業兩種用Tcl指令的設計模式,同步設計技術、HDL編碼技術、時序收斂和HI.S優化DSP算法等關鍵技術,并以實例介紹了嵌入式系統的設計方法等。

責任編輯人:CC

-

時序分析

+關注

關注

2文章

127瀏覽量

22551

原文標題:FPGA工程師進階必學:時序分析的基本步驟和整體設計思路

文章出處:【微信號:elecfans,微信公眾號:電子發燒友網】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

時序邏輯電路分析有幾個步驟(同步時序邏輯電路的分析方法)

時序分析基本概念介紹

時序約束的步驟分析

時序分析概念min pulse width介紹

AOCV時序分析概念介紹

時序分析的基本步驟介紹

時序分析的基本步驟介紹

評論