賽靈思為 FPGA 和 MPSoC 器件中所有受支持的 I/O 標準提供了 I/O 緩存信息規范 (I/O Buffer Information Specification, IBIS) 模型。

本篇博文旨在提供有關如何為可編程邏輯 (PL) 和處理器系統 (PS) 多用途 I/O (MIO) 進行 IBIS 模型名稱解碼的指導信息。 本文主要分 3 個部分:

PL I/O 標準

PS MIO 標準

PS DDR I/O 標準

在這 3 個章節中包含多個解碼器表格,其中逐一細分羅列了模型名稱的每個部分并提供了一些模型名稱示例。

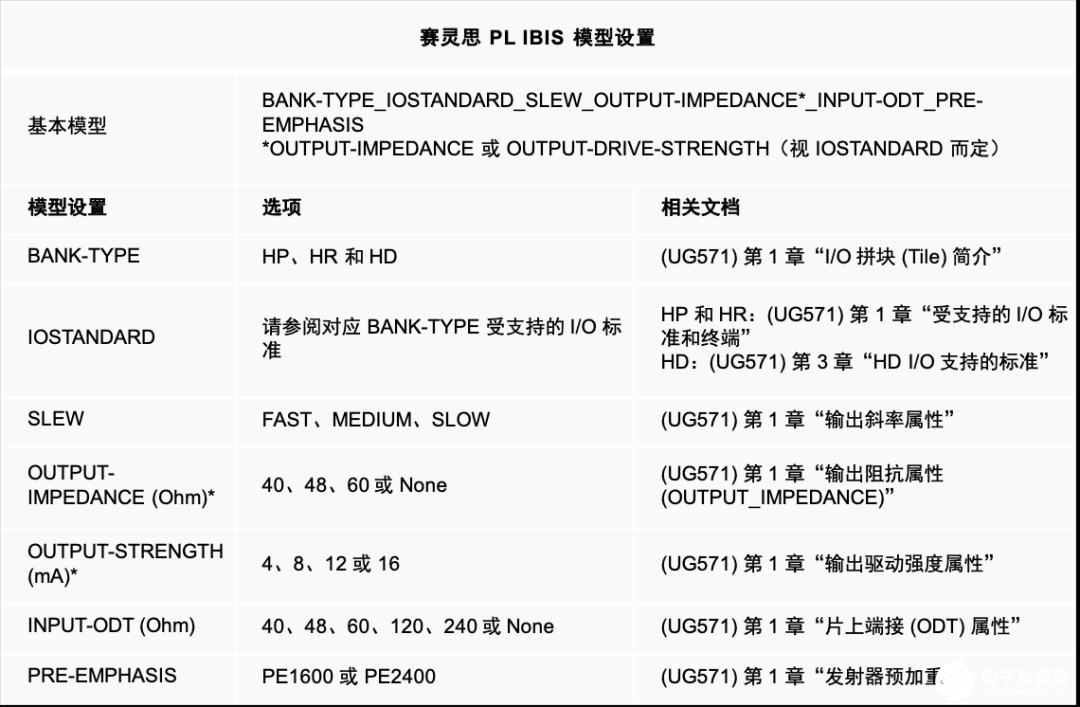

1. 賽靈思 PL I/O 標準 IBIS 解碼器

PL IBIS 解碼器可用于為所有可編程邏輯 I/O 執行 PL IBIS 模型解碼。 它適用于 Zynq MPSoC PL I/O。

表 1:PL IBIS 解碼器

所有模型(LVDS 除外*)都將包含“bank 類型 (Bank Type)”、“I/O 標準 (IOStandard)”、“斜率 (Slew Rate)”和“輸出阻抗/驅動強度 (Output Impedance/DriveStrength)”。

*LVDS 模型將包含“bank 類型 (Bank Type)”、“LVDS”、“I/O 標準 (IOStandard)”和“數字端接 (Digital Termination)”。

內部 100-ohm 差分終端僅在以 1.8V (LVDS) 或 2.5V (LVDS_25) 加電的 bank 中可用。 請參閱(UG571) v1.12 第 103 頁以獲取詳細信息。

https://china.xilinx.com/support/documentation/user_guides/c_ug571-ultrascale-selectio.pdf

注:并非每個 IBIS 模型都包含所有模型設置。

如果模型名稱中不含某項設置,即表示此模型不支持該項設置。

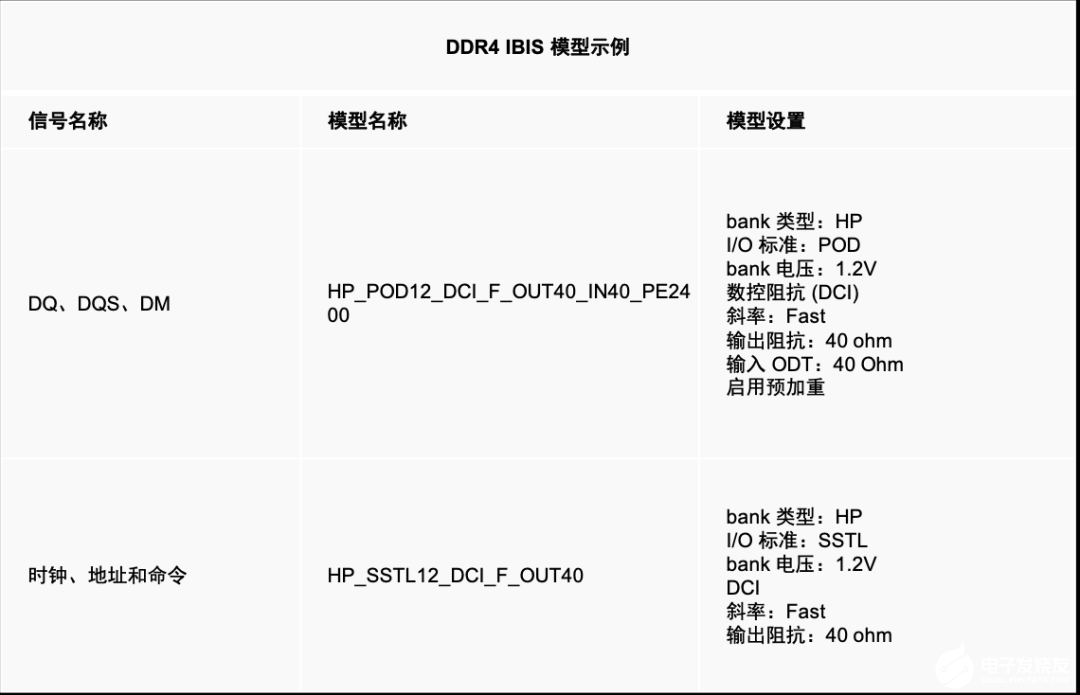

表 2 和表 3 提供了適用于 DDR4 和 SelectIO 的 PL IBIS 模型示例。

表2:PL DDR4 IBIS 模型

差分信號在 IBIS 文件中的“[Diff Pin]”關鍵字下指定。

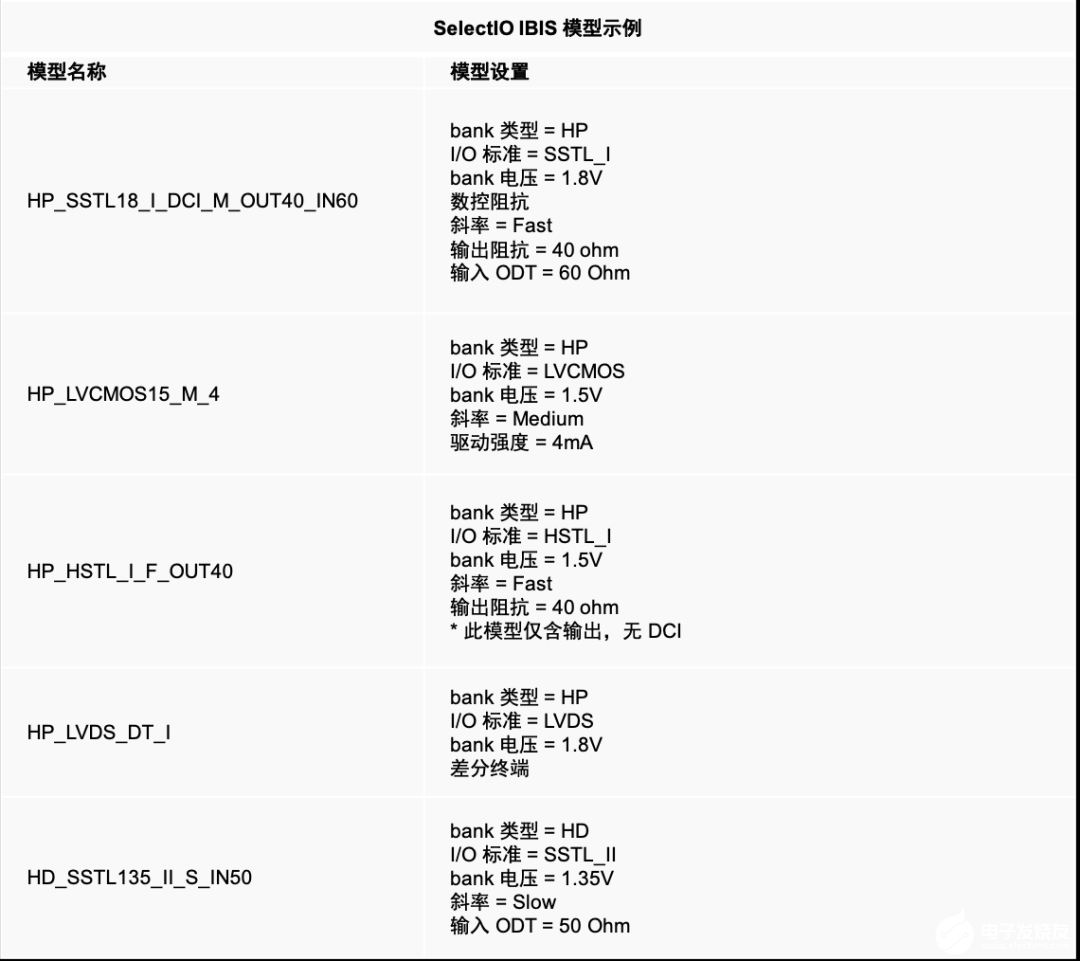

表 3:PL SelectIO IBIS 模型

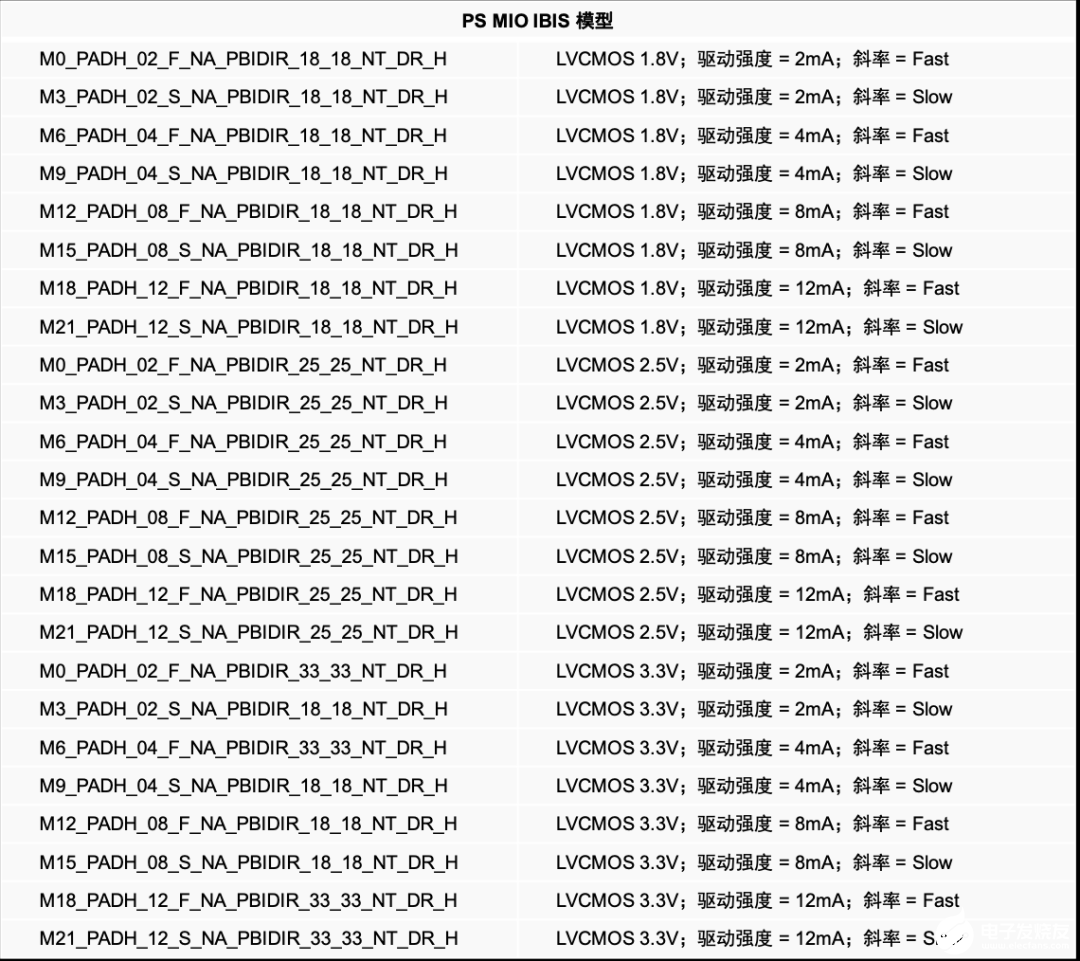

2. 賽靈思 Zynq MPSoC PS MIO IBIS 模型

Zynq MPSoC MIO 管腳支持 LVCMOS,可提供以下選項

接口電壓:1.8V、2.5V 或 3.3V

驅動強度:2mA、4mA、8mA 或 12mA

斜率:Slow 或 Fast

MIO IBIS 模型格式為M0_PADH_02_F_NA_PBIDIR_18_18_NT_DR_H。

表 4 對每個 IBIS 模型的驅動設置進行了解釋。

表 4:PS MIO IBIS 模型

3. 賽靈思 Zynq MPSoC PS DDR IBIS 模型

Zynq MPSoC PS DDR IBIS 信號與所有其它信號都不同。

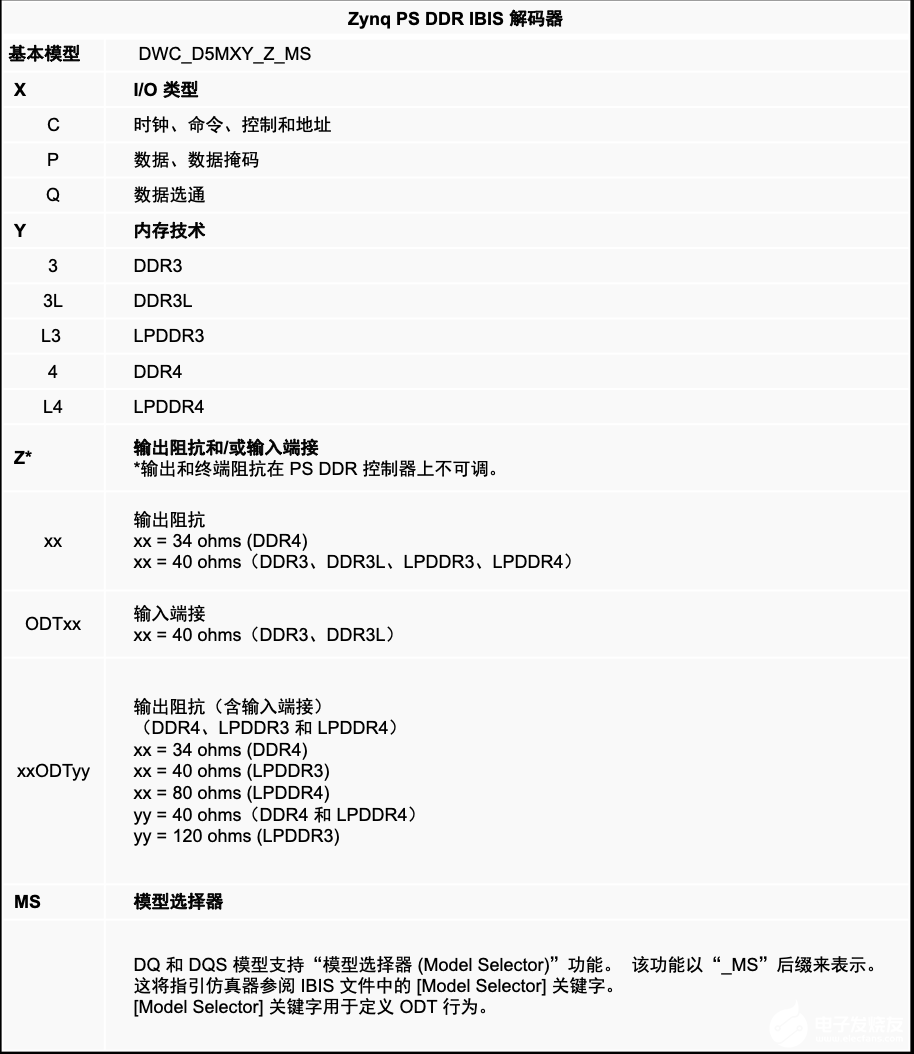

表 5 顯示了適用于 Zynq MPSoC PS DDR IBIS 模型的解碼器。

其中為每一種 DDR 內存類型的 IBIS 模型都提供了相應的示例。

表 5:PS DDR IBIS 解碼器

表 6 到 10 提供了對應受支持的 PS DDR 技術的 Zynq PS DDR IBIS 示例。

表 6:PS DDR3

表 7:PS DDR3L

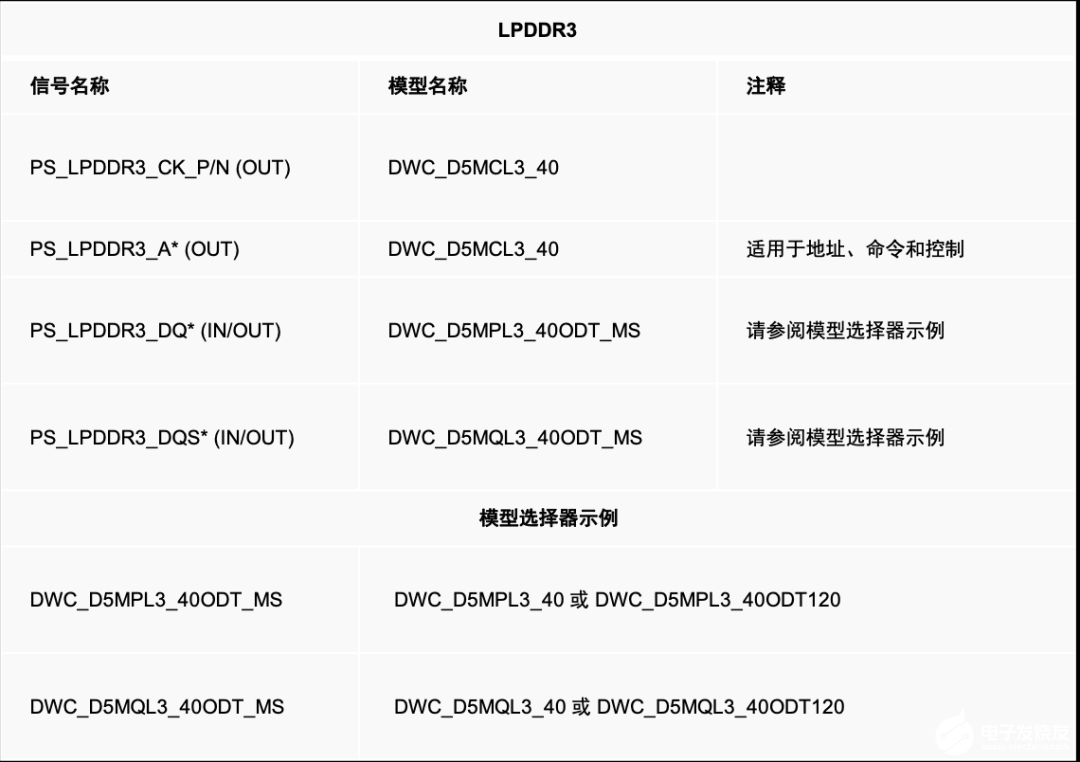

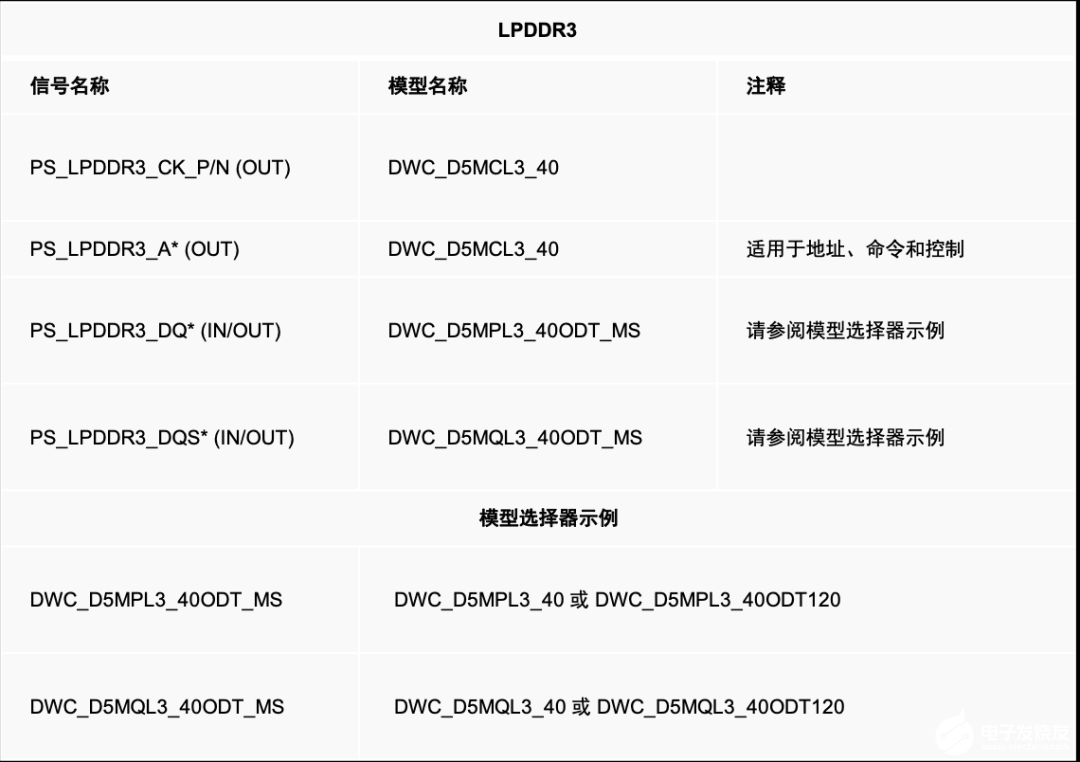

表 8:PS LPDDR3

表 9:PS DDR4

責任編輯:haq

-

解碼器

+關注

關注

9文章

1131瀏覽量

40679 -

賽靈思

+關注

關注

32文章

1794瀏覽量

131166 -

電壓

+關注

關注

45文章

5565瀏覽量

115591 -

IBIS

+關注

關注

1文章

53瀏覽量

19857 -

模型

+關注

關注

1文章

3174瀏覽量

48718

發布評論請先 登錄

相關推薦

無線網解碼器怎么連接

無線網解碼器怎么用

無線解碼器的質量標準是什么

解碼器和控制器區別是什么

控制器解碼器的使用方法

全景聲解碼器

為什么好的播放器還要配解碼器

9740解碼器配什么光柵

光柵解碼器損壞的表現有哪些

數字音頻解碼器和聲卡

賽靈思 PL 和 PS IBIS 模型解碼器

賽靈思 PL 和 PS IBIS 模型解碼器

評論