臺灣半導體制造公司(TSMC)在2nm半導體制造節點的研發方面取得了重要突破。這一突破性的報告已經浮出水面臺灣媒體,并已拿起由東方媒體。負責為全球各種大小公司提供處理器和其他芯片的臺積電也有望在2023年中期進入該工藝的試生產階段,并于一年后開始批量生產。

臺積電的2nm節點將標志著當前芯片制造技術的重大跨越

目前,臺積電的最新制造節點是其第一代5納米工藝,該工藝將用于為2020年蘋果旗艦智能手機構建處理器。通俗地講,“節點”指的是晶體管“鰭”的尺寸測量。當今的處理器由數十億個這樣的鰭組成,這些鰭使計算能夠達到無與倫比的復雜性,降低成本和性能。

與“ FinFET”(鰭式場效應晶體管)相反,該術語用來描述由臺積電和韓國Chaebol三星電子的三星代工部門制造的產品上的晶體管設計,而臺積電的2nm工藝將采用差分晶體管設計。該設計被稱為多橋溝道場效應(MBCFET)晶體管,它是對先前FinFET設計的補充。

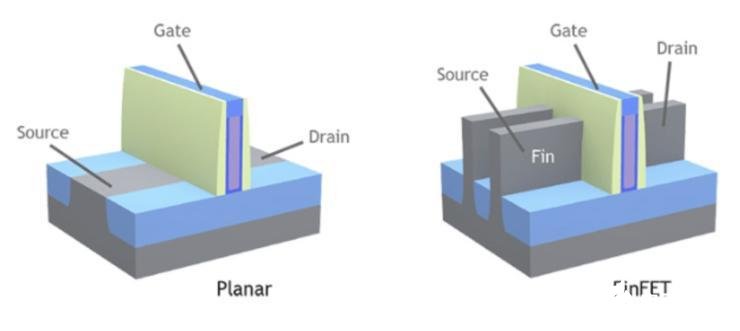

FinFET設計涉及三個基本要素。它們是源極,柵極和漏極,電子從源極流向晶粒,而柵極則調節著這種流動。FinFET之前的設計涉及僅在水平軸上制造源極和漏極,即它們與所討論的芯片一起平放。

FinFET的創新方法將源極和漏極都提高了三維尺寸(即垂直),因此,它允許更多的電子通過柵極,從而減少了泄漏并降低了工作電壓。

臺積電決定將MBCFET設計用于其晶體管并不是晶圓代工廠第一次作出這一決定。三星于去年4月宣布了其3nm制造工藝的設計,該公司的MBCFET設計是對2017年與IBM共同開發和推出的GAAFET晶體管的改進。三星的MBCFET與GAAFET相比,使用了納米片源極和漏極(通道),前者使用納米線。這增加了可用于傳導的表面積,更重要的是,它允許設計人員在不增加橫向表面積的情況下向晶體管添加更多的柵極。

媒體上還散布著無來源的聲明,這也暗示著臺積電預計其20納米工藝節點的良率在2023年將達到驚人的90%。如果發生這種情況,那么該晶圓廠將很好地完善其制造工藝,并輕松地轉向到2024年將實現量產和批量生產。三星在發布MBCFET時表示,預計3nm晶體管的功耗將分別比7nm設計降低30%和45%,并將性能提高30%。

臺積電的2nm工藝是否也將提供類似的改進尚不確定,但一旦確定了該工藝的設計參數,我們就應該發現更多信息。IBM和三星的5nm GAAFET設計能夠在50mm2的表面積中擠壓出驚人的300億個晶體管,基于此,天空似乎確實是臺積電的極限。

責任編輯:lq

-

處理器

+關注

關注

68文章

19167瀏覽量

229153 -

半導體

+關注

關注

334文章

27019瀏覽量

216347 -

晶體管

+關注

關注

77文章

9635瀏覽量

137854

發布評論請先 登錄

相關推薦

速通半導體發布首款自研Wi-Fi7路由器芯片樣品

Rapidus計劃2027年量產2nm芯片

思銳智能半導體先進裝備研發制造中心項目封頂

消息稱三星電子再獲2nm訂單

半導體制造設備對機床的苛刻要求與未來展望

三星奪得首個2nm芯片代工大單,加速AI芯片制造競賽

臺銘光電808nm高功率激光芯片技術取得重大突破

三星電子:加快2nm和3D半導體技術發展,共享技術信息與未來展望

華光光電808nm高功率半導體激光芯片研究取得重大技術突破

半導體制造技術節點:電子科技飛速發展的幕后英雄

TSMC在2nm半導體制造節點的研發方面取得了重要突破

TSMC在2nm半導體制造節點的研發方面取得了重要突破

評論