看了這篇文章,你還不知道晶體和晶振的區(qū)別,你來(lái)打我

晶振有兩個(gè)比較重要的參數(shù),頻偏和溫偏,單位都是PPM,通俗說(shuō),晶振的標(biāo)稱頻率不是一直穩(wěn)定的,某些環(huán)境下晶振頻率會(huì)有誤差,誤差越大,電路穩(wěn)定性越差,甚至電路無(wú)法正常工作。

所以在PCB設(shè)計(jì)時(shí),晶振的layout顯得尤其的重要,有如下幾點(diǎn)需要注意。

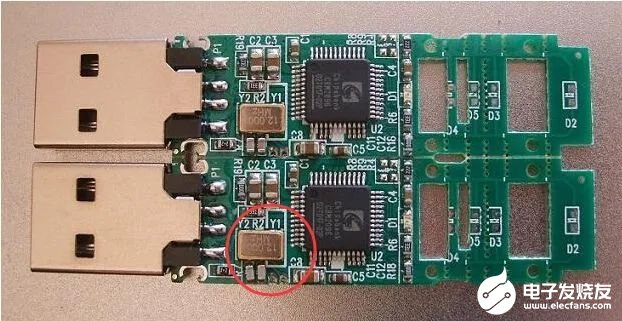

兩個(gè)匹配電容盡量靠近晶振擺放。

晶振由石英晶體構(gòu)成,容易受外力撞擊或跌落的影響,所以在布局時(shí),最好不要放在PCB邊緣,盡量靠近芯片擺放。

晶振的走線需要用GND保護(hù)好,并且遠(yuǎn)離敏感信號(hào)如RF、CLK信號(hào)以及高速信號(hào)。

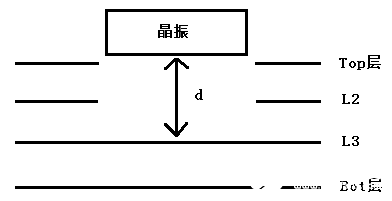

在一些晶振的PCB設(shè)計(jì)中,相鄰層挖空(凈空)或者同一層和相鄰層均凈空處理,第三層需要有完整的地平面,這么做的原因是維持負(fù)載電容的恒定。

晶振負(fù)載電容的計(jì)算公式是:

CL=C1*C2/(C1+C2)+Cic+Cp

Cic為集成電路內(nèi)部電容,Cp為PCB板的寄生電容,寄生電容過(guò)大,將會(huì)導(dǎo)致負(fù)載電容偏大,從而引起晶振頻偏,這個(gè)時(shí)候減小匹配電容C1和C2可能會(huì)有所改善,但這也是治標(biāo)不治本的措施。

晶振相鄰層挖空是如何控制寄生電容Cp的呢?

電容的物理公式是:C=εS/4πKd,即晶振焊盤與鄰近地平面之間的面積S和距離d均會(huì)影響寄生電容大小,因?yàn)槊娣eS是不變的,所以影響寄生電容的因素只剩下距離d,通過(guò)挖空晶振同一層的地和相鄰層的地,可以增大晶振焊盤與地平面之間的距離,來(lái)達(dá)到減小寄生電容的效果。

電容容值和物理量之間的關(guān)系

簡(jiǎn)單畫了一個(gè)圖示,如下一個(gè)4層板,晶振放在Top層,將Top層和相鄰層凈空之后,晶振相對(duì)于地平面(L3),相比較沒有凈空之前,這個(gè)距離d是增大的,即寄生電容會(huì)減小。

晶振的L1和L2層均凈空處理

晶振的擺放需要遠(yuǎn)離熱源,因?yàn)楦邷匾矔?huì)影響晶振頻偏。

我們知道晶振附近相鄰地挖空處理,一方面是為了維持負(fù)載電容恒定,另一方面很大原因是隔絕熱傳導(dǎo),避免周圍的PMIC或者其他發(fā)熱體的熱透過(guò)銅皮傳導(dǎo)到晶振,導(dǎo)致頻偏,故意凈空不鋪銅,以隔絕熱的傳遞。

為什么溫度會(huì)影響晶振頻率呢?

當(dāng)晶振加熱或者降低到某個(gè)溫度后再降到常溫,與最初在常溫下測(cè)試通常情況下會(huì)有一定的變化,這是因?yàn)榫w的熱滯后現(xiàn)象,帶溫度補(bǔ)償?shù)腡CXO相對(duì)來(lái)說(shuō)精度會(huì)好不少,可以有效解決晶體溫漂,但一般TCXO都是M以上級(jí)別較多,KHz的很少,受限于生產(chǎn)工藝。

責(zé)任編輯:haq

-

pcb

+關(guān)注

關(guān)注

4317文章

23009瀏覽量

396320 -

電容

+關(guān)注

關(guān)注

99文章

5997瀏覽量

150010 -

晶振

+關(guān)注

關(guān)注

34文章

2826瀏覽量

67908

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

TLV320AIC33IRGZ Layout走線時(shí)需要注意的事項(xiàng)有哪些?

貼片晶振選型與應(yīng)用的藝術(shù):精準(zhǔn)匹配,高效運(yùn)行

貼片電感的尺寸和形狀設(shè)計(jì)需要注意什么?

淺析貼片晶振和直插晶振區(qū)別以及如何選擇?

貼片晶振的PCB layout需要注意哪些?

貼片晶振的PCB layout需要注意哪些?

評(píng)論