在進行整機RE輻射測試時,在頻譜圖上常會出現兩種情形,一種是30M~300M的低頻包絡,另一種是300M~40G頻段內的高頻尖峰。前者一般是由電源或者接口電路驅動芯片激勵線纜導致的輻射,后者一般是由時鐘借助線纜或結構上的孔洞和縫隙對外進行泄露。本文主要討論時鐘導致的輻射情況,對于信號傳輸參考時鐘導致的輻射只能通過濾波去加以抑制,如GE網口的4對差分線參考時鐘為125M,測試時常會在頻譜上發現125M及其倍頻處的噪聲尖峰,此時一般會通過網口變壓器和去耦電容去加以抑制。對于時鐘發生器本身或者其輸出信號耦合到輸出線纜上造成的輻射,一般可以通過優化時鐘芯片布局加以解決,下面主要講解如何優化時鐘電路布局及走線來解決時鐘輻射問題。

一、晶體電路應用及PCB設計

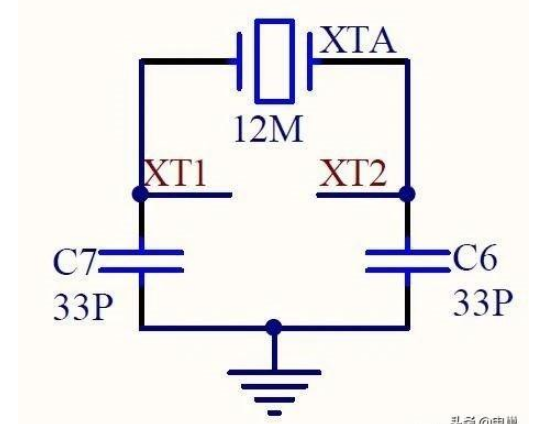

晶體一般應用在單片機小系統和計時芯片的電路中,為其提供電路運行必要的參考時鐘,具體如下圖所示。

單板上的晶體應用

晶體電路一般比較簡單,由晶體加2個電容組成,這兩個電容分別為增益電容和相位電容。

晶體時鐘電路

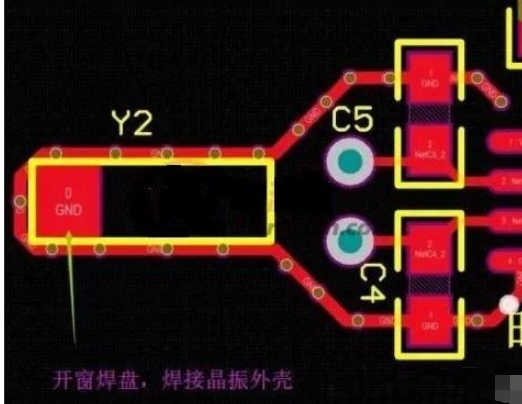

晶體電路的布局及走線如下圖所示。

PTH封裝晶體布局走線圖

圓柱形晶體布局走線圖

二、晶體電路布局走線注意事項

晶體電路布局注意事項:

(1)晶體電路和IC布在同一層面,這樣可以少打孔;

(2)布局要緊湊,電容位于晶體和IC之間,且靠近晶體放置,使時鐘線到IC盡量短;?

(3)對于有測試點的情況,盡量避免stub或者是使stub盡量短;?

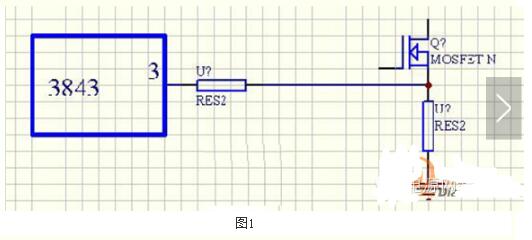

(4)附近不要擺放大功率器件、如電源芯片、MOS管、電感等發熱量大的器件,會影響晶體輸出頻率;

(5)晶體電路離板邊及出面板信號500mil以上。

晶體電路布線應注意事項:?

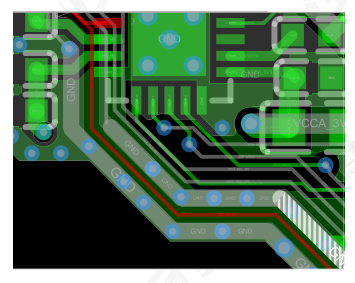

(1)和IC同層布局,同層走線,盡量少打孔,如果打孔,需要在附近加回流地孔;

(2)時鐘走線采用類差分走線;

(3)走線要加粗,通常8~12mil,由于晶體時鐘波形為正弦波,所以此處按模擬設計;

(4)信號線包地處理,且包地線或者銅皮要打屏蔽地孔;?

(5)晶體電路模塊區域相當于模擬區域,禁止其他信號穿過。

責任編輯人:CC

-

pcb

+關注

關注

4318文章

23022瀏覽量

396434 -

晶體

+關注

關注

2文章

1342瀏覽量

35378 -

PCB設計

+關注

關注

394文章

4671瀏覽量

85321

發布評論請先 登錄

相關推薦

晶體電路應用及PCB設計_晶體電路布局走線注意事項

晶體電路應用及PCB設計_晶體電路布局走線注意事項

評論