本文介紹了三種 CCD(電荷耦合器件)圖像傳感器體系結構的特點、優點和缺點,涉及全幀(FF)、幀傳輸(FT)和行間傳輸(IT)三種 CCD 的架構。

全幀(Full-Frame)CCD

半導體區域既可以作為光電元件,也可以作為電荷轉移器件,這有點違反直覺,但這正是 FF CCD 中發生的事情。在集成過程中,像素位置響應入射光子積累電荷,在集成之后,電荷包垂直地通過像素位置向水平移位寄存器移動。

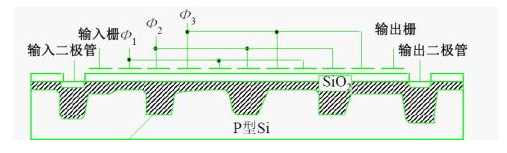

一般情況下,我們通過應用精心定時的時鐘信號來獲得 CCD 像素數據,這些時鐘信號依次在器件的電荷傳輸結構中產生電位阱和電位屏障。在全幀 CCD 中,我們需要能夠將這些控制電壓應用到同樣起光電探測器作用的區域,因此,柵極電極由透明多晶硅制成。

全幀 CCD 相對而言比較簡單且易于制造,并且它們允許整個 CCD 表面具有光敏性。這使硅的給定區域中可以包含的像素數量最大化,同時也使每個像素中實際上能夠將光子轉換為電子的部分最大化。

然而,一個主要的限制是需要一個機械快門(或一個同步的、短時間的光源稱為頻閃)。CCD 的光激活區并不會因為你已經決定是時候執行讀出而停止光激活。如果沒有在曝光周期完成后阻擋入射光的機械快門,則在(有意)集成期間生成的電荷包將被讀出期間到達的光損壞。

這是全幀 CCD 的基本架構

幀傳輸(Frame-Transfer)CCD

一般來說,我們更喜歡用電子方式控制曝光,快門(像任何其他快速移動的高精度機械設備一樣)使設計更加復雜,最終產品更加昂貴,整個系統更容易出現故障。在電池供電的應用中,驅動物理物體所需的額外能量也是不可取的。

FT-CCD 允許我們保持 FF-CCD 的一些優點,同時(幾乎)不需要快門。這是通過將 FF CCD 分成兩個大小相等的部分來實現的。其中一個部分是普通的光敏成像陣列,另一個部分是屏蔽入射光的存儲陣列。

在集成之后,用于所有像素的電荷包被快速地傳輸到存儲陣列,然后在存儲陣列中發生讀出。當讀取存儲位置時,活動像素可以為下一圖像累積電荷,這使得幀傳輸 CCD 能夠獲得比全幀 CCD 更高的幀速率。

說 FT 架構幾乎消除了快門,因為無快門設計會遇到一個稱為垂直涂抹的問題。電荷包從活動像素到存儲位置的傳輸很快,但不是瞬間發生的,因此在垂直傳輸期間到達傳感器的光可以改變圖像信息。

FT 架構的主要缺點是成本較高,并且相對于圖像質量而言面積增大,因為基本上是使用 FF 傳感器,然后將像素數減少兩倍。

幀傳輸 CCD 在全幀架構中增加了一個存儲陣列

線間傳輸(Interline-Transfer)CCD

我們需要的最后一個主要的架構改進是將集成電荷快速轉移到存儲區域,從而將污跡降低到可以忽略的程度。線間傳輸 CCD 通過提供與每個光活動位置相鄰的存儲(和傳輸)區域的網絡來實現這一點。曝光完成后,傳感器中的每個電荷包同時傳輸到非光敏垂直移位寄存器中。

因此,它的 CCD 能夠以最小的拖影實現電子快門,并且像 FT-ccd 一樣,它們可以在讀出期間集成,從而保持較高的幀速率能力。然而,如果光生電荷在讀出過程中從光活性柱泄漏到相鄰的垂直移位寄存器中,則可能發生一些涂抹。如果應用程序不需要高幀速率,則可以通過延遲積分直到讀出完成來消除此問題。

線間 CCD 不需要幀傳輸 CCD 中使用的大存儲部分,但它們引入了一個新的缺點:傳感器成為將光子轉換為電子的效率較低的手段,因為每個像素位置現在都由光電二極管和垂直移位寄存器的一部分組成。換言之,部分像素對光不敏感,因此相對于落在像素區域上的光的量產生較少的電荷。這種靈敏度的損失通過在傳感器上添加將入射光集中到每個像素的光活動區域的微小透鏡而大大減輕,但是這些“微透鏡”有其自身的一系列困難。

在行間傳輸架構中,存儲(和垂直傳輸)區域位于光活性柱之間。

結論

希望這篇文章能幫助理解在設計 CCD 圖像傳感器時所涉及的權衡。全幀 CCD 可能看起來是最“原始”的類型,但它們仍然是不需要高幀速率的系統中的首選,并且可以容忍閃光燈或機械快門的使用。幀傳輸 CCD 和線間傳輸 CCD 具有更多的用途,在某些應用中具有關鍵的優勢。

審核編輯 黃昊宇

-

CCD

+關注

關注

32文章

879瀏覽量

142131 -

圖像傳感器

+關注

關注

68文章

1883瀏覽量

129451

發布評論請先 登錄

相關推薦

工業溫度傳感器的優缺點 溫度傳感器在智能家居中的應用

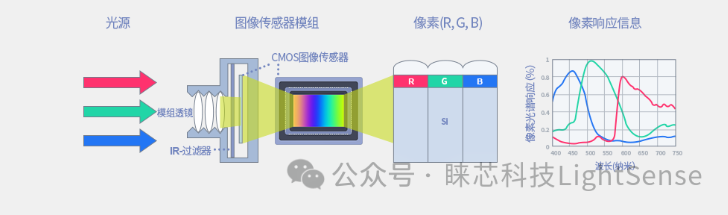

CMOS圖像傳感器的優缺點

CMOS與CCD傳感器的區別

AJ601PGAP1AA1AMA/E雷達傳感器和紅外傳感器優缺點對比

索尼圖像傳感器芯片有哪些

熱電阻溫度傳感器的優缺點有哪些

什么是壓電陶瓷傳感器?它有哪些優缺點?

非接觸式溫度傳感器的優缺點有哪些

CMOS圖像傳感器堆棧式與單芯片的區別

圖像傳感器常見參數解讀

如何權衡CCD圖像傳感器的各種優缺點?

如何權衡CCD圖像傳感器的各種優缺點?

評論