電磁干擾的三要素是干擾源、干擾傳輸途徑、干擾接收器。EMC 就圍繞這些問題進行研究。最基本的干擾抑制技術(shù)是屏蔽、濾波、接地。它們主要用來切斷干擾的傳輸途徑。廣義的電磁兼容控制技術(shù)包括抑制干擾源的發(fā)射和提高干擾接收器的敏感度,但已延伸到其他學科領(lǐng)域。

本規(guī)范重點在單板的 EMC 設(shè)計上,附帶一些必須的 EMC 知識及法則。在印制電路板設(shè)計階段對電磁兼容考慮將減少電路在樣機中發(fā)生電磁干擾。問題的種類包括公共阻抗耦合、串擾、高頻載流導(dǎo)線產(chǎn)生的輻射和通過由互連布線和印制線形成的回路拾取噪聲等。

在高速邏輯電路里,這類問題特別脆弱,原因很多:

1、電源與地線的阻抗隨頻率增加而增加,公共阻抗耦合的發(fā)生比較頻繁;

2、信號頻率較高,通過寄生電容耦合到步線較有效,串擾發(fā)生更容易;

3、信號回路尺寸與時鐘頻率及其諧波的波長相比擬,輻射更加顯著。

4、引起信號線路反射的阻抗不匹配問題。

……

1 總體概念及考慮

1、五一五規(guī)則,即時鐘頻率到 5MHz 或脈沖上升時間小于 5ns,則 PCB 板須采用多層板。

2、不同電源平面不能重疊。

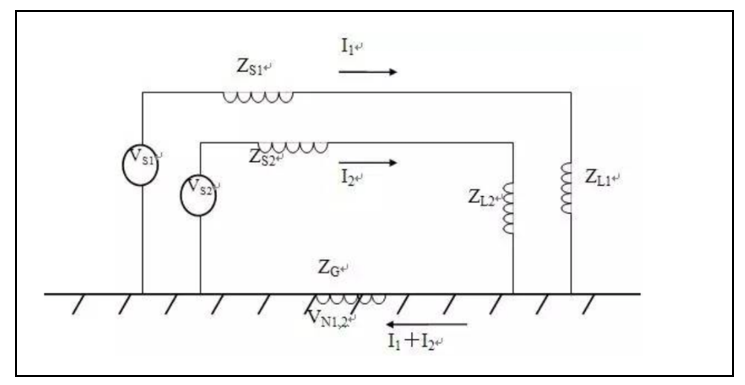

3、公共阻抗耦合問題。

模型:

VN1=I2ZG 為電源 I2 流經(jīng)地平面阻抗 ZG 而在 1 號電路感應(yīng)的噪聲電壓。

由于地平面電流可能由多個源產(chǎn)生,感應(yīng)噪聲可能高過模電的靈敏度或數(shù)電的抗擾度。

解決辦法:

①模擬與數(shù)字電路應(yīng)有各自的回路,最后單點接地;

②電源線與回線越寬越好;

③縮短印制線長度;

④電源分配系統(tǒng)去耦。

4、減小環(huán)路面積及兩環(huán)路的交鏈面積。

5、一個重要思想是:PCB 上的 EMC 主要取決于直流電源線的 Z

2 布局

下面是電路板布局準則:

1、 晶振盡可能靠近處理器

2、 模擬電路與數(shù)字電路占不同的區(qū)域

3、 高頻放在 PCB 板的邊緣,并逐層排列

4、 用地填充空著的區(qū)域

3 布線

1、電源線與回線盡可能靠近,最好的方法各走一面。

2、為模擬電路提供一條零伏回線,信號線與回程線小與 5:1。

3、針對長平行走線的串擾,增加其間距或在走線之間加一根零伏線。

4、手工時鐘布線,遠離 I/O 電路,可考慮加專用信號回程線。

5、關(guān)鍵線路如復(fù)位線等接近地回線。

6、為使串擾減至最小,采用雙面#字型布線。

7、高速線避免走直角。

8、強弱信號線分開。

4 屏蔽

1 屏蔽 》 模型:

屏蔽效能 SE(dB)=反射損耗 R(dB)+吸收損耗 A(dB)

高頻射頻屏蔽的關(guān)鍵是反射,吸收是低頻磁場屏蔽的關(guān)鍵機理。

2、工作頻率低于 1MHz 時,噪聲一般由電場或磁場引起,(磁場引起時干擾,一般在幾百赫茲以內(nèi)),1MHz 以上,考慮電磁干擾。單板上的屏蔽實體包括變壓器、傳感器、放大器、DC/DC 模塊等。更大的涉及單板間、子架、機架的屏蔽。

3、 靜電屏蔽不要求屏蔽體是封閉的,只要求高電導(dǎo)率材料和接地兩點。電磁屏蔽不要求接地,但要求感應(yīng)電流在上有通路,故必須閉合。磁屏蔽要求高磁導(dǎo)率的材料做 封閉的屏蔽體,為了讓渦流產(chǎn)生的磁通和干擾產(chǎn)生的磁通相消達到吸收的目的,對材料有厚度的要求。高頻情況下,三者可以統(tǒng)一,即用高電導(dǎo)率材料(如銅)封閉并接地。

4、對低頻,高電導(dǎo)率的材料吸收衰減少,對磁場屏蔽效果不好,需采用高磁導(dǎo)率的材料(如鍍鋅鐵)。

5、磁場屏蔽還取決于厚度、幾何形狀、孔洞的最大線性尺寸。

6、磁耦合感應(yīng)的噪聲電壓 UN=j(luò)wB.A.coso=j(luò)wM.I1,(A 為電路 2 閉合環(huán)路時面積;B 為磁通密度;M 為互感;I1 為干擾電路的電流。降低噪聲電壓,有兩個途徑,對接收電路而言,B、A 和 COS0 必須減小;對干擾源而言,M 和 I1 必須減小。雙絞線是個很好例子。它大大減小電路的環(huán)路面積,并同時在絞合的另一根芯線上產(chǎn)生相反的電動勢。

7、防止電磁泄露的經(jīng)驗公式:縫隙尺寸 《 λmin/20。好的電纜屏蔽層覆視率應(yīng)為 70%以上。

5 接地

1、300KHz 以下一般單點接地,以上多點接地,混合接地頻率范圍 50KHz~10MHz。另一種分法是:《 0.05λ單點接地;《 0.05λ多點接地。

2、好的接地方式:樹形接地

3、信號電路屏蔽罩的接地。

接地點選在放大器等輸出端的地線上。

4、對電纜屏蔽層,L 《 0.15λ時,一般均在輸出端單點接地。L《0.15λ時,則采用多點接地,一般屏蔽層按 0.05λ或 0.1λ間隔接地。混合接地時,一端屏蔽層接地,一端通過電容接地。

5、對于射頻電路接地,要求接地線盡量要短或者根本不用接線而實現(xiàn)接地。最好的接地線是扁平銅編織帶。當?shù)鼐€長度是λ/4 波長的奇數(shù)倍時,阻抗會很高,同時相當λ/4 天線,向外輻射干擾信號。

6、單板內(nèi)數(shù)字地、模擬地有多個,只允許提供一個共地點。

7、接地還包括當用導(dǎo)線作電源回線、搭接等內(nèi)容。

6 濾波

1、選擇 EMI 信號濾波器濾除導(dǎo)線上工作不需要的高頻干擾成份,解決高頻電磁輻射與接收干擾。它要保證良好接地。分線路板安裝濾波器、貫通濾波器、連接器濾波器。從電路形式分,有單電容型、單電感型、L 型、π型。π型濾波器通帶到阻帶的過渡性能最好,最能保證工作信號質(zhì)量。

一個典型信號的頻譜:

2、選擇交直流電源濾波器抑制內(nèi)外電源線上的傳導(dǎo)和輻射干擾,既防止 EMI 進入電網(wǎng),危害其它電路,又保護設(shè)備自身。它不衰減工頻功率。DM(差摸)干擾在頻率 《 1MHz 時占主導(dǎo)地位。CM 在 》 1MHz 時,占主導(dǎo)地位。

3、使用鐵氧體磁珠安裝在元件的引線上,用作高頻電路的去耦,濾波以及寄生振蕩的抑制。

4、盡可能對芯片的電源去耦(1-100nF),對進入板極的直流電源及穩(wěn)壓器和 DC/DC 轉(zhuǎn)換器的輸出進行濾波(uF)。

Cmin≈△I△t/△Vmax △Vmax 一般取 2%的干擾電平。

注意減小電容引線電感,提高諧振頻率,高頻應(yīng)用時甚至可以采取四芯電容。電容的選取是非常講究的問題,也是單板 EMC 控制的手段。

7 其它

單板的干擾抑制涉及的面很廣,從傳輸線的阻抗匹配到元器件的 EMC 控制,從生產(chǎn)工藝到扎線方法,從編碼技術(shù)到軟件抗干擾等。一個機器的孕育及誕生實際上是 EMC 工程。最主要需要工程師們設(shè)計中注入 EMC 意識。

審核編輯 黃昊宇

-

EMC設(shè)計

+關(guān)注

關(guān)注

5文章

257瀏覽量

39397

發(fā)布評論請先 登錄

相關(guān)推薦

【招聘】EMC/元器件工程師-廈門-8.3更新

電子工程師必備手冊—EMI_EMC設(shè)計

設(shè)計工程師必須看完以下設(shè)計規(guī)范

EMI/EMC 設(shè)計秘籍 ——電子產(chǎn)品設(shè)計工程師必備手冊

【PCB工程師必備資料】華為精品_終端互連設(shè)計規(guī)范(共88頁)

工程師必備--EMC設(shè)計規(guī)范

工程師必備:硬件EMC設(shè)計規(guī)范

工程師必備-EMC設(shè)計規(guī)范

工程師必備-EMC設(shè)計規(guī)范

評論