嵌入式 FPGA 將不再是夢想。根據(jù) Achronix,未來,芯片設計者只要簡單地將線對線互連加進其 SoC 設計即可。

Achronix Semiconductor 營銷副總裁 Steve Mensor 表示,這款被稱為 Speedcore 的嵌入式 FPGA (eFPGA) IP 產(chǎn)品目前已經(jīng)就緒且正出貨中。盡管并未透露出貨數(shù)字以及客戶名稱,該公司表示這款產(chǎn)品現(xiàn)在已經(jīng)提供給客戶使用了。

Speedcore 象征著該公司首次進軍 IP 業(yè)務。Achronix 自 2013 年以來一直在生產(chǎn)其旗艦級 FPGA 產(chǎn)品——Speedster 22i。因此,對于 Achronix 來說,這是一條漫長的道路,因為該公司在 4 年以前才首次宣布開發(fā) eFPGA IP 的計劃。

盡管如此,Achronix 在此看到了一線曙光,預計今年可望首次盈利,營收上看 1,200 萬美元。根據(jù) Mensor 表示,該公司預計其銷售額將在 2017 年成長超過 4,000 萬美元,進一步使 eFPGA IP 業(yè)務成為帶動 Achronix 成長的“重要驅(qū)動力”。

設計工具

Speedcore 采用與 Achronix Speedster 22i FPGA 相同的高性能架構(gòu)。專為運算和網(wǎng)絡加速應用而設計的 Speedcore eFPGA IP 將整合至其他公司的 ASIC,應用于數(shù)據(jù)中心、無線基礎設施和網(wǎng)絡設備。

Mensor 認為,eFPGA 的最大優(yōu)勢在于其設計工具。多年來,Achronix 了解到客戶需要更好的設計工具,為其帶來優(yōu)質(zhì)的結(jié)果、簡單易用性以及第三方整合,而這些特點都是“Achronix CAD 環(huán)境”(ACE)所能提供的一部份。

為了成為系統(tǒng)的一部份,eFPGA IP 必須具備易于整合于 SoC 的功能設計。Achronix 提供了可讓客戶直接整合于其 SoC 的 GDS II 版 Speedcore IP,以及可讓客戶用于設計、驗證與編程 Speedcore eFPGA 功能的 ACE 工具客制版。

CPU 投片?

整個電子產(chǎn)業(yè)都知道 FPGA 極其熱門。只要看看微軟(Microsoft)的 Project Catapult 就知道了。

微軟解釋,這項計劃是專為“加速微軟在網(wǎng)絡、安全、云端服務和人工智能(AI)等方面的超級運算基礎”而打造的,并作為其于“后 CPU”(post-CPU)的各種技術——包括 GPU、FPGA 與 ASIC 的最大睹注。

微軟這項 Project Catapult 的關鍵就在于 Altera Stratix V D5 FPGA。Mensor 強調(diào),整個電子產(chǎn)業(yè)普遍存在的看法是,微軟的計劃促成了英特爾(Intel)決定收購 Altera。

藉由 AlphaGo,Googler 的客制 Tensor 處理器單元也激勵了許多工程師,促使他們開始考慮從 ASIC 到 GPU 和 DSP 的一切。Mensor 解釋說,他們正在尋找能夠更有效率處理“加速非結(jié)構(gòu)性搜尋、機器學習與人工智能”的技術。

Achronix 在其中看到了機會。

FPGA 應用領域以及成長階段

FPGA 從 1990 年代中期作為“膠合芯片”(glue chip)開始流行于市場上,如今正重新定義其價值,成為 CPU 的協(xié)同處理器。在這個角色上,F(xiàn)PGA 可加速加密 / 解密、壓縮 / 解壓縮,或甚至是預處理資料封包,以便只讓有關的共享資料可被傳送與進行處理。

當進行非結(jié)構(gòu)化搜尋時,F(xiàn)PGA 的平行環(huán)境經(jīng)證實是十分有效的。例如,相較于專為劃分功能成為較小部份以及依順序作業(yè)而設計的 CPU 而言,F(xiàn)PGA 能以平行方式,在單一頻率周期完成整個任務。

當無線基礎設施必須涵蓋多個地理區(qū)時,F(xiàn)PGA 是可編程數(shù)位前端和地理區(qū)客制化的一張備用王牌。

在芯片之間布線

盡管在 SoC 中嵌入 FPGA 總能為設計者帶來不錯的設計想法,但對于 FPGA 供應商而言,要實現(xiàn)這個愿望并不容易。

“在不同芯片之間布線是非常困難的,”Mensor 說。成功整合 eFPGA IP 的關鍵在于盡可能降低延遲并提高吞吐量。該公司強調(diào),Achronix 最先提供了具有嵌入式系統(tǒng)級 IP 的高密度 FPGA。

對于“希望將 ASIC 設計的所有效率以及 eFPGA 可編程硬件加速器的靈活性結(jié)合于同一芯片”的公司,Achronix 為其提供相同的 eFPGA 技術。

而對于 IP 供貨商而言,整合極具挑戰(zhàn)之處在于客戶對于特定應用所要求的優(yōu)化芯片尺寸、功耗與資源分配總有不同的想法與方法。他們還自行定義了查找表數(shù)目、嵌入式內(nèi)存模塊女以及 DSP 模塊的數(shù)量。

但問題并不一定是客戶的不同建置方式,而是他們經(jīng)常使用不同的方法進行芯片測試與驗證。Mensor 解釋,客戶并不知道 IP 供貨商的工具如何與其搭配作業(yè)。例如,“我們經(jīng)常聽到客戶問:‘如何才能用你們的 IP 關閉計時功能?’”

雖然 Achronix 并未為客戶整合其 IP,其業(yè)務取決于所提供的工具是否足以讓客戶快速完成設計

Achronix NT31P1 Achronix 也向外收購了一些第三方 IP,包括接口協(xié)議、可編程 IO、SerDes 和 PLL 等。那么在開發(fā) FPGA 和滿足客戶需求時,Achronix 是否遇到困難?Mensor 說:“我們總會試著把遇到的每個問題都轉(zhuǎn)化為一次機會。”

對于 Achronix 來說,其關鍵在于整合該公司的 FPGA 架構(gòu)。最終的結(jié)果是一款更精簡的 Speedster 22i,其可編程 IO、SerDes 和接口控制器占用的空間更少,相形之下,競爭對手的高階 FPGA 通常使用了大約 50%的芯片面積。

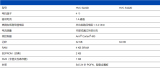

Achronix NT31P2 FPGA 芯片尺寸比較

提高延遲和傳輸速率

Achronix 認為,能夠與 SoC 實現(xiàn)線對線連接的 Speedcore eFPGA,有助于消除大量的可編程 IO 緩沖器,從而使功耗降低一半。此外,Speedcore 的芯片尺寸也比標準 FPGA 更小,使得 eFPGA 的成本可降低 90%以上。

然而,Mensor 強調(diào),“對于大多數(shù)客戶而言,最大的決定因素在于延遲和吞吐量方面的問題。”根據(jù) Achronix,相較于獨立的 FPGA,eFPGA 具有更高的接口性能,可望提高 10 倍的吞吐量和延遲性能。

Speedcore 現(xiàn)可采用臺積電 16FF+工藝,并以臺積電 7nm 技術進行開發(fā)。該公司并承諾,透過 Speedcore 的模塊化架構(gòu)讓 Achronix 能夠輕松地將該技術轉(zhuǎn)移到不同的工藝技術和堆棧。

審核編輯 黃昊宇

-

FPGA

+關注

關注

1620文章

21510瀏覽量

598977 -

嵌入式

+關注

關注

5046文章

18821瀏覽量

298612

發(fā)布評論請先 登錄

相關推薦

TDK進一步擴充Micronas嵌入式電機控制器系列HVC 5x

fpga和嵌入式應該學哪個

嵌入式和fpga的關系

fpga是嵌入式開發(fā)嗎

fpga和嵌入式的區(qū)別和聯(lián)系

fpga與嵌入式的區(qū)別 嵌入式和fpga開發(fā)有什么關系

fpga和嵌入式哪個前景好

嵌入式學習步驟

飛凌嵌入式這2款核心板已完成“礦鴻OS”適配,礦企伙伴看過來

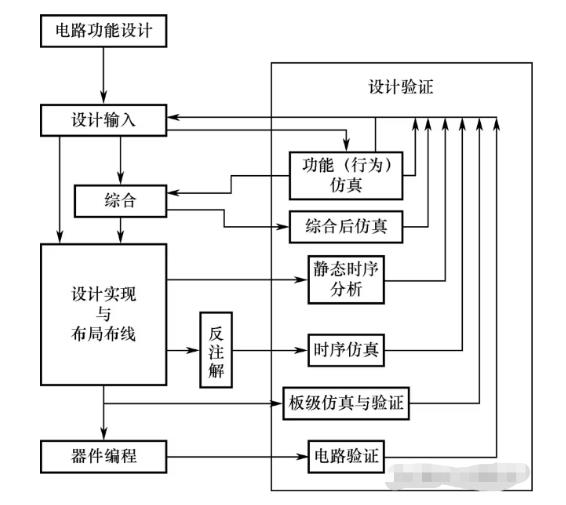

fpga的開發(fā)流程有哪些步驟?fpga和嵌入式系統(tǒng)的區(qū)別在哪里?

什么是嵌入式Linux?

基于ARMS和FPGA的嵌入式數(shù)控系統(tǒng)設計原理

嵌入式FPGA不是夢,只需簡單一步即可完成

嵌入式FPGA不是夢,只需簡單一步即可完成

評論