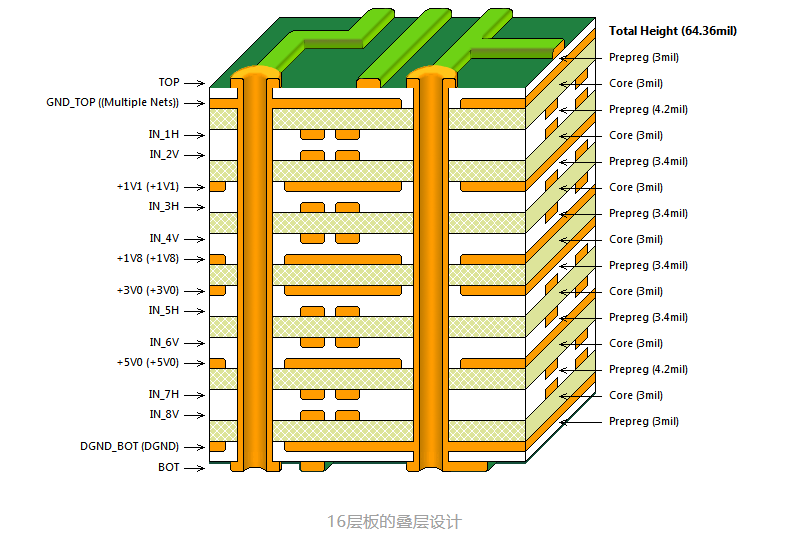

總的來說疊層設計主要要遵從兩個規矩:

1. 每個走線層都必須有一個鄰近的參考層(電源或地層);

2. 鄰近的主電源層和地層要保持最小間距,以提供較大的耦合電容;

下面列出從兩層板到十層板的疊層:

一、單面 PCB 板和雙面 PCB 板的疊層

對于兩層板來說,由于板層數量少,已經不存在疊層的問題。控制 EMI 輻射主要從布線和布局來考慮;

單層板和雙層板的電磁兼容問題越來越突出。造成這種現象的主要原因就是因是信號回路面積過大,不僅產生了較強的電磁輻射,而且使電路對外界干擾敏感。要改善線路的電磁兼容性,最簡單的方法是減小關鍵信號的回路面積。

關鍵信號:從電磁兼容的角度考慮,關鍵信號主要指產生較強輻射的信號和對外界敏感的信號。能夠產生較強輻射的信號一般是周期性信號,如時鐘或地址的低位信號。對干擾敏感的信號是指那些電平較低的模擬信號。

單、雙層板通常使用在低于 10KHz 的低頻模擬設計中:

1 在同一層的電源走線以輻射狀走線,并最小化線的長度總和;

2 走電源、地線時,相互靠近;在關鍵信號線邊上布一條地線,這條地線應盡量靠近信號線。這樣就形成了較小的回路面積,減小差模輻射對外界干擾的敏感度。當信號線的旁邊加一條地線后,就形成了一個面積最小的回路,信號電流肯定會取道這個回路,而不是其它地線路徑。

3 如果是雙層線路板,可以在線路板的另一面,緊靠近信號線的下面,沿著信號線布一條地線,一線盡量寬些。這樣形成的回路面積等于線路板的厚度乘以信號線的長度。

二、四層板的疊層

推薦疊層方式:

1. SIG-GND(PWR)-PWR (GND)-SIG;

2. GND-SIG(PWR)-SIG(PWR)-GND;

對于以上兩種疊層設計,潛在的問題是對于傳統的 1.6mm(62mil)板厚。層間距將會變得很大,不僅不利于控制阻抗,層間耦合及屏蔽;特別是電源地層之間間距很大,降低了板電容,不利于濾除噪聲。

對于第一種方案,通常應用于板上芯片較多的情況。這種方案可得到較好的 SI 性能,對于 EMI 性能來說并不是很好,主要要通過走線及其他細節來控制。主要注意:地層放在信號最密集的信號層的相連層,有利于吸收和抑制輻射;增大板面積,體現 20H 規則。

對于第二種方案,通常應用于板上芯片密度足夠低和芯片周圍有足夠面積(放置所要求的電源覆銅層)的場合。此種方案 PCB 的外層均為地層,中間兩層均為信號 / 電源層。信號層上的電源用寬線走線,這可使電源電流的路徑阻抗低,且信號微帶路徑的阻抗也低,也可通過外層地屏蔽內層信號輻射。從 EMI 控制的角度看, 這是現有的最佳 4 層 PCB 結構。主要注意:中間兩層信號、電源混合層間距要拉開,走線方向垂直,避免出現串擾;適當控制板面積,體現 20H 規則;如果要控 制走線阻抗,上述方案要非常小心地將走線布置在電源和接地鋪銅島的下邊。另外,電源或地層上的鋪銅之間應盡可能地互連在一起,以確保 DC 和低頻的連接性。

三、六層板的疊層

一、 對于芯片密度較大、時鐘頻率較高的設計應考慮 6 層板的設計

推薦疊層方式:

1.SIG-GND-SIG-PWR-GND-SIG;

對于這種方案,這種疊層方案可得到較好的信號完整性,信號層與接地層相鄰,電源層和接地層配對,每個走線層的阻抗都可較好控制,且兩個地層都是能良好的吸收磁力線。并且在電源、地層完整的情況下能為每個信號層都提供較好的回流路徑。

2.GND-SIG-GND-PWR-SIG -GND;

對于這種方案,該種方案只適用于器件密度不是很高的情況,這種疊層具有上面疊層的所有優點,并且這樣頂層和底層的地平面比較完整,能作為一個較好的屏蔽層 來使用。需要注意的是電源層要靠近非主元件面的那一層,因為底層的平面會更完整。因此,EMI 性能要比第一種方案好。

小結:對于六層板的方案,電源層與地層之間的間距應盡量減小,以獲得好的電源、地耦合。但 62mil 的板厚,層間距雖然得到減小,還是不容易把主電源與地 層之間的間距控制得很小。對比第一種方案與第二種方案,第二種方案成本要大大增加。因此,我們疊層時通常選擇第一種方案。設計時,遵循 20H 規則和鏡像層 規則設計

四、八層板的疊層

八層板通常使用下面三種疊層方式

A:由于差的電磁吸收能力和大的電源阻抗導致這種不是一種好的疊層方式。它的結構如下:

1.Signal 1 元件面、微帶走線層

2.Signal 2 內部微帶走線層,較好的走線層(X 方向)

3.Ground

4.Signal 3 帶狀線走線層,較好的走線層(Y 方向)

5.Signal 4 帶狀線走線層

6.Power

7.Signal 5 內部微帶走線層

8.Signal 6 微帶走線層

B:是第三種疊層方式的變種,由于增加了參考層,具有較好的 EMI 性能,各信號層的特性阻抗可以很好的控制

1.Signal 1 元件面、微帶走線層,好的走線層

2.Ground 地層,較好的電磁波吸收能力

3.Signal 2 帶狀線走線層,好的走線層

4.Power 電源層,與下面的地層構成優秀的電磁吸收

5.Ground 地層

6.Signal 3 帶狀線走線層,好的走線層

7.Power 地層,具有較大的電源阻抗

8.Signal 4 微帶走線層,好的走線層

C:最佳疊層方式,由于多層地參考平面的使用具有非常好的地磁吸收能力。

1.Signal 1 元件面、微帶走線層,好的走線層

2.Ground 地層,較好的電磁波吸收能力

3.Signal 2 帶狀線走線層,好的走線層

4.Power 電源層,與下面的地層構成優秀的電磁吸收

5.Ground 地層

6.Signal 3 帶狀線走線層,好的走線層

7.Ground 地層,較好的電磁波吸收能力

8.Signal 4 微帶走線層,好的走線層

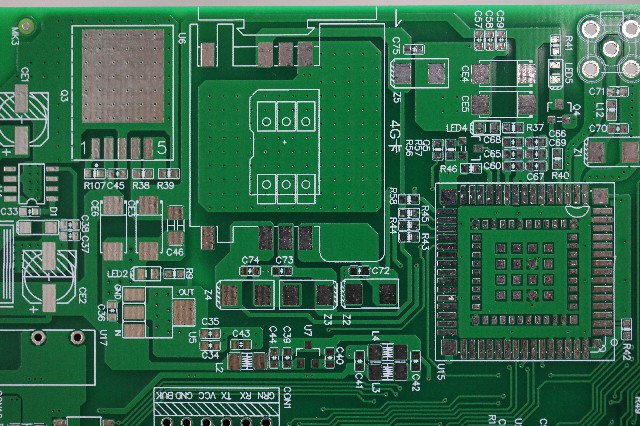

對于如何選擇設計用幾層板和用什么方式的疊層,要根據板上信號網絡的數量,器件密度,PIN 密度,信號的頻率,板的大小等許多因素。對于這些因素我們要綜 合考慮。對于信號網絡的數量越多,器件密度越大,PIN 密度越大,信號的頻率越高的設計應盡量采用多層板設計。為得到好的 EMI 性能最好保證每個信號層都 有自己的參考層。

審核編輯 黃昊宇

-

pcb

+關注

關注

4318文章

23022瀏覽量

396424

發布評論請先 登錄

相關推薦

如何根據貼片疊層電感參數進行選型

谷景揭秘貼片疊層電感精度是不是越高越好

鈣鈦礦疊層電池:Topcon與HJT底電池性能對比研究

PCB疊層結構與阻抗計算筆記分享

PCB疊層設計優化ESD性能設計

PCB疊層設計示例詳解

4層以上的PCB設計,如何選取合適的疊層方案?

DDR電路的疊層與阻抗設計!

DDR電路的疊層與阻抗設計

鈣鈦礦疊層電池知識整理匯總

簡述PCB疊層設計

簡述PCB疊層設計

評論