富士通進一步改進制造工藝,為 ASIC 和 COT 客戶提供世界一流的 65 納米 CMOS 技術。這種極具競爭力的 65 納米技術具有最大化性能和最小化功耗的選項。因此,該技術既適合以性能為導向的應用程序,也適合結合了卓越性能和長電池壽命的移動應用程序。

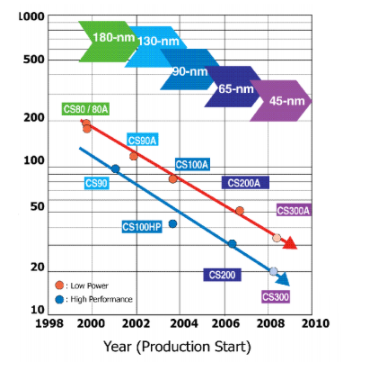

正如公司的技術路線圖(圖 1)所示,與 90 納米技術相比,富士通的 65 納米技術將柵極縮小了 25%。富士通將于 2006 年初開始接受 65 納米技術的流片驗收。

CMOS技術路線圖

富士通 65 納米技術為用戶提供了兩個系列的選擇:

CS200A 用于低功耗/移動使用

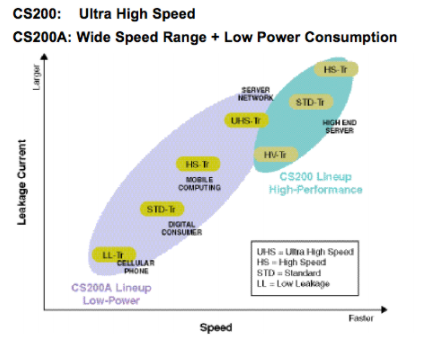

圖 2 說明了這兩個系列的應用范圍。這兩個系列都提供了一系列具有不同泄漏功率/性能點的晶體管,使設計人員能夠混合晶體管類型以實現高性能和低功耗。CS200A 技術提供了種類繁多的晶體管,從用于手機等應用的低泄漏 (LL) 到用于服務器或網絡設備的超高速 (UHS)。

CS200和CS200A晶體管品種

高性能晶體管

CS200 技術的進步包括改進的 CMOS 晶體管配置。具體來說,CS200 晶體管的柵極長度為 30 nm,比 CS100 晶體管的尺寸縮小了 75%。較小的晶體管還使用新的鎳多晶硅/多晶硅堆棧,而不是用于 CS100 晶體管的多晶鈷/多晶硅堆棧。新材料較低的薄層電阻可確保較低的柵極電阻,從而轉化為更高的速度。

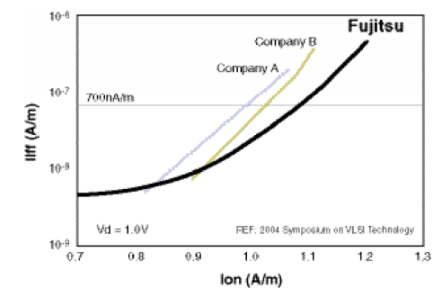

nMOSFET 的 I(on) 和 I(off) 特性

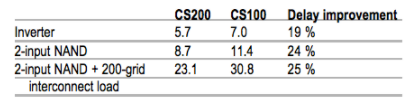

為了說明這種晶體管配置的優勢,圖 3 顯示了 CS200 nMOSFET 的 Ion 和 Ioff 特性以及競爭技術的特性。富士通的 CS200 晶體管在速度和漏電流方面都表現出卓越的特性。一些 CS200 基準電路的 SPICE 仿真顯示速度提高了 20% 到 30%,如下表所示。富士通投入了大量精力來實現這些性能改進,以便在公司自己的高性能服務器中使用。

CS200 電路延遲性能(每門 ps)

編輯:hfy

-

cpu

+關注

關注

68文章

10826瀏覽量

211162 -

服務器

+關注

關注

12文章

9024瀏覽量

85187 -

晶體管

+關注

關注

77文章

9635瀏覽量

137858 -

富士通

+關注

關注

2文章

193瀏覽量

54543

發布評論請先 登錄

相關推薦

基于ZU3EG的低功耗高性能嵌入式AI高性能計算模組

統一工藝和架構,賽靈思28納米FPGA成就高性能和低功耗的完

ADC08B3000低功耗、高性能CMOS模數轉換器數據表

ADC083000單通道、低功耗、高性能CMOS模數轉換器數據表

ADC081500低功耗、高性能CMOS模數轉換器數據表

ADC081000低功耗、高性能CMOS模數轉換器數據表

高性能/低功耗65納米 CMOS技術解析

高性能/低功耗65納米 CMOS技術解析

評論