本應用筆記介紹了 ARM Cortex-M3 處理器的主要特性,并描述了為其開發軟件的不同方面。它還涵蓋了現有 ARM 項目到 Cortex-M3 平臺的遷移。

Cortex-M3

ARM Cortex-M3 是一種高性能、低成本和低功耗的 32 位 RISC 處理器。Cortex-M3 處理器只執行 Thumb-2 指令。它不支持 ARM 指令集。Cortex-M3 處理器基于 ARM 架構 v7-M,擁有高效的哈佛 3 級流水線內核。它還具有硬件劃分和低延遲中斷服務程序 (ISR) 進入和退出。

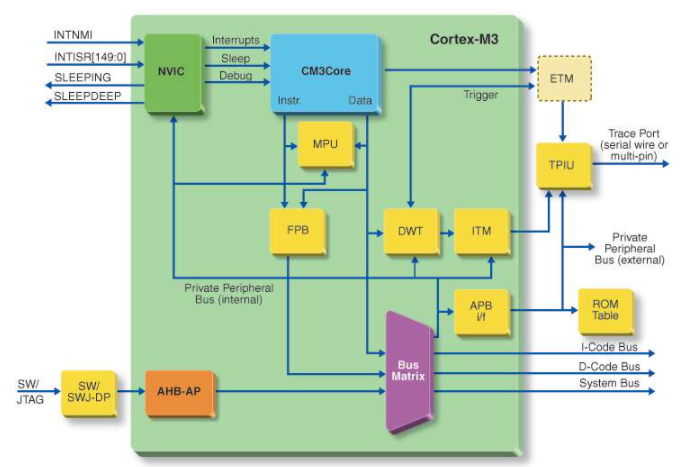

除了 CPU 內核外,Cortex-M3 處理器還包括許多其他組件。其中包括嵌套向量中斷控制器 (NVIC)、可選的內存保護單元 (MPU)、定時器、調試訪問端口 (DAP) 和可選的嵌入式跟蹤宏單元 (ETM)。Cortex-M3 也有一個固定的內存映射。

嵌套向量中斷控制器 (NVIC)

根據芯片制造商使用的實現方式,NVIC 可以支持多達 240 個外部中斷,具有多達 256 個不同的優先級,可以動態重新確定優先級。它同時支持電平和脈沖中斷源。處理器狀態在中斷進入時由硬件自動保存,并在中斷退出時恢復。NVIC 還支持中斷的尾鏈。

在 Cortex-M3 中使用 NVIC 意味著 Cortex-M3 的向量表與以前的 ARM 內核非常不同。Cortex-M3 向量表包含異常處理程序和 ISR 的地址,而不是像大多數其他 ARM 內核那樣包含指令。初始堆棧指針和復位處理程序的地址必須分別位于 0x0 和 0x4。這些值然后在復位時加載到適當的 CPU 寄存器中。

內存保護單元 (MPU)

MPU 是 Cortex-M3 的可選組件。如果包含在內,它會通過強制執行特權和訪問規則來支持保護內存區域。它最多支持八個不同的區域,每個區域可以再分成八個相同大小的子區域。

調試訪問端口 (DAP)

DAP 使用 AHB-AP 接口與處理器和其他外設進行通信。調試端口有兩種不同的支持實現,串行線 JTAG 調試端口 (SWJ-DP) 和串行線調試端口 (SW-DP)。您的 Cortex-M3 實現可能包含其中之一,具體取決于您的芯片制造商使用的實現。

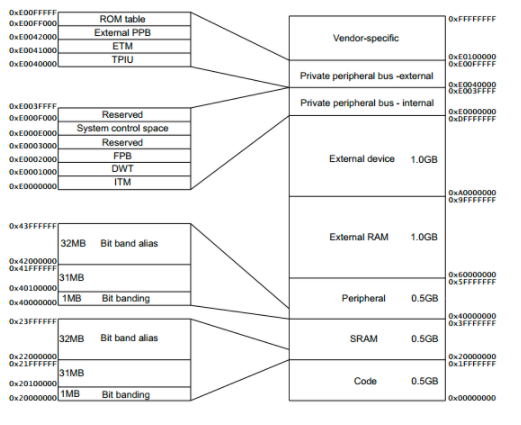

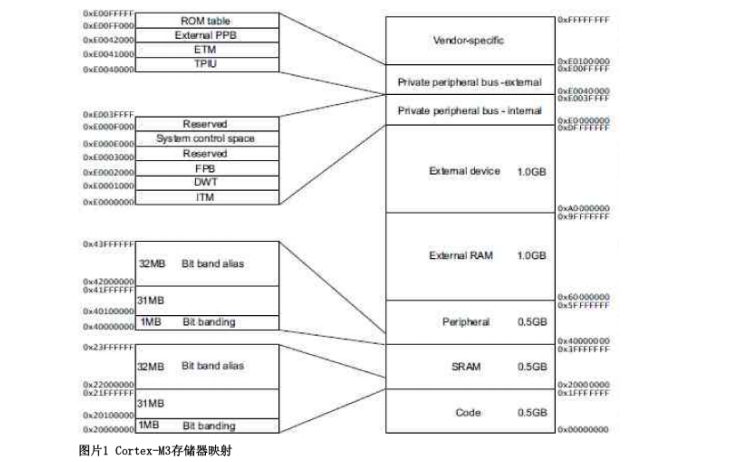

內存映射

與大多數以前的 ARM 內核不同,基于 Cortex-M3 的設備的內存映射的整體布局是固定的。這允許在基于 Cortex-M3 的不同系統之間輕松移植軟件。地址空間被分成許多不同的部分。這在下面的圖 2 中顯示。

編輯:hfy

-

cpu

+關注

關注

68文章

10829瀏覽量

211196 -

定時器

+關注

關注

23文章

3241瀏覽量

114519 -

中斷控制器

+關注

關注

0文章

59瀏覽量

9442

發布評論請先 登錄

相關推薦

Cortex-M3處理器是什么

STM32 的核心Cortex-M3 處理器是什么

ARM Cortex-M3定義指南

STM32系列ARM Cortex-M3微控制器原理與實踐

Cortex-M3 技術參考手冊

選擇ARM處理器,ARM7還是Cortex-M3

Cortex-M3內核的ARM處理器的應用資料說明

Cortex-M3處理器內核與基于Cortex-M3的MCU關系

STM32 的核心Cortex-M3 處理器

ARM Cortex-M3 處理器的主要特性分析

ARM Cortex-M3 處理器的主要特性分析

評論