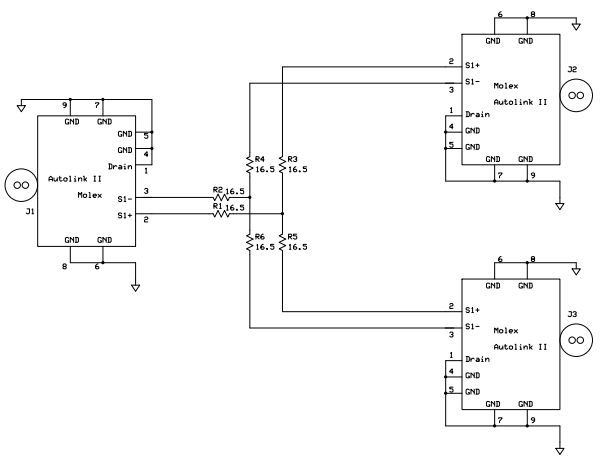

在某些應用中,單個數據源需要將 LVDS 數據發送到兩個目的地。這方面的一個例子是單個視頻源向兩個 LCD 面板發送數據,這可能在汽車后座娛樂系統中找到。傳統上,SERDES 鏈路是點對點的,單個發送器通過電纜或電路板將串行數據發送到單個接收器。如果系統要求將相同的數據發送到兩個目的地,則需要兩條完整的鏈路(4 個 SERDES 芯片和 2 條電纜)。圖 1 中顯示了這樣的一個示例。為方便圖片顯示,顯示器靠近在一起顯示,但在最終應用中可能相距一米或更遠。

客觀的

提出一種允許系統設計人員拆分 LVDS 電纜的技術,以便單個 ISL76341 或 ISL76321 發送器可以驅動兩個接收器。這從 BOM 中消除了一個 SERDES 芯片,并縮短了系統中的總電纜長度。在整個數據路徑中保持 100Ω 差分阻抗環境對于消除反射和保持共模電壓至關重要。由于這是降低成本的標準電路板,因此必須使用設計技術。

分路器設計

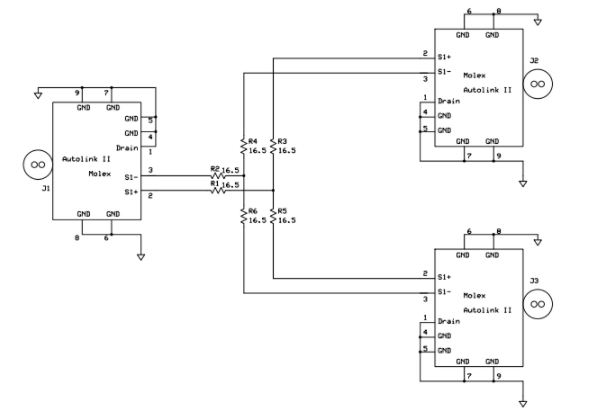

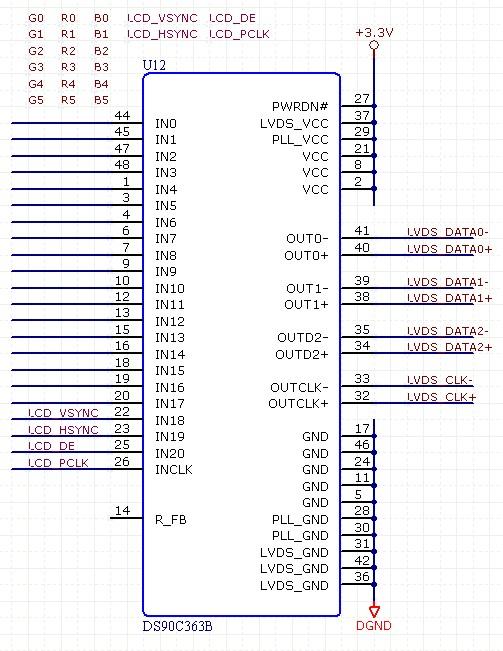

為了實現這些目標,需要在系統中添加一塊電路板,以將 LVDS 信號分成兩個相同的信號。雖然預計會有一些信號損失,但我們希望將其保持在最低限度。必須保持信號完整性,以免 EMI 增加。分線板原理圖如圖 2 所示。

LVDS 分配器原理圖

每個發射器和接收器的阻抗為 100 Ω。分析上支路,我們從 100Ω 開始。當我們添加 R3 和 R4 時,該分支的阻抗為 133Ω。兩個并聯接收器支路的阻抗為 66.5Ω。最后,我們添加了來自發射支路 R1 和 R2 的兩個串聯電阻的 33Ω 電阻,從發射器輸出端看到的總電阻為 99.5Ω。每個分支的分析都是相同的,因此每個 SERDES 芯片都會看到 100Ω 負載。六個 16.5Ω 電阻器是標準的 1% SMT 值。這些電阻器通過的電流很小,因此可以使用任何尺寸的 SMT 電阻器。

電路板設計

分離器可以在 2 層或 4 層板設計中實現。關鍵部分是保持 50Ω 單端和 100Ω 差分傳輸線環境。使這有點挑戰性的事實是,由于信號需要交叉,因此至少需要一對從電路板的頂層到底層。對于 4 層板,通過使用內部層作為參考平面 (GND) 和信號的頂層和底層,更容易保持阻抗控制。信號路徑中所需的過孔只會增加少量的電感和特性阻抗的微小變化,可以忽略不計。

編輯:hfy

-

串聯電阻

+關注

關注

1文章

190瀏覽量

14767 -

接收器

+關注

關注

14文章

2458瀏覽量

71797 -

lcd

+關注

關注

34文章

4411瀏覽量

167093 -

lvds

+關注

關注

2文章

1036瀏覽量

65705 -

發送器

+關注

關注

1文章

258瀏覽量

26797

發布評論請先 登錄

相關推薦

FPGA編程LVDS信號圖像處理技術

信號分離電路(ppt)

什么是lvds信號

LVDS信號電平特性

LVDS信號的PCB設計

LVDS分離器簡化高速信號分配

LVDS技術原理和設計簡介

LVDS信號的PCB設計和仿真分析

遠場渦流缺陷信號盲分離技術研究

淺談分裂LVDS信號設計技術

淺談分離LVDS信號設計技術

淺談分離LVDS信號設計技術

評論