本應用報告介紹了實現 IDT 基于 PLL 的零延遲緩沖器的輸入參考時鐘和輸出時鐘之間定義的相位關系的不同方法。該報告重點介紹了 PLL 反饋環路中不同走線長度和反饋時鐘輸入端的電容負載對生成早期(或晚期)時鐘的影響。早期時鐘定義為輸出時鐘的相位相對于參考輸入時鐘提前的情況。

簡介

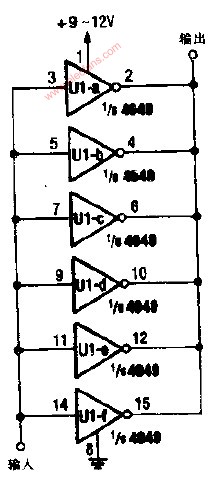

時鐘驅動器架構有兩種主要類型:緩沖器型和帶鎖相環 (PLL) 的反饋型。在緩沖器型(非 PLL)時鐘驅動器中,輸入波通過器件傳播并由輸出緩沖器“重新驅動”。輸出信號直接跟隨輸入信號,并帶有一些器件傳播時間延遲 (tPD)。

反饋型時鐘驅動器利用來自設備時鐘輸出之一的附加反饋輸入路徑。反饋路徑可以在設備內部或外部。對于外部反饋,PCB 上的走線用于將輸出引腳連接到反饋輸入引腳。這種類型的設備通常基于一個或多個 PLL,這些 PLL 用于對齊反饋和參考輸入的相位和頻率。可以補償板級走線長度不匹配,以實現輸入和輸出時鐘之間定義的偏移關系。輸出可以有選擇地進行分頻、相乘或反相,同時仍然保持非常低的輸入到輸出偏差。

什么是鎖相環?

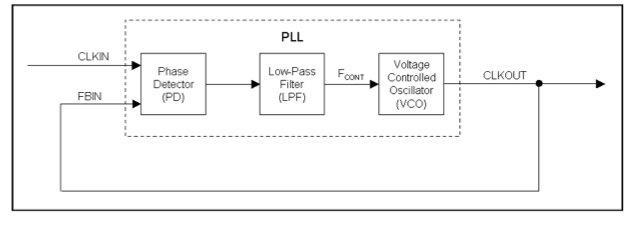

基本的 PLL 是一種反饋系統,它接收輸入的振蕩信號并生成以輸入信號的整數倍或分數倍數振蕩的輸出波形。它由相位或頻率檢測器、濾波器和壓控振蕩器組成,如圖 1 所示。為了使 PLL 將參考輸入 (CLKIN) 與輸出對齊,必須將輸出反饋到反饋(FBIN) PLL 的輸入。

鎖相環 (PLL) 框圖

相位檢測器 (PD) 通常評估 CLKIN 輸入相對于 FBIN 輸入的上升沿。如果 CLKIN 輸入超前 FBIN 輸入,表明壓控振蕩器 (VCO) 的運行速度比理想情況要慢,則 PD 會產生一個在 CLKIN 輸入的上升沿觸發并持續到上升沿的“Pump Up”信號FBIN 輸入。這個“上泵”脈沖迫使 VCO 運行得更快,并減少了 CLKIN 輸入和 FBIN 輸入之間的時間差。

如果 FBIN 輸入超前于 CLKIN 輸入,則 PD 會產生一個“抽空”信號,該信號在 FBIN 輸入的上升沿觸發并持續到 CLKIN 輸入的上升沿。“Pump Down”脈沖強制 VCO 運行得更慢,并減少 FBIN 輸入和 CLKIN 輸入之間的時間差。

編輯“hfy”

-

鎖相環

+關注

關注

35文章

576瀏覽量

87545 -

濾波器

+關注

關注

158文章

7596瀏覽量

176581 -

緩沖器

+關注

關注

6文章

1903瀏覽量

45327 -

pll

+關注

關注

6文章

767瀏覽量

134856 -

時鐘驅動器

+關注

關注

0文章

32瀏覽量

13788

發布評論請先 登錄

相關推薦

零延時緩沖器

如何在ISE中延遲緩沖區?

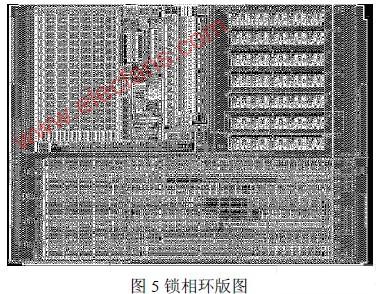

用于零延遲緩沖器的PLL設計

Cypress高性能零延遲緩沖器面向高速通信和消費設備

緩沖器,緩沖器是什么?

緩沖器,緩沖器基本原理是什么?

基于CSMC工藝的零延時緩沖器的PLL設計

使用IDT時鐘緩沖器提升應用設計

什么是時鐘緩沖器(Buffer)?時鐘緩沖器(Buffer)參數解析

如何在TDMoP產品上使用抖動緩沖器來補償數據包延遲變化

基于 PLL 的零延遲緩沖器的系統應用

基于 PLL 的零延遲緩沖器的系統應用

評論