本文檔的目的是幫助用戶了解如何在降低噪聲性能的情況下設計良好的PCB布局。在采取本文檔中提到的對策后,有必要進行全面的系統評估。本文檔提供了有關RL78 / G14樣品板的說明。

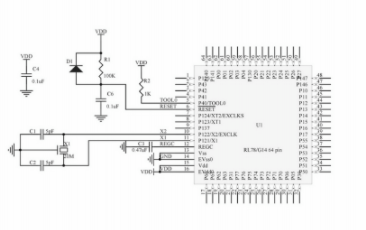

測試板的說明。本節顯示了推薦布局的示例,不建議使用的電路板均使用相同的原理圖和組件制作而成。僅PCB布局不同。通過推薦的方法,推薦的PCB板可以實現更高的降噪性能。推薦的布局和不推薦的布局均采用相同的原理圖設計。圖1顯示了MCU周圍的電路原理圖。

MCU周圍電路原理圖

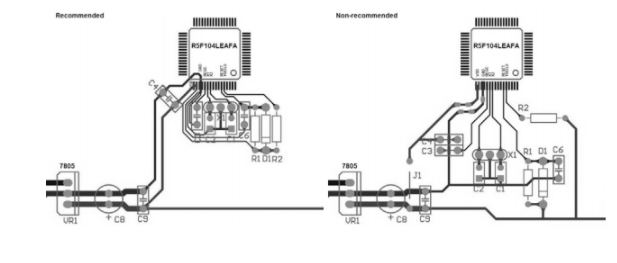

兩個測試板的PCB布局。

本節顯示了推薦布局和非推薦布局的示例。PCB布局應按照推薦的布局進行設計,以降低噪聲性能。下一節將說明為什么建議使用圖1左側的PCB布局的原因。圖2顯示了兩個測試板的MCU周圍的PCB布局。

推薦布局(左)和非推薦布局(右)

推薦和非推薦布局之間的差異

本節介紹了推薦布局和非推薦布局之間的主要區別。

VDD和VSS的接線。推薦板的VDD和VSS布線與主電源入口處的外圍電源布線分開。并且推薦板的VDD布線和VSS布線比非推薦板更靠近。特別是在非推薦板上,MCU的VDD布線通過跳線J1連接到主電源,然后通過濾波電容器C9。

振蕩器問題。推薦板上的振蕩器電路X1,C1和C2比非推薦板上的更靠近MCU。推薦板上從振蕩器電路到MCU的布線比不推薦的布線短。在非推薦板上,振蕩器電路不在VSS接線的端子上,也沒有與其他VSS接線分開。

旁路電容器。推薦板上的旁路電容器C4比非推薦板上的電容器更靠近MCU。并且從旁路電容器到MCU的布線比不推薦的布線短。特別是在非推薦板上,C4的引線沒有直接連接到VDD和VSS干線。

編輯:hfy

-

mcu

+關注

關注

146文章

17002瀏覽量

350328 -

pcb

+關注

關注

4317文章

23010瀏覽量

396353

發布評論請先 登錄

相關推薦

如何在降低噪聲性能的情況下設計良好的PCB布局

如何在降低噪聲性能的情況下設計良好的PCB布局

評論