本應用筆記介紹了運算放大器如何驅動電容性負載。為了更深入地研究該主題,將模擬作為表示數據的一種方式進行顯示。本說明將幫助工程師設計更有效的模擬電路,從而能夠克服常見的局限性和獲得更好輸出的障礙。

從理想到現實:從基礎開始

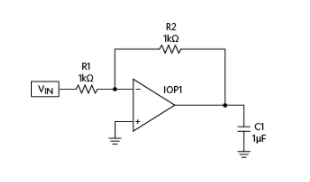

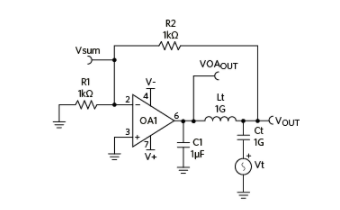

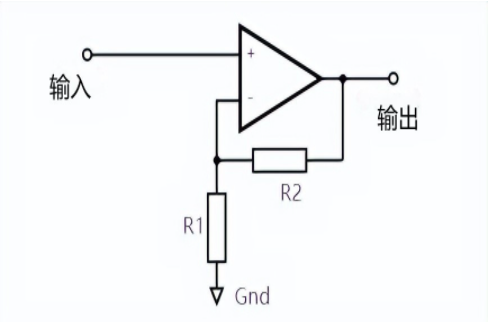

有經驗的人知道,運算放大器驅動電容性負載的最常見問題是運算放大器周圍環路的穩定性。圖1顯示了一個簡單的“理想”運算放大器電路,其增益為-1來驅動1 μF電容性負載。

現在,如果這個運算放大器是理想的,它將具有零輸出阻抗,并且負載電容不會對其周圍環路的穩定性產生影響。正如我希望您已經知道的那樣,理想的運算放大器在現實世界中根本不可用。

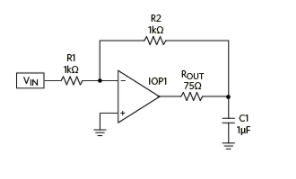

任何實際的運算放大器都有一定的輸出阻抗。為了簡單起見,我們假設輸出阻抗是一個電阻。圖2明確顯示了該運算放大器的輸出電阻。

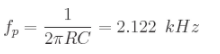

現在,我們有了一個帶有ROUT和C1的RC低通濾波器。產生的極點頻率為:

理想的運算放大器具有無限的增益,而真正的運算放大器具有非常高的有限的DC增益。它還在一個相當低的頻率上具有一個極點,導致運算放大器的增益下降,最終在更高的頻率下達到單位增益。該極點稱為主導極點。在設計良好的運算放大器中,總是有更多的極點,所有極點的頻率都高于單位增益頻率。對于大多數實際目的,我們可以僅考慮這些極點中的第一個進行分析。

不要“迷失在香料中”

在我們進一步研究之前,我想提一提關于Spice模型的實際使用的重大警告。在整個應用筆記中,我們將使用Spice模擬代替實驗室中的實際工作。我之所以經常這樣做,是因為它使讀者能夠在計算機上快速使用基本電路和概念。這也是在廣泛的范圍內清楚地展示基本概念和特征的一種更有效的方法。盡管如此,讀者也必須提防使用模擬器的任何人,并且要避免相信模擬結果是絕對事實。

Spice僅提供最多與我們提供的輸入一樣準確的結果,例如真實組件的模型以及我們如何設置和使用它。如果我們不利用我們的實踐知識和健康的懷疑態度,香料可能會并且將產生不正確的結果。

最終,如果您希望在Spice中正常工作,則必須減少您在Spice中所做的任何事情。

讓我們開始仿真

我們正在使用一個參數化的運算放大器模型,該模型是TINA標準庫的一部分,TINA是本應用筆記中使用的模擬器。圖3顯示了可調參數表。

該模型使我們能夠更改運算放大器的特性以適應我們的需求,而無需花費時間尋找具有所需精確規格的真正運算放大器。

現在,我們將使用默認參數。對我們來說關鍵的是:

開環增益:200k(106 dB)

主導極點:5 Hz

第二極點:10 MHz

輸出電阻:75Ω

請注意,前兩項將增益帶寬乘積(GBWP)確定為1 MHz(200k×5 Hz)。

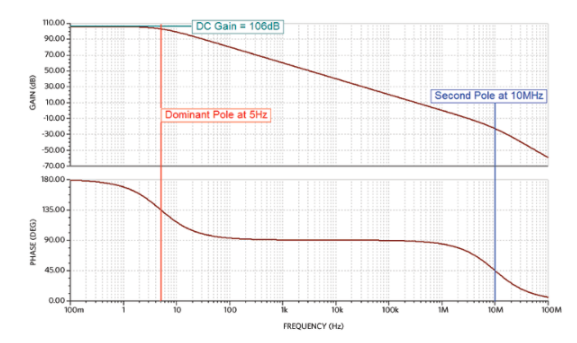

圖4顯示了運算放大器的開環增益和相位。

盡管很難在這種規模上目視分辨,但低頻增益確實如所承諾的是106 dB。然后,我們在5 Hz處看到一個極點,用紅色光標指示。現在給您一個提示:通過查看-45°點的相位圖而不是增益圖的-3 dB點,可以更容易地確定單個極點的精確位置。在這種情況下,我們從180°相位開始(使用運算放大器反相輸入以確保與隨后的相位保持一致),因此-45°點為135°。

我們還看到第二個極點位于10MHz,用藍色光標指示。

電容負載如何工作?

既然我們知道了運放的顯著特性,我們將回到容性負載電路(圖1)。我們已經知道我們的運算放大器的極點為5 Hz,因此大約50Hz時,我們只有90°的裕度可以工作。回想一下,1 μF的容性負載與我們的75Ω輸出電阻相結合,使我們在2.122 kHz處得到另一個極點。這意味著到22 kHz左右,我們應該用盡相位裕量。如果我們這里還剩下任何環路增益,那么電路將非常不穩定。讓我們來看看。

圖5顯示了與圖1相同的電路中的參數化運算放大器,但增加了一些新的組件,特別是Vt,Ct和Lt。

需要這些附加組件來測量環路,而又不會破壞環路的直流路徑。從理論上講,使用完美的運算放大器,我們可以將反饋電阻與運算放大器的輸出斷開,將信號注入到電阻的此斷開端,然后測量運算放大器的輸出以了解環路增益是多少。 。但是,如果環路沒有閉合(至少對于DC而言),那么小的偏移量將導致輸出飽和。請記住:我們的運算放大器的DC增益為200k,因此僅1 mV的偏移就可產生200 V的輸出。

我們在運算放大器的輸出和反饋電阻之間放置一個電感值Lt,該電感值必須大,以確保負載電容與運算放大器保持一致,以便其與運算放大器的輸出電阻發生反應。然后,我們使用與信號源串聯的大容量電容器Ct將信號注入反饋電阻的輸出端。這些較大的分量值確保了對于DC而言,環路仍然是閉合的,但是這些增加的分量將不會影響感興趣頻率下的測量。這種方法實際上僅在“香料之地”中有效,因為我們可以擁有具有如此大價值的組件。

由于我們正在驅動該電路的輸出,因此R1的正常輸入已接地。現在是進行快速仿真的時候了(圖6)。

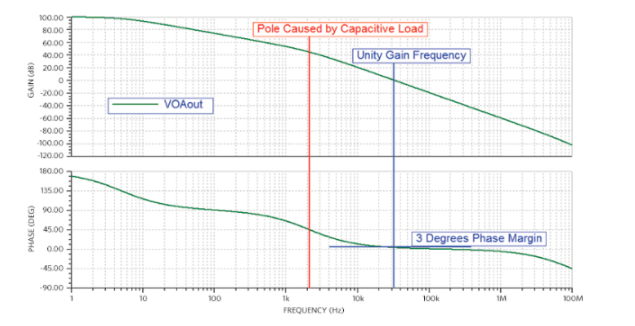

圖6中的紅色光標指示由電容性負載引起的極點位置。藍色光標位于單位增益交叉處,指示3°的相位裕度。當然,這對于穩定性很糟糕。

一些最終觀察結果

現在,下一步當然是在實驗室中使用真實電路驗證所有這些內容,以確保我們獲得預期的性能。作者在多年前就建造了該電路,并驗證了其正常工作。

在當今與芯片上的數百萬個晶體管高度集成的今天,有時我們仍然需要使用單個分立晶體管來完成工作。但是,要使電路正常工作,我們必須依賴于基本電子學的基本知識。一直需要這些基礎知識,好奇心和健康的懷疑態度,但如今,使用我們先進的產品和工具,這些問題變得尤為重要。

編輯:hfy

-

運算放大器

+關注

關注

215文章

4900瀏覽量

172607 -

晶體管

+關注

關注

77文章

9641瀏覽量

137876 -

輸出阻抗

+關注

關注

1文章

102瀏覽量

12316

發布評論請先 登錄

相關推薦

運算放大器振蕩的解決辦法

運算放大器如何抑制噪聲

運算放大器的輸入電阻怎么算

運算放大器和儀表放大器的區別

公式+案例 搞定同相運算放大器

運算放大器如何驅動電容性負載

運算放大器如何驅動電容性負載

評論