當(dāng)讀者和DI貢獻(xiàn)者Jim Brannan建議編寫(xiě)他的base-3 DAC設(shè)計(jì)時(shí),我感到非常高興。像Charlieplexing一樣,他的想法是利用三態(tài)輸出來(lái)從引腳中擰出更多的信息,而不僅僅是“ 0”和“ 1”!例如,一個(gè)四位的DAC理論上可以產(chǎn)生34(81)個(gè)電平,而不是通常的16個(gè)電平。五個(gè)位實(shí)際上將與常規(guī)的八位性能(243個(gè)電平)相匹配,盡管精確的實(shí)現(xiàn)可能會(huì)更多。比常規(guī)的二進(jìn)制DAC困難,尤其是隨著分辨率的提高。

像往常一樣,我到處搜尋Google的現(xiàn)有技術(shù),是的,發(fā)現(xiàn)有兩個(gè)頁(yè)面描述了類(lèi)似的野獸。吉姆看了一眼,并決定他沒(méi)有什么要補(bǔ)充的,所以……沒(méi)有“設(shè)計(jì)理念”。但是我覺(jué)得這個(gè)概念還是值得宣傳的。吉姆也有自己獨(dú)特的方法。

在繼續(xù)之前,也許花點(diǎn)時(shí)間想象一下如何實(shí)現(xiàn)三元DAC。也許您會(huì)想出一個(gè)新的變體,然后再將下面的想法弄清楚。

好的,這是我自己的實(shí)現(xiàn)想法:

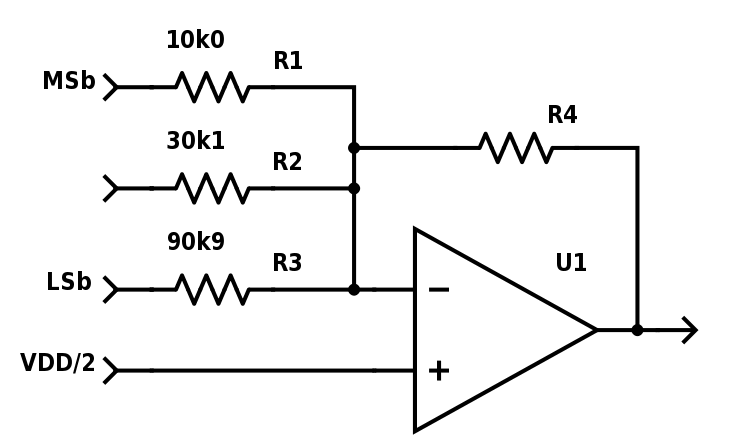

圖1 具有中間電源基準(zhǔn)的求和放大器實(shí)現(xiàn)了一個(gè)3基數(shù)DAC。

實(shí)際上,我最初的想法是在-VDD處輸入放大器的(+)輸入,但隨后我意識(shí)到一個(gè)浮動(dòng)輸出將被拉向該負(fù)電源,可能鉗位在-0.7V,并且通常不起作用。VDD/ 2參考表示0,1,2狀態(tài)對(duì)應(yīng)于0,Z,1輸出(“ Z”表示高阻抗和/或輸入模式)。

另一個(gè)硬件問(wèn)題是,當(dāng)輸入處于中軌時(shí),某些微控制器可能會(huì)消耗過(guò)多的電源電流,因此請(qǐng)確認(rèn)這不是問(wèn)題,禁用數(shù)字輸入模式,或者使用可以設(shè)置為模擬輸入的引腳。

驅(qū)動(dòng)三進(jìn)制DAC將需要查找表或二進(jìn)制到三進(jìn)制的轉(zhuǎn)換例程。在大多數(shù)情況下,除非可以在一個(gè)寫(xiě)周期內(nèi)設(shè)置引腳模式和值,否則更改其設(shè)置后,DAC輸出就會(huì)出現(xiàn)毛刺。

吉姆(Jim)中止的“設(shè)計(jì)理念(Design Idea)”使用無(wú)源“ R-2R”型DAC,他編寫(xiě)了軟件來(lái)搜索許多電阻器組合。無(wú)法創(chuàng)建完美的線性DAC,他的解決方案是使用查找表,并且性能有些不均勻。

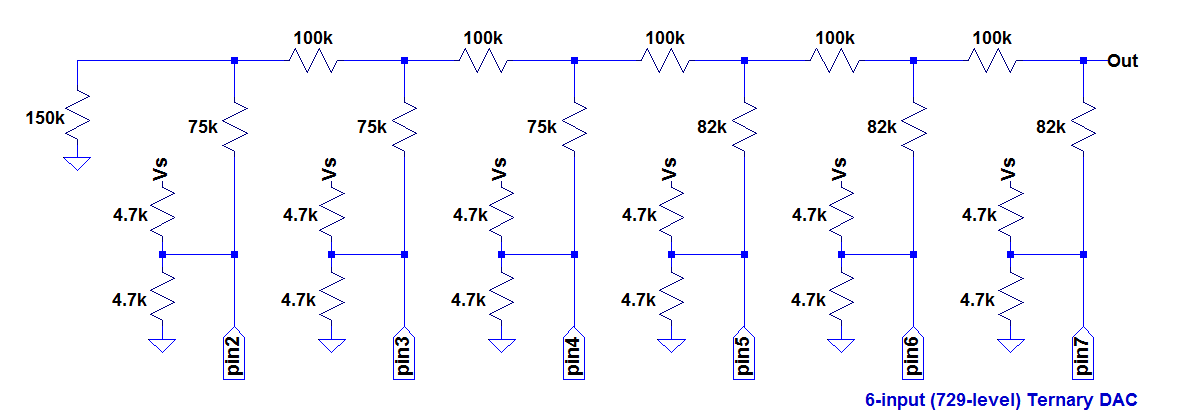

喬什·鮑曼(Josh Bowman)在他的博客中描述了自己對(duì)3進(jìn)制DAC的看法。結(jié)構(gòu)為R-2R-ish,其中較小值的電阻器將電源分開(kāi),以生成中間電平的“ Z”值。

圖2 喬什·鮑曼(Josh Bowman)的無(wú)源三元DAC

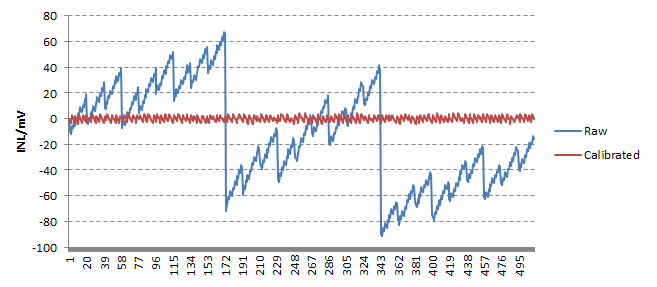

如下所示,設(shè)計(jì)中存在冗余值,可以進(jìn)行校準(zhǔn)。

圖3原始和校準(zhǔn)的INL性能

在此Arduino論壇上還討論了一些基于base-3的DAC設(shè)計(jì),這些是上述設(shè)計(jì)的變體。

如果嘗試三元DAC實(shí)現(xiàn),請(qǐng)?jiān)谙旅嬷匦聰⑹瞿慕?jīng)驗(yàn)。我們希望知道這一點(diǎn)。記住,與所有這些簡(jiǎn)單的DAC設(shè)計(jì)一樣,電源噪聲會(huì)傳遞到輸出。

編輯:hfy

-

放大器

+關(guān)注

關(guān)注

143文章

13554瀏覽量

213143 -

電阻器

+關(guān)注

關(guān)注

21文章

3763瀏覽量

62051 -

Google

+關(guān)注

關(guān)注

5文章

1758瀏覽量

57418 -

dac

+關(guān)注

關(guān)注

43文章

2272瀏覽量

190852 -

電源噪聲

+關(guān)注

關(guān)注

3文章

149瀏覽量

17467

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

lvds接口如何實(shí)現(xiàn)高分辨率顯示

過(guò)采樣ADC12以獲得更高分辨率

使用MSP430高分辨率定時(shí)器的PWM DAC

高分辨率音頻和傳統(tǒng)音頻區(qū)別

鼎陽(yáng)科技|高分辨率產(chǎn)品增長(zhǎng)39.42%,引領(lǐng)高端市場(chǎng)新浪潮!

什么是高分辨率示波器?它有哪些優(yōu)勢(shì)?

Moritex 5X 高分辨率遠(yuǎn)心鏡頭 助力晶圓檢測(cè)

高管洞察:高分辨率音樂(lè)需要高分辨率揚(yáng)聲器

高分辨率音頻和普通音頻之間的區(qū)別

EVAL_PASCO2_SENSOR為什么無(wú)法從較低的分辨率高速獲得更高的分辨率?

如何使用SPU實(shí)現(xiàn)MUSIC或ESPRIT算法以獲得超高分辨率?

使用傅里葉疊層成像對(duì)運(yùn)動(dòng)物體進(jìn)行高分辨率成像

如何實(shí)現(xiàn)更高分辨率,更少的位三元DAC

如何實(shí)現(xiàn)更高分辨率,更少的位三元DAC

評(píng)論