目前,在建筑物早期火災監測和報警上,還是一直沿用有線網絡的方式,其線路遍布在建筑內,初裝成本高,同時線路本身也是很大的火災隱患。因而新型的無線火災監測系統應運而生,該系統安裝方便、快捷,且其成本更為低廉,有更大的應用空間。微控制器是火災監測系統的核心部件之一,通用的微處理器和微控制器不能滿足無線火災監測系統中節點主控芯片低功耗、低成本的要求。

為了掌握無線火災監測系統的核心技術,建立擁有自主知識產權的軟硬件平臺,推動我國無線火災監測系統的發展,有必要開發出針對無線火災監測系統的微處理器。本文完成了一款專用于火災檢測系統的微控制器芯片的物理設計。

1 SW-A芯片的架構

SW-A芯片是一款基于ARM Cortex-M0的專于無線火災檢測系統的專用數模混合型控制器芯片,總線采用AMBA AHB、APB 雙總線架構,工作頻率最高可達50 MHz,支持多級內部分頻,待機狀態下也可以極低的頻率運行;內置一個高采樣率的12位逐次逼近的8通道ADC,最多可依次對來自8個傳感器(如溫度傳感器、煙霧傳感器、光強傳感器等)的信號直接進行采樣、轉換、保存,檢測主程序可任意讀取目標傳感器對應的采樣數據進行處理、判斷是否發生火災。

內置18 KBSRAM,可靈活切換作為FLASH、RAM使用,滿足火災監測和簡易處理程序的存儲。支持ISP(在系統編程)操作和IAP(在應用編程)操作,既便于火災監測主程序的更新升級,又便于軟件編寫優化。接口包括工業標準的UART 接口、SSI 通信接口(支持SPI、MicroWire 及SSI 協議),還有3 組(6 通道)PWM,豐富的接口和功能模塊使該款芯片在功能拓展方面有較大潛力。

2 SW-A芯片的物理設計

2.1 采用的物理設計流程

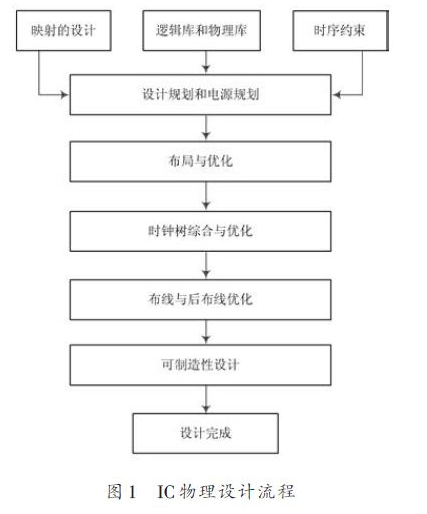

SW-A芯片的物理設計借助Synopsys公司的EDA工具IC Compiler 進行,采用IC Compiler 典型的設計流程。基于臺積電(TSMC)180 nm CMOS工藝進行。物理設計準備就緒后(設計邏輯庫、設置物理庫、設置TLU-Plus相關文件以及設置讀入的門級網表與標準延時約束),即可開始物理設計,依次完成設計規劃(Designplanning)、布局(Placement)、時鐘樹綜合(Clock tree Syn-thesis)、布線(Routing)直至設計完成(Chip Finish)。

2.2 設計規劃

設計規劃(Design Planning)是芯片物理設計中非常重要的一步;主要包括布圖規劃(Floorplan)電源規劃(Powerplant)。

通常情況下,在布局開始之前,設計者往往需要花費大量的時間來進行布圖規劃(Floorplan)和電源規劃(powerplan),設計規劃的好壞直接決定芯片的功耗、標準單元的擁塞的、時序收斂、電源穩定性等。所以設計規劃是整個物理設計過程中反復次數最多、手動設計最多的一步。

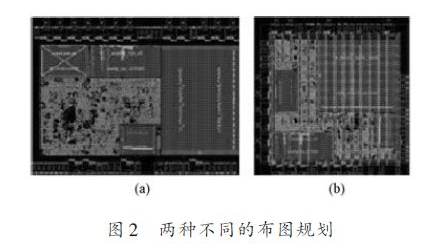

布圖規劃(Floorplan)要完成IO 排布、PAD 擺放、Macro(包括模擬模塊、存儲單元等)的定位以及芯片的形狀、擁塞度(Congestion)和面積等的設定。作為一款面向用戶的控制芯片,IO 的排布必須綜合考慮用戶的需求與設計的要求,不同功能PAD 的縱橫向尺寸也不同。本文將縱橫兩向尺寸均較大的PAD置于芯片的南北兩邊,將單向尺寸較小的PAD 置于芯片的東西側且大尺寸邊朝向南北(見圖2(a)),相比較于將雙向尺寸均較大PAD 置芯片的四周(見圖2(b)),這樣的設計非常有效的減小了芯片的面積。

本芯片需要定位的Macro 有SRAM、ROM、ADC 以及ANALOG_TOP,本文綜合考慮它們與IO 的位置關系將它們定位于芯片的四周,這樣可以芯片中保留成片的空白區域來放置標準單元。為了保證Macro與PAD 及標準單元之間的互聯線,在每個Macro的四周這只一個空白區,這個區域內任何情況不允許擺放標準單元。具體命令如下:

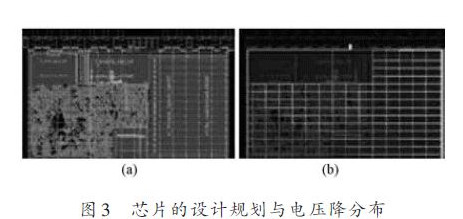

本芯片在放置標準單元和Macro 的核心區與PAD之間設計40 μm 的預留區,用于擺放電源環(PowerRing)及互聯走線。為防止標準單元重疊放置,用命令可保證標準單元只能置于高度大于10 μm 的通道內。設置好芯片布圖規劃可使用命令creat_fp_placement進行預布局。本芯片使用TSMC 180 nm 工藝設計生產,要求工作電壓為1.8 V,可容忍最大電壓波動為±10%,所以本文在進行電源規劃時,綜合考慮了芯片的供電需求、互聯線造成的電壓降(IR-Drop)及較小的電源網絡面積,設計了兩個電源環(Power ring)和縱橫各14條電源帶(Strap)。經過分析電源網絡(Analyze Pow-er Network),本設計最大的IR-Drop 為29.7 mV.圖3(a)是芯片的設計規劃,圖3(b)是芯片的電壓降分布圖。

2.3 布局

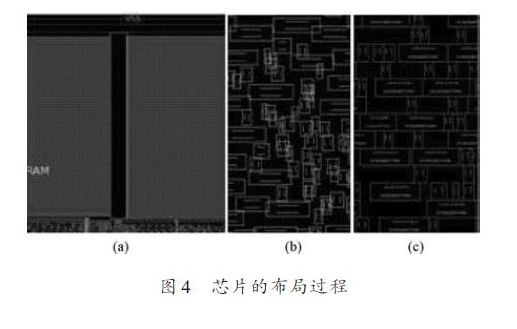

布局(Placement)的好壞是決定芯片物理設計成敗的關鍵。布局的主要任務是完成設計中標準單元的擺放和修復建立時間(setup time)。布局正式開始之前需使用命令check_physical_design命令檢查布局準備是否完成,必須保證:所有Hard Macro 和IO 等的位置以固定;設計中所有邏輯pin和物理pin一一對應;所有的邏輯單元都有與之對應的物理單元;設計中所有單元的尺寸都已固定。為了方便互聯走線,在開始擺放標準單元之前,可以將芯片內特定區域設置為布局限制區(Place-ment Blockage)。ICC工具多種形式的限制,如禁止粗略布局時擺放標準單元、只允許布局優化時擺放標準單元、只允許布線等;本設計中設置了多處布局限制區,以方便ADC、ANALOG_TOP 等與IO 之間的連線(見圖4(a))。

布局準備就緒后可使用命令place_opt配合附加約束進行布局,該命令執行錯略布局(coarse place)、高扇出網絡合成(high-fanout net synthesis)、物理優化(physicaloptimization)直至合法化(legalization),由前三步確定單元的位置(見圖4(b)),通過合法化最終將標準單元正確的擺放在計算好的位置上(見圖4(c))。本文物理設計的具體命令如下:

要求工具對除關鍵時鐘路徑外的其他面積進行修復,努力程度高,通過選項“-congestion”控制工具盡可能的降低芯片的擁塞度以便利后續布線,通過選項“-pow-er”控制工具優化泄漏功耗、動態功耗并且進行低功耗布局。

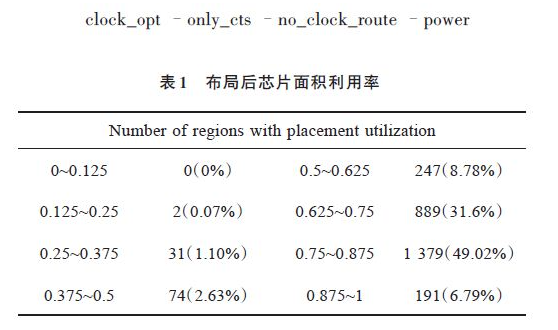

完成布局后芯片的面積利用率如表1所示,擁塞度的集中在0.625~0.875之間,擁塞度適中,既沒有因為芯片利用率過低而浪費芯片面積,也不會因為擁塞度過大而導致后續設計困難甚至重新設計。

2.4 時鐘樹綜合

時鐘樹綜合(Clock Tree Synthesis)的主要任務之一就是將時鐘偏差控制在可接受范圍內,保證芯片高效無誤的工作。本芯片的時鐘樹綜合策略如下:時鐘樹的邏輯綜合(clock-cts)、時鐘樹的物理綜合(clock-psyn)以及時鐘樹的布線(clock-route)。時鐘樹的邏輯綜合階段只完成兩項工作:通過計算各條時鐘路徑上的延遲,得到需要插入緩沖器(buffer、inverter)的位置及尺寸(由-only_cts命令選項控制);由于時鐘網絡的功耗占總功耗的比重非常大,所以在時鐘樹綜合時必須進行功耗優化(-power)此階段并不進行布線。具體命令如下:

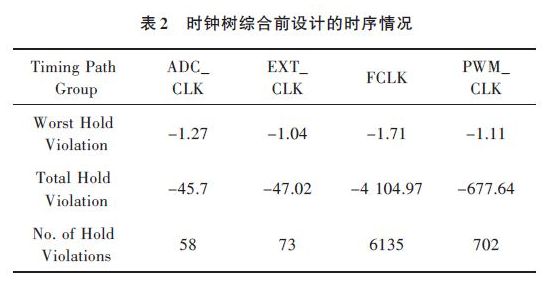

時鐘樹的物理綜合階段將插入的緩沖器擺放至準確的位置,進行RC提取,參照延遲約束文件(SDC)檢查時鐘網絡的的最大插入延遲、最小插入延遲、最大時鐘偏差以及最大轉換時間等并對設計中出現hold違反進行修復,為了便利非時鐘網絡布線,此時需要增加-ar-ea_recovery選項,以減小連線面積,此階段依然對功耗進行優化。在完成時鐘樹布線時,本文采用arnoldi模型來精確計算時鐘樹的延時并15次循環迭代法進行時鐘布線。表2是時鐘綜合前本設計的時序情況,顯而易見有多條關鍵路徑并存在較多建立時間違反;完成時鐘樹綜合后再進行時鐘檢查,未發現時鐘違反,表示時鐘樹綜合完成。

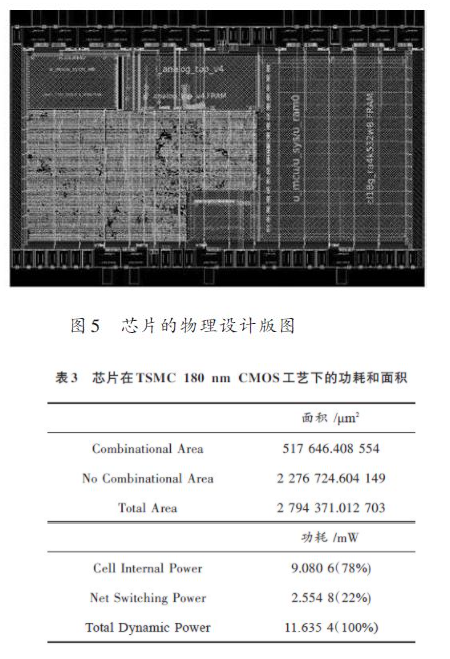

2.5 布線與芯片完成

本文將布線及其優化分開來做,首先在初始布線階段完成全局布線(global routing)、詳細布線(detail rout-ing)和檢查與修正(search&repair),然后采用拓撲算法對布線進行優化,同時對電流漏功耗進行優化。為了防止天線效應的發生,在芯片完成階段對芯片進行了天線效應修復設計,此時芯片中依然存在空白區域,需要填充filer 以滿足DRC 的要求。圖5 是該芯片的物理設計版圖,表3 是該芯片的面積與功耗,可見總面積為2 794 371.012 703 μm2,總功耗為11.635 4 mW.經過仿真后證明芯片于50 MHz時鐘頻率下正常工作,滿足設計要求,證明本次設計是正確有效的。

3 結語

本文基于TSMC 180 nm 工藝完成了一款用于無線火災監測系統中的微處理器芯片的物理設計,采用不同策略分別完成芯片的布圖規劃、布局、時鐘樹綜合及布線等設計步驟后得到了該芯片的版圖及面積、功耗等報表,物理設計后芯片的各項設計指標均滿足設計要求,證明了該芯片物理設計的正確性。

編輯:hfy

-

微控制器

+關注

關注

48文章

7341瀏覽量

150144 -

ARM

+關注

關注

134文章

8967瀏覽量

365074 -

TSMC

+關注

關注

3文章

177瀏覽量

84352 -

微處理器

+關注

關注

11文章

2221瀏覽量

81988

發布評論請先 登錄

相關推薦

清溢光電:已實現180nm節點掩膜版量產 佛山基地2025年末遷入設備

嵌入式微處理器的分類 嵌入式微處理器的種類和型號

嵌入式微處理器的定義與發展 嵌入式微處理器種類和型號

嵌入式微處理器的類型與特點 嵌入式微處理器技術的優缺點

嵌入式微處理器有哪幾類 嵌入式微處理器包含哪些重要參數

嵌入式微處理器的功能 嵌入式微處理器原理與應用

什么是嵌入式微處理器? 嵌入式微處理器的區別

主流嵌入式微處理器的結構與原理是什么 常見的嵌入式微處理器類型包括

微處理器屬于專用集成電路嗎對嗎

什么是嵌入式微處理器?嵌入式微處理器有哪些?

嵌入式微處理器的原理和應用

微處理器芯片發展歷程及行業競爭格局簡述

基于TSMC 180nm工藝的微處理器芯片的物理設計

基于TSMC 180nm工藝的微處理器芯片的物理設計

評論