眾所周知合理的層疊結(jié)構(gòu)和連續(xù)的參考平面能夠很有效的抑制EMI問題,但有時(shí)候設(shè)計(jì)就涉及到模擬數(shù)字信號(hào)隔離的問題。

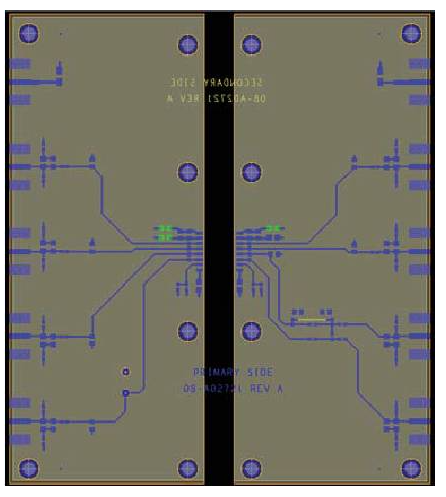

圖1

圖1是一個(gè)電源轉(zhuǎn)換芯片,一邊為數(shù)字信號(hào),一邊為模擬信號(hào),數(shù)字信號(hào)模擬信號(hào)隔開有助減小數(shù)字信號(hào)和模擬信號(hào)之間的相互干擾。但中間分隔區(qū)域?qū)е铝藚⒖计矫娴牟贿B續(xù),從而產(chǎn)生EMI的問題。

有經(jīng)驗(yàn)的設(shè)計(jì)人員遇到這種情況可能在模擬低和數(shù)字地之間加入縫補(bǔ)電容(Stitching Capacitance)或者磁珠,通常這些情況下都使用陶瓷電容。然而加電容會(huì)帶來一些不利的因素:

1.電容為分立器件,電容會(huì)額外的增加pad和via,pad和via都會(huì)增加寄生電感。

2.安裝陶瓷電容由于容值較小,其有效的作用空間較小。電容需要安裝到適當(dāng)?shù)奈恢谩?/p>

3.安裝電容起作用的頻率范圍一般低于200MHz。

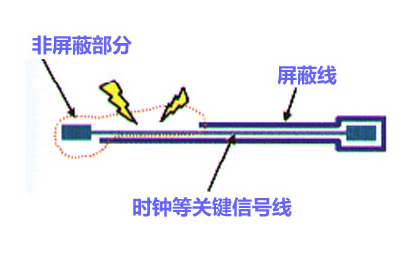

PCB設(shè)計(jì)盡量讓電源平面和地平面緊耦合,讓鄰近的兩個(gè)面之間形成耦合平面電容。我們能不能有一個(gè)辦法即讓模擬地和數(shù)字地分開又讓分開平面上噪聲更好的耦合到地平面上去呢?方法如下圖所示:

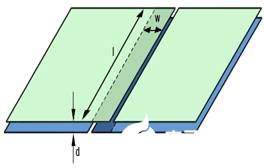

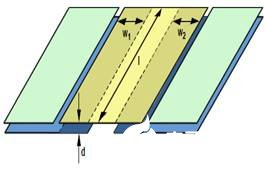

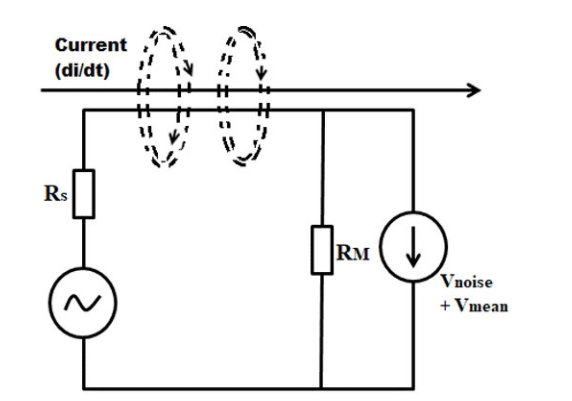

圖2 圖3

圖2圖3為兩種平面耦合方式

將上下兩個(gè)平面在分割區(qū)域形成一個(gè)重疊的區(qū)域,重疊區(qū)域會(huì)形成一個(gè)耦合平板電容,這樣既可以把模擬和數(shù)字區(qū)域分開,又可讓模擬地和數(shù)字地通過耦合平板電容鏈接到一起。

通過上述平面形成電容有以下特點(diǎn):

1.寄生電感小,另外電容均勻分散在平面重疊區(qū)域。

2.平面耦合電容起作用的頻率范圍更廣。

3.埋容平面與平面是電源平面還是地平面無關(guān)。

4.埋容結(jié)構(gòu)最好位于板子的內(nèi)層。表層或者底層會(huì)減小平板耦合電容的效果。

圖2和圖3兩種方式各有優(yōu)點(diǎn)和缺點(diǎn),圖2單位平面形成的電容較大,但如果整版都這樣分割,PCB板子的容易折斷,此方法適用于很小的區(qū)域分割;圖3的單位面積形成的電容較小,但形成的PCB比較牢固。使用于板子空間較大。

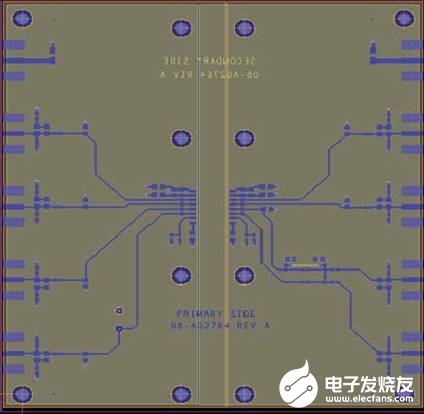

圖4 分割區(qū)域形成平面耦合電容

Remark:平面耦合電容的計(jì)算,以圖4為例:

圖4可以看做是左右兩個(gè)深黃色下的耦合電容串聯(lián)的結(jié)果。

C=(c1*c2)/(c1+c2),其中c1 c2 分別為左右兩個(gè)耦合電容,假設(shè)左右耦合電容相等則有C1=c2=(ε*s)/d,其中ε=ε_(tái)0*ε_(tái)r,ε_(tái)0為真空介電常數(shù)8.854*1e-12F/m, ε_(tái)r為相對介電常數(shù),比如FR4為4.5;S為相互重疊的面積,比如圖4中深黃色區(qū)域,d為相互重疊區(qū)域距離。

Edadoc公司有款設(shè)計(jì)用到此方案,設(shè)計(jì)中重疊區(qū)域的長4300mil,寬250mil,帶入公式中:

C=(4.5*(8.854*e-12)*4300*0.0254*(10e-3)*250*0.0254*(10e-3))/(5.12*0.0254*(10*e-3))=212pf

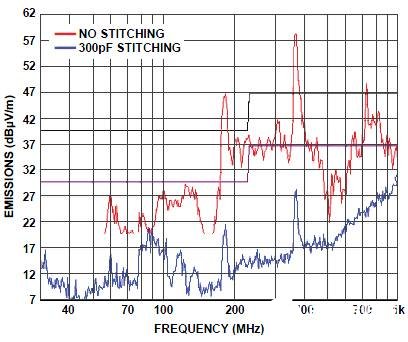

圖5 形成330pf縫補(bǔ)電容和沒有縫補(bǔ)電容實(shí)測對比圖

編輯:hfy

-

emi

+關(guān)注

關(guān)注

53文章

3582瀏覽量

127346 -

模擬信號(hào)

+關(guān)注

關(guān)注

8文章

1116瀏覽量

52394 -

數(shù)字信號(hào)

+關(guān)注

關(guān)注

2文章

951瀏覽量

47513 -

陶瓷電容

+關(guān)注

關(guān)注

3文章

428瀏覽量

23887

發(fā)布評論請先 登錄

相關(guān)推薦

淺談PCB設(shè)計(jì)七大流程

高速PCB設(shè)計(jì)的EMI抑制探討

PCB設(shè)計(jì)中EMI控制原理與實(shí)戰(zhàn)技巧

淺談PCB設(shè)計(jì)

高速PCB設(shè)計(jì)解決EMI問題的九大規(guī)則

解決高速PCB設(shè)計(jì)EMI(電磁干擾)的九大規(guī)則

PCB設(shè)計(jì)中EMI控制原理與實(shí)戰(zhàn)技巧

怎樣降低PCB的EMI

PCB設(shè)計(jì)如何降低EMI

淺談PCB設(shè)計(jì)產(chǎn)生EMI的問題

淺談PCB設(shè)計(jì)產(chǎn)生EMI的問題

評論