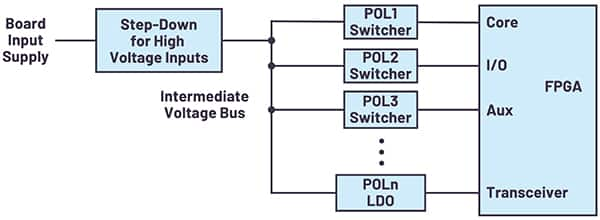

現代FPGA是有史以來最復雜的集成電路。他們采用最先進的晶體管技術和尖端的建筑結構,以實現難以置信的靈活性和最高性能。隨著時間的推移,隨著技術的進步,這種復雜性已決定了在使用FPGA的系統的設計和實現中的某些折衷辦法。在電源方面,這比在任何地方都更加明顯。對于每一代新的FPGA,電源都必須更加準確,更加敏捷,更加可控,更小,更高效并且對故障有更多的了解。

在本文中,我們專門研究了Altera Arria 10 FPGA的一些約束規范,以及它們對電源設計的意義。然后,我們討論最佳的電源解決方案,并制定計劃以成功滿足所有規格,并使用ADI公司的整套電源系統管理(PSM)IC使FPGA以最佳的效率,速度和功率水平運行包括LTC3887,LTC2977和LTM4677。

FPGA功耗要求(解釋數據表)

工程師應該將大部分時間花在編程上,而又不想花時間和精力在設計合適的電源上。確實,供電的最佳方法是使用堅固,靈活,經過驗證的設計,該設計可以滿足要求并隨著項目的發展而擴展。這使工程師騰出了重要工作來設計具有背景比特幣礦機或類似設備的每秒兆兆比特的加密并行無線光學軌道互聯網平臺。在這里,我們仔細研究一些重要的電源規格及其含義。

電壓精度

內核電源電壓是平衡FPGA功率和性能的最重要的關鍵之一。規格文件給出了可接受的電壓范圍,但總范圍并不完整。與所有事物一樣,需要進行權衡和優化。

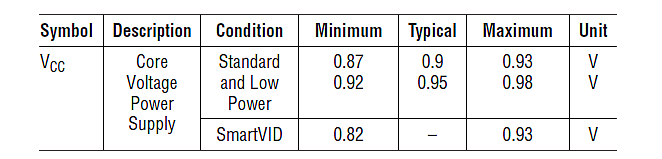

表1是流行的Altera Arria 10 FPGA1的核心電壓規范示例。盡管這些數字特定于Arria 10,但它們代表了其他FPGA內核電壓要求。該范圍相當于額定電壓的±3.3%容差。在此電壓范圍內,FPGA可以正常工作,但完整的畫面更為復雜。

表1Altera Arria 10核心電壓規格

注意標有“ SmartVID”的行,范圍為0.82V至0.93V。這代表了廣泛的電壓范圍,當FPGA通過SmartVID接口請求其自身的內核電壓時,這是可能的(稍后會有更多介紹)。SmartVID規范表明了FPGA的基本原理:它可以在不同的電壓下運行,這取決于其特定的制造公差以及所實現的特定邏輯設計。一個FPGA所需的靜態電壓可能與另一個FPGA不同。電源必須能夠響應和適應。

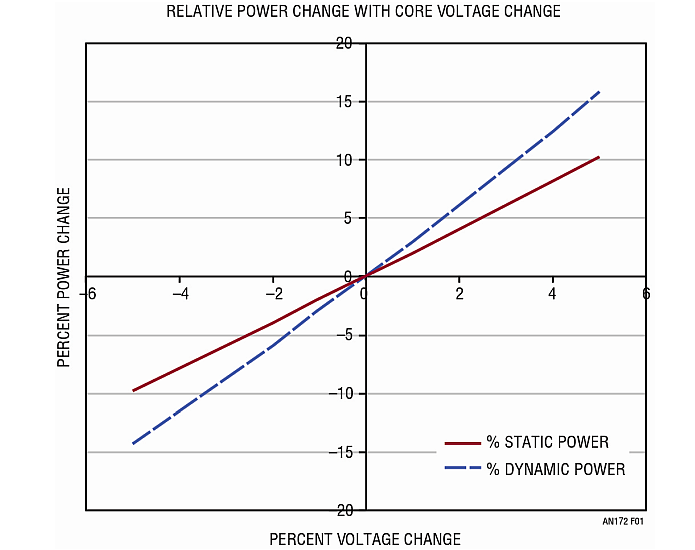

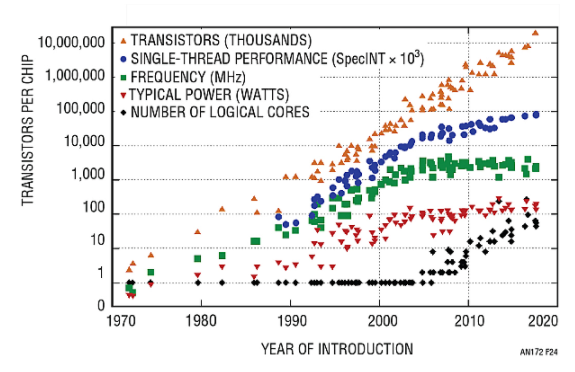

目標是產生恰到好處的性能水平,以操作已編程的功能,而不會消耗不必要的功率。從半導體物理學以及Altera,Xilinx(圖1)等發布的數據中我們知道,隨著內核VDD的增加,動態和靜態功耗都將急劇增加,因此目標是為FPGA提供足夠的電壓以達到滿足其時間要求,但僅此而已。過多的功耗并不能提高性能。實際上,這會使情況變得更糟,因為晶體管泄漏電流會隨著溫度的升高而增加,從而耗散了更多不必要的功率。由于這些原因,當務之急是針對設計和工作點優化電壓。

圖1Xilinx Virtex V電源與Core VCC

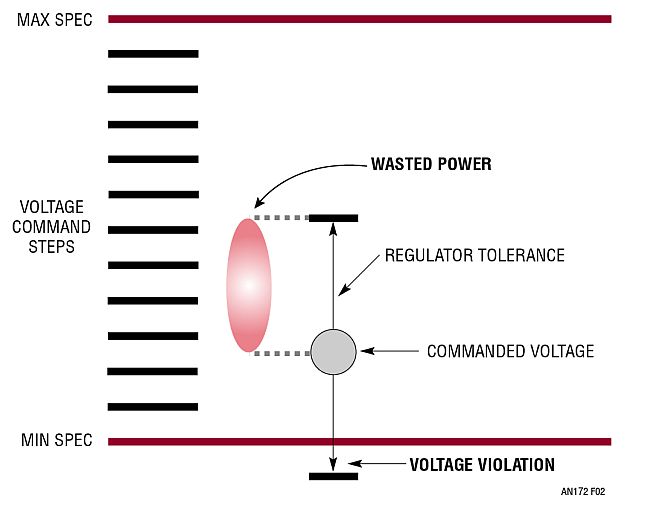

此優化過程需要非常精確的電源才能成功。調節器的不準確性必須納入誤差預算,并從可用于優化的可用電壓范圍中減去。如果內核電壓降至要求以下,則FPGA可能會因時序錯誤而發生故障。如果內核電壓漂移超過最大規格,則可能損壞FPGA,或者可能在邏輯中造成保持時間故障。所有這些情況都必須通過考慮電源容差范圍來防止,并且只能保證保證將其保持在規格范圍內的指令電壓。

問題在于大多數功率調節器不夠精確。穩壓電壓可能在指令電壓附近的公差范圍內,并且可能隨負載條件,溫度和使用期限而漂移。保證±2%容差的電源可以在4%電壓范圍內的任何地方進行調節。為了補償電壓可能過低2%的可能性,必須將命令電壓提高2%以上,以滿足時序要求。如果調節器隨后漂移到高于指令電壓的+ 2%,它將在該工作點所需的最低電壓之上運行4%。這仍然可以滿足FPGA所要求的規定電壓,但會浪費很多功率(圖2)。

圖2電源調節器容差的權衡

解決方案是選擇可以在更嚴格的電壓容限下工作的電源穩壓器。可以要求公差為±0.5%的穩壓器在所需的工作頻率下更接近最低要求,并且保證低于所需電壓的1%。FPGA將正常工作,并且將在該工作條件下消耗可能的最小功耗。

LTC388X系列電源控制器在一個可配置的寬電壓范圍內,保證了穩定的輸出電壓容差優于±0.5%。LTC297X系列電源系統管理器保證穩壓器的修整容限優于±0.25%。有了這些精度,就可以為任何FPGA優化功耗與性能之間的權衡取舍。

熱管理

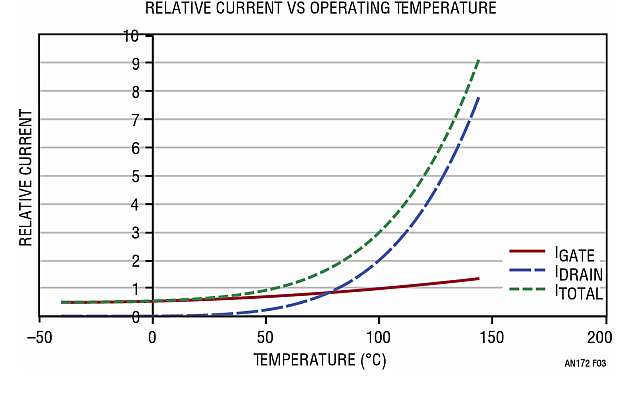

電源精度的微妙含義體現在熱預算中。由于靜態功耗幾乎可以忽略不計,因此即使不執行任何操作,FPGA也會發熱。溫度升高會導致更多的靜態功耗,從而進一步提高工作溫度(圖3)。)。向電源添加不必要的電壓只會使此問題變得更糟。如前所述,不正確的電源需要在工作電壓中設置一個保護帶,以確保有足夠的電壓來完成這項工作。由容差,系統組件可變性和工作溫度的變化引起的電源電壓不確定性會產生明顯高于最低要求的電壓。當施加到FPGA時,這種額外的電壓會導致散熱復雜,甚至在高處理負載下也會導致散熱失控。

圖3電源電流與工作溫度的關系

補救措施是提供一個非常準確的電源,該電源只能產生正確的電壓,而不僅僅是產生所需的電壓,而這正是ADI電源系統管理設備的出色表現。

SmartVID

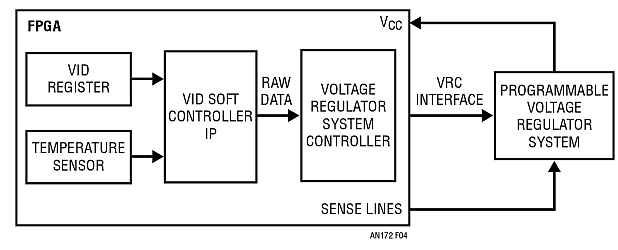

Smart VID2是Altera的名稱,它是按FPGA本身的要求在最佳電壓下運行每個FPGA的技術。FPGA內部有一個寄存器,其中包含一個特定于器件的電壓(在工廠編程),可以保證FPGA在該電壓下高效運行。FPGA內部的一個已編譯IP可以讀取該寄存器,并通過外部總線向電源發出請求以提供此精確電壓(圖4)。達到電壓后,在運行期間它將保持靜態。

圖4Altera SmartVID結構

SmartVID應用程序對電源的要求包括特定的總線協議,電壓精度和速度。總線協議是FPGA用于將其所需電壓傳送至功率調節器的幾種方法之一。在可用的方法中,PMBus是最靈活的,因為它可以處理種類繁多的電源管理IC。SmartVID IP使用兩個PMBus命令:VOUT_MODE和VOUT_COMMAND,通過它們可命令兼容PMBus的功率調節器獲得正確的電壓。

穩壓器對電壓精度和速度的要求包括:自動啟動電壓(在PMBus激活之前),每10ms接受新的電壓命令的能力,在電壓調整階段每10ms采取10mV步進的能力以及穩定時間。在10ms的步進時間內達到目標電壓的30mV(?3%)以內,最終上升到指令電壓并在FPGA操作期間保持靜態。

盡管Altera使用SmartVID這個名稱,但業界也有其他類似的技術可以實現相同的功能。最簡單的方法之一是在工廠測試每塊板,然后將精確的電壓編程到電源的非易失性存儲器中,以優化該特定板的性能。此技術不需要任何其他干預即可使電源在正確的電壓下運行。這是具有EEPROM的電源管理器或控制器的優點。

LTC388X系列電源控制器可以滿足Altera SmartVID的所有要求。此外,LTM4675/LTM4676/LTM4677μModule穩壓器可以輕松滿足要求,并以緊湊的形式提供完整的解決方案。

定時關閉

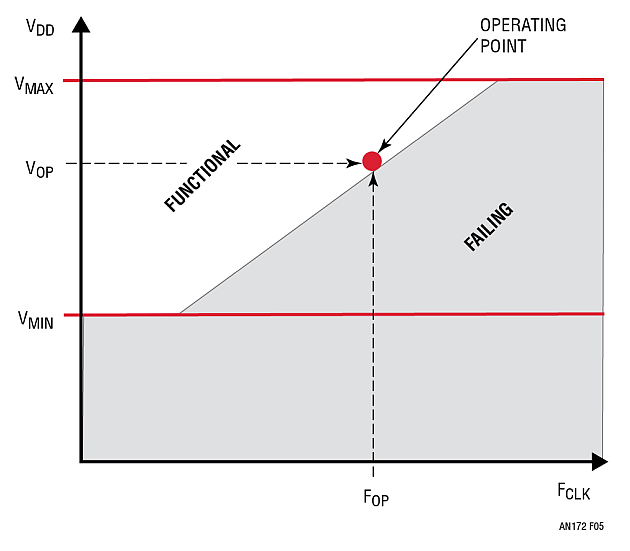

任何邏輯塊的計算速度取決于其電源電壓。在限制范圍內,較高的電壓可提供更快的性能。我們已經了解了為什么我們不能簡單地在最高電壓下工作,從而保證最佳速度。另一方面,如圖5所示,我們必須在足夠高的電壓下工作以進行應用。

圖5FPGA工作頻率與VDD的權衡

圖5的重要含義當特定設計不滿足其邏輯時序要求并落入“失敗”區域時,該怎么辦。在將設計提交給硬件之前,通常無法很好地定義功能與故障之間的界限,并且無法預先確定將通過時序的特定電壓。唯一的選擇是要么預先承諾一個遠遠高于最小值的電壓,從而浪費功率以保證功能,要么設計一種靈活的電源,以便在測試時甚至在測試時適應硬件的需求。如果是SmartVID,則在開機時。適應未知需求的能力使ADI PSM器件的精度更有價值,因為FPGA設計人員可以在實際設計中以及在開發的任何階段權衡功率以提高性能。

電源排序101

摩爾定律推動了現代FPGA中晶體管不斷縮小的趨勢,并迫使人們在使用這些微小的晶體管時進行權衡,這些微小的晶體管非常快,體積很小,但更易碎。包含數億個晶體管的芯片必須分為可獨立設計和管理的內核,模塊和分區。這些考慮的實際結果是具有許多電源域的FPGA。最近的一些FPGA具有多達12個以上的電源,需要保持這種電源狀態。除了電壓,電流,紋波和噪聲外,還包括啟動,關閉和故障情況下的順序。

當啟動和關閉電源時,最新的FPGA規范對序列順序提出了具體要求。Xilinx和Altera都建議使用特定的順序和時序,以確保FPGA正確復位,保持最小的電流消耗并在電源轉換期間將其I / O保持在正確的三態配置。給定每個FPGA的電源數量,排序任務的復雜性相當可觀。

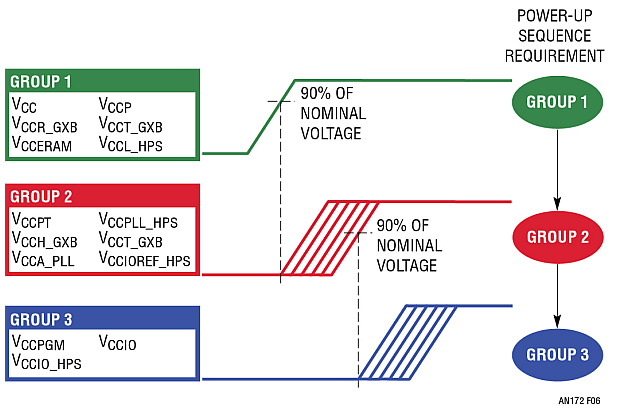

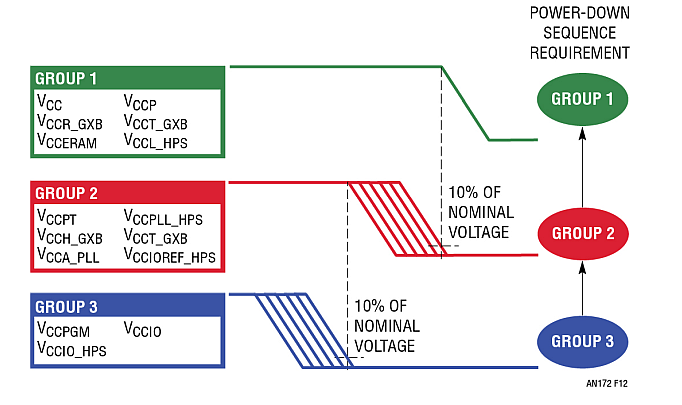

Altera Arria 10處方將電源分為三個順序組(1、2和3),并要求它們按順序1、2和3向上排序,并按相反的順序向下排序:3、2和13。

圖6Altera Arria 10升序組順序

同樣,針對Virtex UltraScale FPGA升序的Xilinx建議是:VCCINT / VCCINT_IO,VCCBRAM,VCCAUX / VCCAUX_IO和VCCO。降序是升序順序4的逆序。

這些只是眾多可用FPGA中的兩個。幾乎每個現代的FPGA系統都有多個電源軌,最明顯的問題之一是,它們應按什么順序打開和關閉?即使沒有明確的排序要求,也有充分的理由強制執行確定性的事件序列。以下是一些可用的設計選項。

無需排序-讓電源自行上升和下降。可能出什么問題了?

硬件級聯排序—每個上升的電源都必須進行硬連線以啟用下一個電源。這僅在耗材增加時起作用。

基于CPLD的排序-使用可編程邏輯來創建自定義解決方案。這是靈活的,但是整個挑戰都在設計師身上。

基于事件的排序-基于事件的排序類似于級聯排序,但是更加靈活,因為它可以上下運行。專用的定序器IC可以進行編程,并處理許多故障情況和特殊情況。

基于時間的排序-基于時間的排序會在指定的時間觸發每個事件。結合全面的故障管理,基于時間的定序器可以變得靈活,確定性和安全。

沒有排序

完全不用管理就可以打開電源系統。當主電源可用或“ ON”開關被激活時,調節器開始調節。斷電或“ ON”開關關閉時,調節器將停止調節。當然,這種方法存在很多問題。有些比其他的更明顯。

缺乏時間確定性會在系統中產生各種影響。首先是簡單地強調敏感的FPGA。這可能會立即導致災難性故障,或者可能導致過早老化,從而慢慢降低性能。都不是好事。它也可能導致不可預知的上電復位行為或上電時不確定的邏輯狀態,這使系統穩定性令人懷疑且難以調試。故障檢測和響應,能量管理和調試支持的問題在此方案中完全沒有解決。通常,避免電源時序控制會引發災難。

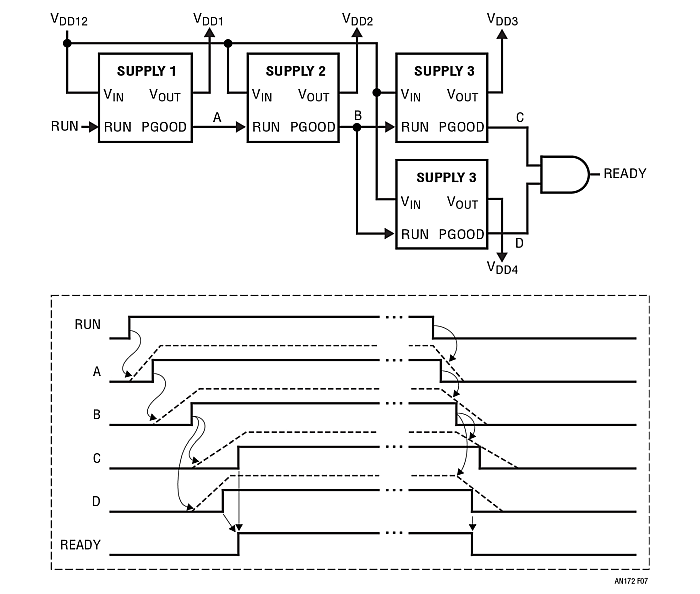

級聯測序

圖7所示為經典的PGOOD-to-RUN硬接線級聯,它是一種更有條理的排序方法。。這就像多米諾骨牌掉落:每個人都點擊序列中的下一個,這保證了進度。該技術具有簡單性的優點。不幸的是,它也有缺點。盡管它通常可以正常地用于對電源系統進行排序,但它不能反向(或以任何其他順序)進行向下排序。只能有一個序列順序。另外,該方案不能在不確定的操作條件下適當地處理故障或管理能量。做任何決定還不夠聰明。如果序列的一個階段失敗,接下來會發生什么?如果一個工作電源用盡,會發生什么?答案是不確定的,調試這些問題并不容易。

圖7PGOOD至RUN級聯測序

FPGA或CPLD排序

許多設計人員選擇在板上使用輔助CPLD或FPGA來對電源進行排序。在由數字設計師和為數字設計師設計的系統中,它具有一定的吸引力。設計數字控制模塊是很自然的事情,可以將其編程到FPGA中以控制另一個FPGA的電源。這里的決定可能具有欺騙性,因為電源系統并不像從數字控制的角度看那樣簡單。

如果設計人員希望從頭到尾解決電源排序,控制和管理問題,那么他必須首先徹底了解其復雜性。我們已經討論了許多這樣的內容,還有更多內容,例如檢測和響應微秒級時可能發生的過壓和欠壓情況,檢測危險電流和溫度,記錄遙測和狀態以及提供啟動信息。和調試服務,使硬件人員的工作更輕松。所有這些考慮因素除了數字算法外,還需要專用的模擬硬件。

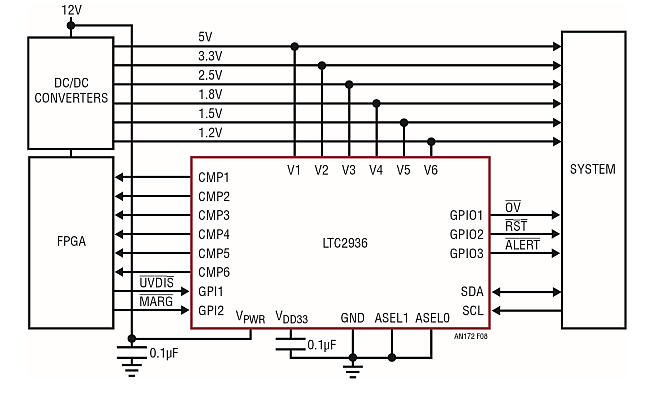

對于希望走這條路的勇敢的設計師,ADI公司提供了幾種模擬前端IC來幫助完成這項任務。在數字位和模擬電源之間的接口,LTC2936提供了六個堅固的,高精度可編程閾值模擬比較器,以檢測快速事件并將數字狀態發送至邏輯。它還具有三個可編程的GPIO引腳,用于其他功能。該可編程IC具有一個EEPROM,用于在啟動時提供幾乎即時的功能,并能夠存儲故障遙測信息以通過其I2C / SMBus接口進行調試。圖8顯示了使用LTC2936的便捷方法。

圖8LTC2936可編程電壓監控器

除了快速比較器功能外,還必須有一個模數轉換器(ADC)來收集遙測數據。LTC2418是一個經過驗證的選擇,它可以通過其快速建立的24位delta-sigma ADC和4線SPI接口監視多達16個通道的模擬信號。板控制器可以輕松地傳輸測量結果并監視系統中的許多興趣點。

通常,使用FPGA或CPLD控制電源排序有很多選擇。這種方法可行,但必須有人擁有數字和模擬設計,包括所有不可避免的設計錯誤,出現難以想象的極端情況和故障的機會以及令人不快的支持問題。當然,有更簡單的方法來構建電源系統。

簡單的音序器/監督器

解決強大的排序和錯誤處理難題是簡單的排序器/管理程序的領域。這些功能對電源軌進行排序,并確保它們在運行(監控)期間保持在其指定的限制內,這一重要工作很重要。的LTC2928是一種易于使用的引腳帶配置序器配置的序列的定時(下是向上的反向),和可配置的監督員電壓閾值。它具有滿足要求的潛力,但沒有多余的裝飾,并且不提供數字可編程性或遙測功能。

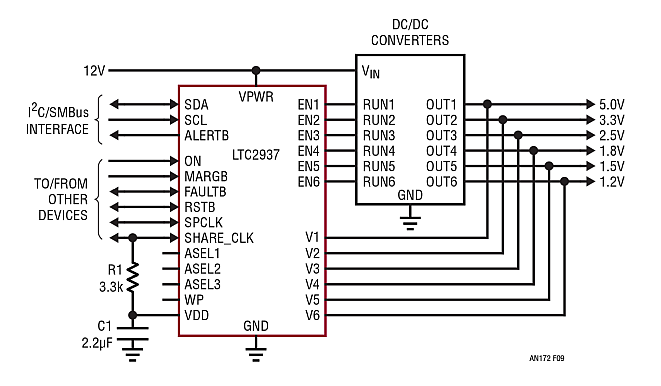

圖9LTC2937電源管理器和排序器

LTC2937是具有EEROM的可編程定序器和監控器的類別。它具有完整的數字可編程性,基于時間和基于事件的排序功能,并且可以對任何數量的電源進行排序和監督,處理故障并將故障狀態記錄到EEPROM黑盒中。對于不需要電壓管理和遙測的情況,這是一個有價值的解決方案。

電力系統管理

為了充分利用完整的電源系統管理(PSM)的所有優勢,請使用ADI公司的PSM IC之一。這些功能可以自動對任意數量的電源軌進行升序和降序排序,將電壓精確控制在0.5%以上(在某些情況下為0.25%),可以測量和報告電壓,電流,溫度和狀態遙測,從而協同處理復雜的信號。故障場景,并將詳細的故障信息記錄到EEPROM。

排序是通過定時握手系統完成的,所有IC均同意“零時間”和時基,所有序列事件均發生在預編程的時間(基于時間的排序)。這允許任意數量的導軌自動進行升序和降序。

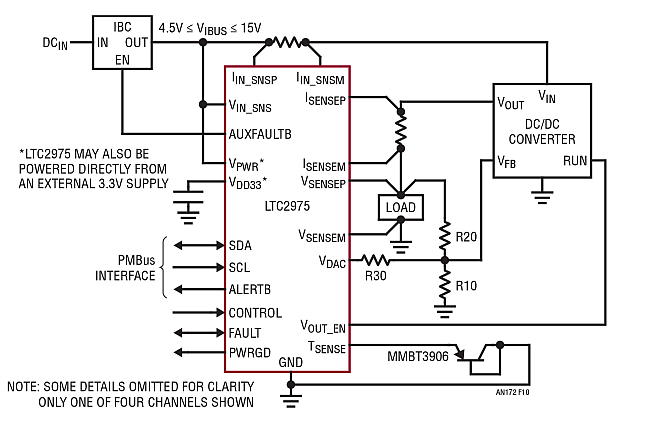

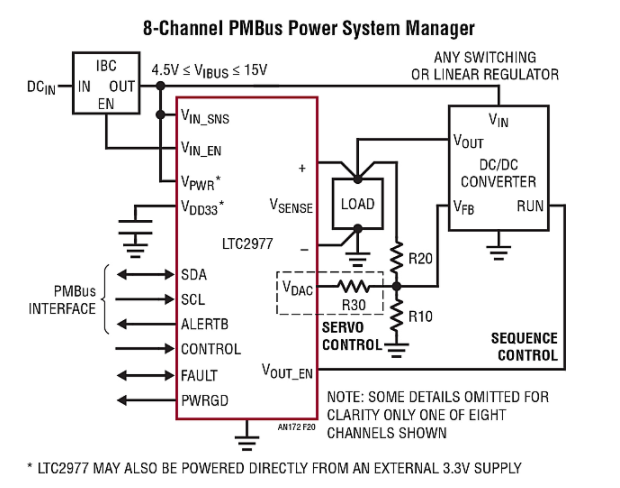

PSM IC系列包括“控制器”,這些控制器具有自己的開關驅動器和模擬環路控制,以在各個方面處理開關電源。或者,電源“管理器”包含環繞外部電源的伺服環路,從而將電源管理的所有功能(包括定序,監控和監視)添加到從開關電源穩壓器到LDO的任何電源軌上。電源管理器的一個示例是LTC2975,如圖10所示。

圖10LTC2975 4通道電源系統管理器

μModules

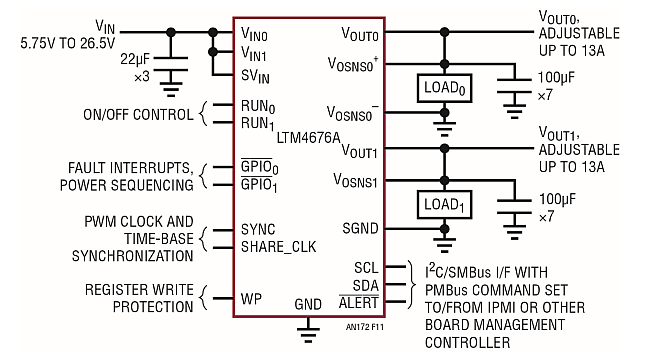

PSM μModules是最緊密集成的解決方案,在BGA或LGA占地面積中每平方厘米提供最多的功能。這些是完整的電源系統,位于一個封裝中,包括控制器IC,電感器,開關和電容器。某些μModule穩壓器(例如LTM4650)不包含數字功能,因此它們可以受益于LTC2975的額外排序和管理。某些μModule,例如LTM4676A,具有其自己的PSM功能,并且可以輕松地與系統中的其他PSM IC集成。

圖11LTM4676A PSM μmodule雙路13A穩壓器

共享測序

PSM微模塊,管理器IC和控制器IC都通過稱為SHARE_CLK的簡單單線總線共享時序信息,從而在升序和降序方面共同協作。所有PSM IC都通過這條單線共享有關何時應該開始排序(時間為零),何時發生時鐘的每個“滴答”以及有關影響排序的其他狀態信息的信息。只需將系統中的所有SHARE_CLK引腳連接在一起就足以實現這種協調。每個IC都有自己的時序控制程序,可以使用共享的時基來準確,可靠地計時事件,例如在發生故障時啟用和禁用,斜坡上升和超時。

在最基本的水平上,SHARE_CLK引腳是一個漏極開路的100kHz時鐘引腳。漏極開路特性意味著IC可以主動下拉或放開并允許總線浮動。當總線上的所有設備松開時,上拉電阻會將電壓拉至3.3V。這樣一臺設備就可以通過拉低直到準備就緒來停止時鐘,這意味著所有設備都必須在時鐘啟動前達成一致:一種有效的機制,用于傳達零時間,并通過停止時鐘來指示排序狀態。

共享故障處理

FAULT總線與SHARE_CLK引腳相似。系統中的每個電源系統管理IC都連接到共享的FAULT導線,可以使用其漏極開路輸出將其拉低,或者在另一個設備拉低時作出響應。這為整個PSM設備系列提供了一種簡單,快速的方法來進行通信并響應故障。該行為是完全可配置的,并且在排序過程中或在穩定狀態下出現問題時,可以進行協調響應。該系統可以配置為在記錄有關系統狀態和發生故障的原因的黑匣子信息時,根據指定的時序來斷開電源并嘗試重新排序。該EEPROM黑盒信息可用于以后通過I2C總線進行處理。

降序排序和管理存儲的能量

降低電源供應順序時,還有一個額外的考慮因素:能源管理。越來越重要的是,在電源時序下降時,為電源提供確定的時序非常重要,這需要仔細考慮系統中存儲的能量在哪里消散。高功率電源可能具有數十個大型電解電容器作為大容量電荷存儲元件,并且這些電容器將被充電至電源電壓,從而擁有足夠的能量,以在不幸的條件下炸毀保護不當的設備。為了避免這種情況,FPGA制造商指定了保護器件的降序。對于Altera Arria 10,此序列如圖12所示。5

圖12Altera Arria 10降序分組順序

在此降序中隱含的要求是,電容器中所有存儲的能量都必須流到某個地方并安全地消散。有幾種方法可以做到這一點。最簡單的是在電容器兩端固定一個電阻。該電阻在電源接通時總是耗散功率,但是可以將其電阻做得足夠大,以使相對損耗最小,并且RC放電時間常數可以接受地短。使電源充分放電所需的時間是RC時間常數的倍數(通常為5倍),應進行優化以使電阻器中散發的靜態功率可以接受(例如,小于1/4 W)。對于1mF的電容和1.0V的電源,R =4Ω的電阻值將具有t = 4ms的時間常數,并且將在大約13ms的時間內將電源放電至50mV以下。

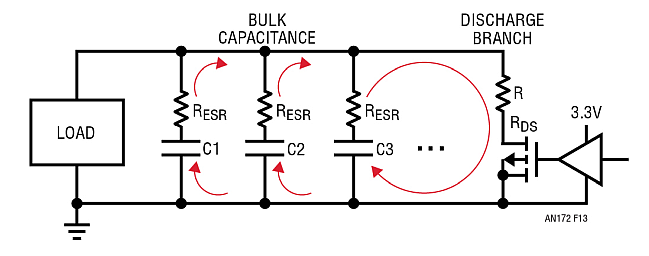

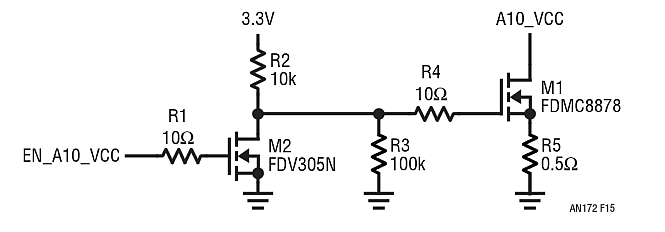

一個更復雜但非常安全的選擇是僅在需要對電源放電時才在電容器上切換電阻。這種方法可以在需要時將電荷從大容量電容器中抽出,并安全地將其散逸到開關FET的電阻和輔助串聯電阻中,但是避免了固定電阻器持續消耗功率的情況。該電路如圖13所示。

圖13用FET釋放電源電容

這種方法有幾個考慮因素:控制,放電時間和功耗。必須有一個可用的信號來命令放電開關在??適當的時間閉合。開關FET是NMOS,因此控制信號必須上升到FET的VTH以上,足以驅動它達到飽和。對于普通的FET,此柵極驅動電壓可能高達3V至5V。

典型的電解電容器將具有數百毫歐的等效串聯電阻(ESR),當電容器放電時會消耗一些能量,但是這些電容器有很多并聯,因此總并聯電容可能總計為10毫法拉,等效電阻將為幾十毫歐或更小。一個安全的假設是,電容器的ESR將耗散一小部分存儲的能量。

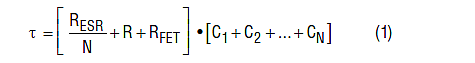

為了在合理的時間內對電容放電,放電RC時間常數必須小于所需放電時間的1/5(以使電壓降至幾毫伏以下)。這是一個簡單的計算(公式1),使用所有電容器的總和以及FET和串聯R的總和以及RESR電阻的并聯組合,其中N是并聯電容器的數量。

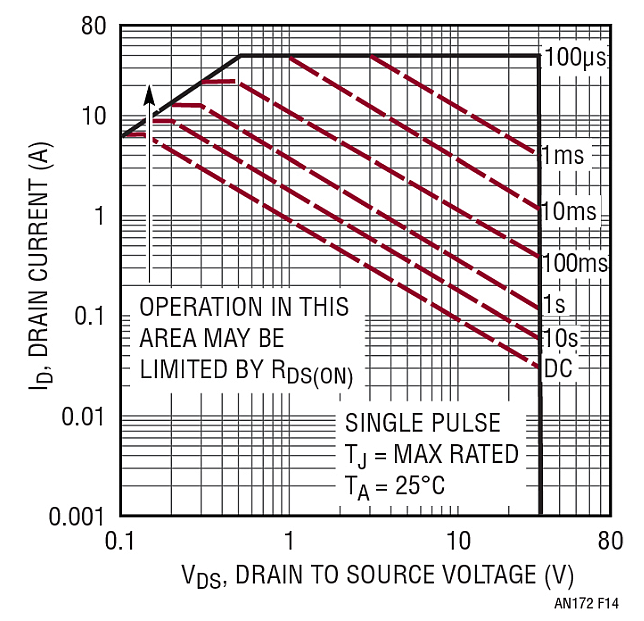

對于具有50mF電容器組且RDS + R =500mΩ之和的大型系統,電壓將在約125ms內降至50mV以下。在此期間的峰值電流(和功率)為1V /500mΩ= 2A或2W。由于大部分存儲的能量都是在前兩個時間常數中燃燒的,因此我們可以通過查看FET的安全工作區域圖(例如圖14中的示例)來確定是否需要串聯電阻。6在這種情況下,我們的FET將安全地承受超過10s的2W脈沖,因此沒有損壞它的危險。但是,該FET的RDS小于20mΩ,因此串聯R必須為480mΩ。我們必須確定串聯電阻的大小,以處理熱量,因為它會耗散大部分功率。通常,脈沖持續時間將比電阻的熱時間常數短得多。電阻數據手冊提供了更多信息。

圖14NMOS FET安全工作區

最強大的放電電路可以在各種條件下安全地耗散能量。圖15中的電路顯示了一種經過實踐檢驗的方法。它使用安森美半導體FDMC8878放電FET和一個物理尺寸較大的SMD 1210尺寸的0.5Ω電阻器。

圖15放電FET電路

通過電源系統管理應對挑戰

如我們所見,ADI公司的PSM是管理FPGA電源系統中所有需求的最佳解決方案。好處包括:

一流的電壓精度(優于±0.5%)。

具有EEPROM存儲器的完全自治的功能。

集成的完全可編程電源時序控制,整個系統的獨立上下定時。

集成的,健壯的,系統范圍的故障管理。

全面的遙測:電壓,電流,溫度和狀態。

協調的IC系列可滿足電源系統的所有領域。

適用于所有產品階段的功能強大的PC軟件(LTpowerPlay):原型設計,設計,編程,啟動,測試,調試等。

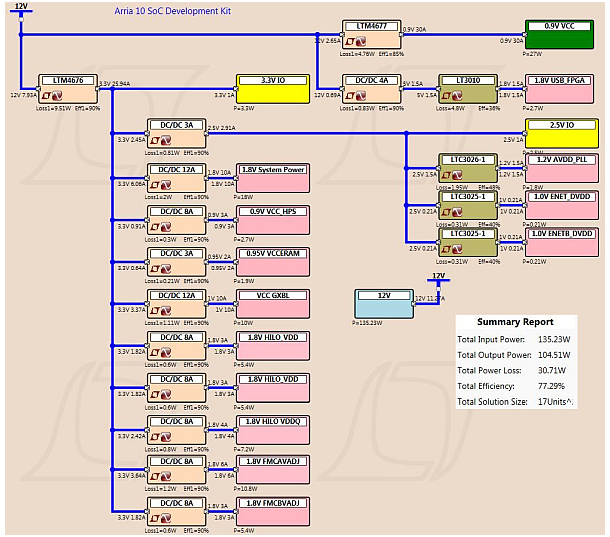

Altera Arria 10 SoC開發套件展示了適用于Altera Arria 10 SoC IC的Analog Devices電源系統管理解決方案(圖16)。

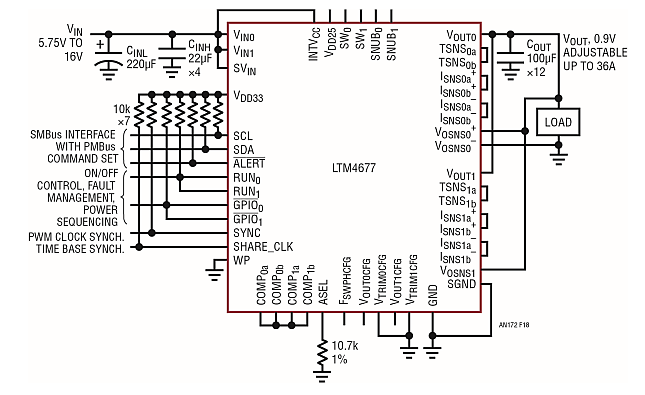

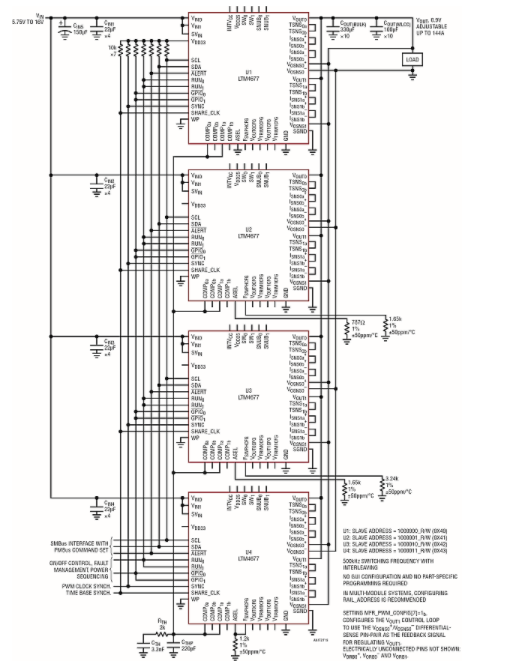

在該設計中(圖17),核心電源工作在0.95V和30A的電壓下。在這些相對寬松的電源要求下,單個LTM4677模塊輕松提供了必要的電流(高達36A),如圖18所示。對于需要更多電流的要求更高的應用,最多可以并行運行四個LTM4677模塊以提供高達144A的電流,如圖19所示。

圖16Altera Arria 10 SoC開發套件

圖17Arria 10 SoC開發套件的電源分配

圖18提供高達36A電流的單個LTM4677

該解決方案提供了最佳的電路板空間利用率,因為集成的μModule幾乎不需要外部組件,而PMBus接口使它們無需硬件修改即可配置。微型模塊提供了最低的復雜度解決方案,因為其中包括許多復雜的模擬考慮因素,例如電源開關,電感器,電流和電壓感測元件,環路穩定性和散熱。

由于LTM4677模塊包括PSM,因此它保證了核心電源將始終在直流電壓目標的±0.5%范圍內工作。它還允許通過PMBus接口進行電壓調整,既可以通過FPGA內部的SmartVID IP進行調整,也可以通過LTpowerPlay圖形用戶界面進行調整,以提供用戶對電源的完全控制權。

為了管理不包含其自身PSM功能的電源穩壓器,我們僅包括LTC2977,它是8通道PMBus兼容的電源系統管理器。每個通道“環繞”電源以將電壓伺服到編程目標的0.25%以內(圖20)。它與LTM4677 μModule無縫協作以實現排序和故障響應,從而使整個電源系統具有連貫性且易于編程。

圖19四顆LTM4677在0.9V電壓下提供高達144A的電流

圖20LTC2977管理任何電源電壓

系統電源排序由LTM4677內核電源,LTM4676A + 3.3V電源和管理板上所有其他電源穩壓器的LTC2977的合作伙伴關系提供。這些IC具有通用的PMBus時序命令(存儲在EEPROM中),可輕松以任何順序和時序配置啟動和關閉時序。這些保證了為“ group1”,“ group2”和“ group3”電源指定的事件的適當的自主順序(圖6)。

除了電壓精度和排序控制之外,該板上的LTM4677,LTM4676A和LTC2977還提供了完整的故障處理。如果一個或多個電源軌出現過壓,欠壓,掉電,過流或完全故障,則可以將系統配置為快速自動響應,關閉電源以保護敏感的FPGA,然后重新啟動。 -如果可能的話,開始。

系統中的大多數電源軌要求適度的電流(小于13A)和適度的電壓容限。這些可以由非PSM設備(例如LTM4620)提供,并由LTC2977進行排序和管理。這在電路板面積,復雜性和成本之間提供了非常有效的平衡。

還有一些電源軌,例如PLL和收發器電源,它們要求的噪聲比開關穩壓器所能提供的噪聲要低,而這些電源軌則需要一個線性穩壓器。的LTC3025-1和LTC3026-1提供這些功能良好,除去由它們的輸出的開關和負載引起的噪聲。LTC2977也可以管理這些信號,以排序,調整和處理故障情況。

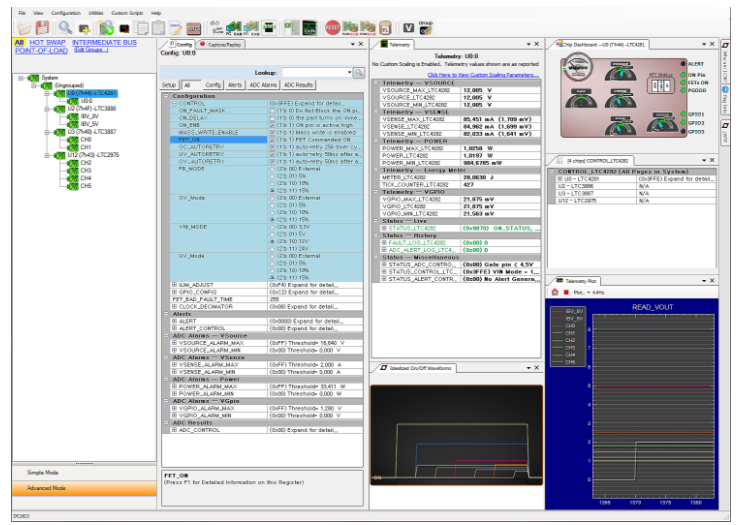

LTpowerPlay

全面的LTpowerPlay圖形用戶界面支持整個PSM設備系列(圖21)。由于PSM的許多功能都是通過IC的EEPROM中豐富的配置寄存器集訪問的,因此一種工具可以將總線上的PSM IC的整個集合整合到一個易于使用的視圖中。LTpowerPlay工具提供了豐富的功能集,可加快設計和開發的各個階段。它可以離線運行,以在對IC進行編程之前顯示它們的視圖,或者可以通過I2C總線與包含一個由許多PSM設備控制的一個到數百個電源軌的完整系統進行實時通信。

LTpowerPlay通過提供有關寄存器和功能的詳細信息來簡化和簡化復雜的配置。它以圖形方式表示系統中可用的所有配置,狀態和遙測信息,從而在系統運行時使其清晰易懂。它簡化了完整寄存器集的編程和維護,提供了一種在Microsoft Windows PC上創建和保存配置的簡單方法。當電源發生故障時,LTpowerPlay可以輕松查看系統中發生故障的位置以及狀態,遙測和黑匣子信息指示發生的情況。它還為常見的故障情況提供了詳細的調試幫助。如果有人需要幫助,LTpowerPlay也可以要求幫助,

圖21LTpowerPlay圖形用戶界面

ADI公司為Altera,Xilinx和NXP FPGA提供了一套全面的演示平臺。這些功能齊全的電路板是電源系統管理如何為FPGA系統提供最清潔,最靈活和最強大的電源解決方案的有效示例。此外,您當地的ADI公司應用工程師可以為選擇和使用完整的電源系統管理IC產品組合提供詳細的幫助。閱讀更多信息,下載參考資料,并在此處訂購FPGA板。

FPGA之旅

既然我們了解了如何最好地為FPGA系統供電,那么我們可以拋開異想天開,看看為什么事情會這樣。為了理解為什么今天的情況如此,我們需要簡短的歷史課。

摩爾定律

1965年,戈登·摩爾(Gordon Moore)在《電子雜志》(Electronics Magazine)8中發表了他的著名文章。他指出,他觀察到單個芯片上的晶體管數量每年都在增加一倍,并且他預測至少在1975年之前,這種情況應該會持續增加。修改了他的模型,但是芯片上晶體管數量的持續指數增長的基本原理已成為電子行業的一個公理。這是一個奇怪的自我實現的預言,在其他任何行業中都沒有,而且在歷史上也沒有過。實際上,它已經成為全球工程師的主要動力,他們創造了創新,并在戈登·摩爾(Gordon Moore)首次發表他的簡單觀察結果時進行了難以想象的折衷。

由于這場與自己的技術競賽,決策過程一直偏向于以成本,功耗,可用性甚至耐用性為代價將更多設備擠入更小的區域的技術。在技??術競賽中,尺寸決定一切。這種軌跡的一些含義是,先進的芯片使用更多的功率,變得更泄漏,更脆弱,更敏感,并且更難于管理和保護。

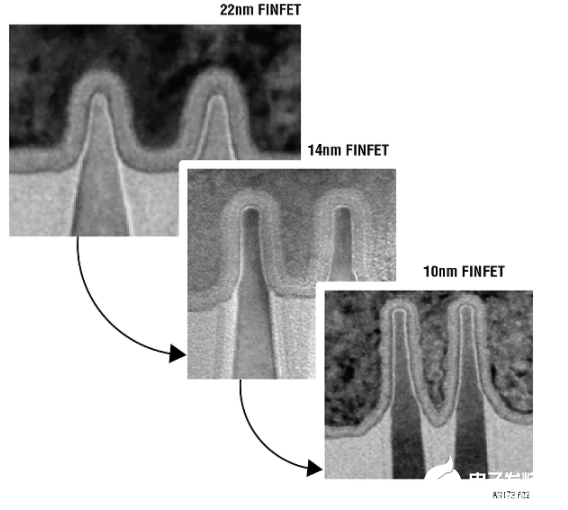

晶體管工程

隨著晶體管縮小到納米尺寸的特征,重要的副作用變得越來越占主導地位。最明顯的是電壓裕量。幾十年前,5伏特曾是晶體管的理想電源,但這種電壓會擊穿較新的FET晶體管中的所有結和氧化物。隨著晶體管特性的縮小,內部電場會變得更強,并且可忍受的工作電壓也會縮小以防止損壞。最新的晶體管一代只能承受約1.0V的最大電源電壓。此外,絕對電壓容限也成比例地縮小:1.0V的2%比5V的2%的范圍小得多,因此精度成為越來越迫切的問題。

隨著電壓的降低,晶體管電流驅動(IDSAT)也隨之增加。提高的驅動強度至少可以實現兩個目的。首先,它允許具有較小柵極電壓的晶體管驅動很大的電流-使其強度足以切換到有用的頻率。其次,它允許使用體積更小的晶體管。較小的晶體管可以更快。不幸的是,晶體管驅動強度的提高有其自身的缺點:泄漏電流。

芯片上的晶體管會消耗兩種功率。動態功率是在一定頻率下在邏輯1和邏輯0之間切換的常見成本,而動態功率是通過對與晶體管本身以及連接器件的芯片上的導線相關的微小寄生電容器進行充電和放電而引起的。動態功率與邏輯轉換的頻率以及電源電壓的平方成正比。

晶體管泄漏所消耗的功率不太明顯。無論電路是處于活動狀態還是空閑狀態,無論是否計時,該電源都會在電路通電時泄漏掉。晶體管驅動強度的增加導致更多的泄漏電流,因為要傳導更多電流的結和結構更難關斷。較強的晶體管比較弱的晶體管更容易泄漏。隨著每一代晶體管的產生,泄漏的影響越來越大。只有英雄級的晶體管工程(化學,冶金,平版印刷和物理)和準確,靈活的電源管理相結合,才能控制泄漏功率。

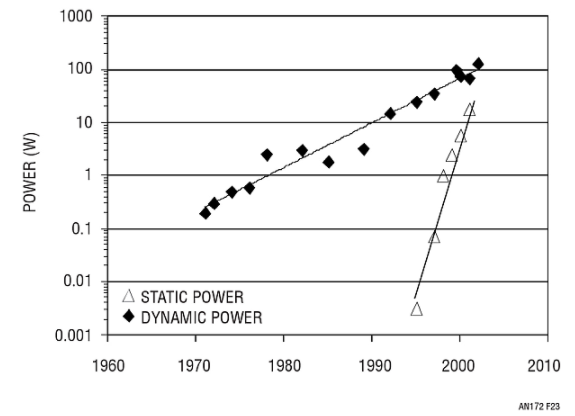

十年前,戈登·摩爾(Gordon Moore)觀察了這些事實,并指出了兩個要點。首先,如果動態功率繼續以相同的速度上升,則工作芯片上的結溫將接近太陽表面的結溫。其次,如果不采取其他措施,泄漏功率將超過動態功率,成為主要的能耗模式,從而進一步加劇了功耗問題(圖23)。為了解決這些影響,IC業界當時采用了幾種新技術。其中之一是時鐘管理-減慢或停止時鐘以降低動態功耗-另一個是在單個芯片上使用多個處理內核以利用不斷增長的晶體管數量。

圖23靜態和動態功率增長

來源:“摩爾,戈登。沒有指數是永遠的:但是“永遠”可以延遲!”2003年國際固態電路會議。

即使使用所有這些高級架構,漏電問題仍然很麻煩。晶體管工程是一種向下彎曲曲線的有效方法,但這還不夠。由于每一代較小的晶體管都需要降低電源電壓,因此動態功率的問題仍然得到解決,但是隨之而來的晶體管強度和漏電流的增加,以及芯片上器件數量的不斷增長,對電壓管理提出了要求。必須嚴格控制電源電壓,并積極調節電源電壓,以滿足每個特定設備的需求。

先進的架構

直到世紀之交的體系結構發展主要集中在優化單個計算核心上,以盡可能快地執行盡可能多的計算。這涉及將時鐘速率提高到電路故障速度以下的“免費”技術:其最大工作頻率。它還涉及架構優化,但是這些優化主要是為了在每個時鐘周期內提高性能。

在令人驚訝地意識到功率很重要之后,工程師開始將資源從原始速度重定向到更微妙的優化中。這種新趨勢首先出現在計算體系結構中,這是時鐘速率不斷提高的平穩期,并且每一代中每個晶體管的性能提高速率都趨于平穩(圖24)。這是馴服動態功率野獸的最明顯方法:停止如此快地將電荷從VDD傾斜到VSS。

圖24計算硬件指標的增長趨勢

來源:M。Horowitz,F。Labonte,O。Shacham,K。Oluktun,l收集并繪制的截至2010年的原始數據。哈蒙德和巴頓。K. Rupp收集了2010-2017年的新地塊和數據。

但是,單個芯片上的晶體管數量繼續以戈登·摩爾(Gordon Moore)預測的(要求?)的必然速度攀升。所有這些晶體管都必須做一些事情。這就需要進行第二項重大創新:多核體系結構。大約在時鐘速度停止增長的同時,單個芯片上的內核數量開始增長。多核的優勢包括可通過重復使用來簡化芯片設計,使用熟悉的構建模塊進行更簡單的軟件設計,以及能夠單獨調節每個核以滿足計算負載需求的能力。多核革命始于固定計算平臺,但有人會說,這一事件是FPGA誕生的那一刻。當世界意識到最大化內核數量是最好的時候。從某種意義上說

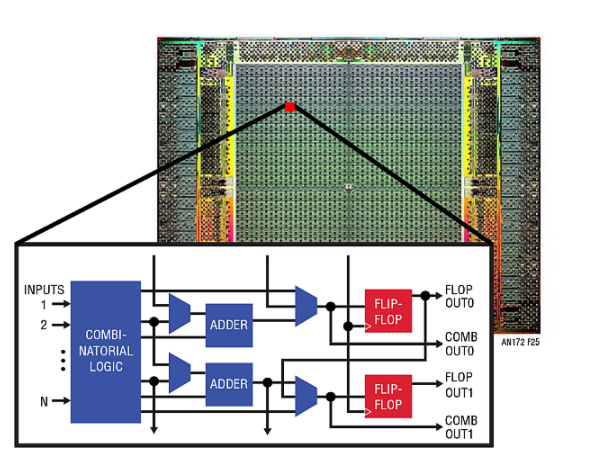

FPGA的剖析

圖25FPGA可配置結構

來源:SemiWiki.com

FPGA在最基本的層次上是通過可配置的互連網格捆綁在一起的原始可配置邏輯單元的集合。它們與編譯器一起形成了高度靈活的計算結構,可以轉換為幾乎任何可以想象的通用數字功能,包括組合和順序邏輯塊。在頂層,該結構被其他功能所圍繞,以支持和增強功能。某些模塊(例如偏置電路,RAM和PLL)支持芯片內部的功能。各種可配置的GPIO單元,高速通信硬宏(LVDS,DDR,HDMI,SMBus等)以及高速收發器允許芯片內部的邏輯以各種電壓,速度和協議與外界通信。其他模塊,例如集成的CPU和DSP內核,

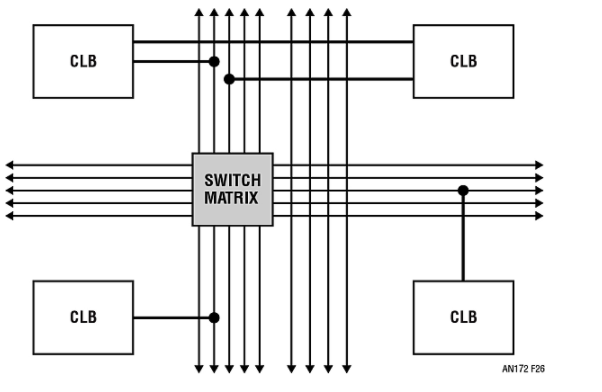

FPGA核心結構由數千個或數百萬個稱為“可配置邏輯塊”(CLB)的基本單元組成。每個CLB是組合邏輯和順序邏輯元素的集合,這些元素可以共同產生基本計算,并將值保存在一個或多個觸發器中。組合邏輯通常采用可編程查找表(LUT)的形式,從而可以將幾個輸入位轉換為幾個任意輸出位。每個LUT都按照編程執行一個基本邏輯功能,并將結果傳遞到可配置的互連中以進行后續處理(圖26)。)。特定的CLB和LUT設計是使一個FPGA系列與另一個FPGA系列不同的秘訣之一。廉價的FPGA使用更簡單的CLB,具有更少的輸入,輸出和互連以及更少的觸發器。最高端的FPGA使用更加復雜的CLB,每個CLB都能夠提供更多的輸入,更多的邏輯組合和更高的速度。此優化允許每個CLB進行更多計算,并在編譯設計中實現更優化的性能。自然,與較簡單,互連程度較低的器件相比,在更復雜的FPGA中增加的輸入和輸出具有不同的動態功耗折衷。

圖26CLB之間的可配置開關矩陣

可配置邏輯功能的基本概念在核心結構本身之外延續到I / O單元,這些I / O單元也可高度配置以滿足廣泛的電壓,驅動強度和邏輯樣式(推挽,三態,開路) -排水等)。像可配置的LUT和互連矩陣一樣,可編程I / O在啟動時會從配置存儲器中接收其配置,這對電源順序有影響。

還有一些功能塊不能或不應該使用通用CLB和GPIO來實現。這些就是所謂的“硬宏”。它們是從優化中受益的功能,或者不能簡單地制造得足夠快或足夠小而需要專用電路。其中包括千兆位收發器,算術邏輯和DSP元件,專用控制器,存儲器和專用處理器內核。與可以像軟件一樣編譯并加載到可配置結構中的“軟”塊相比,這些是“硬宏”。硬宏通常具有自己的電源,特定電壓和時序要求。

所有這些各種功能塊均具有電源系統必須滿足的各種電源需求。核心結構通常需要芯片上的最低電壓和最高功率。在現代FPGA中,該結構在充分利用時,可能需要以0.85V工作的電源提供超過100A的電流。在CPU內核中可以找到相似的電壓,但電壓不同,電流順序也不同。其他片上模擬功能可能由1.8V或3.3V供電,必須先通電。同時,GPIO組可能以3.3V或1.8V工作,并且必須在核心結構的上電復位完成之前才通電。這些電源序列要求中的每一個都必須由系統強制執行。

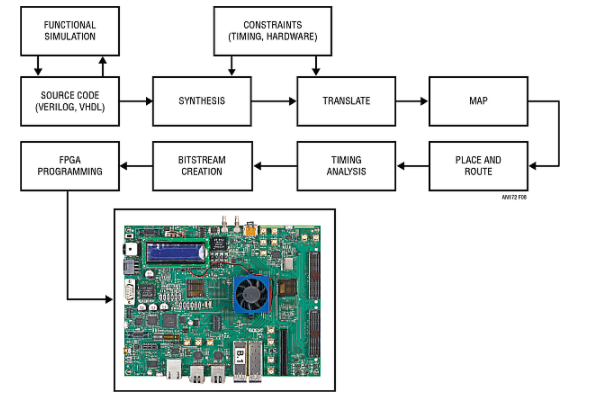

FPGA體系結構的最后一部分是工具鏈(圖27)。為了將可配置邏輯結構的空白板塊轉換為高性能電路,存在一套全面的工具,可將一組Verilog或VHDL代碼轉換為邏輯塊,分配時鐘,復位和可測試性資源,優化功能以實現以下目的:速度,功耗或尺寸限制,然后將結果加載到FPGA的配置EEPROM中。沒有這些工具,FPGA將永遠無法發揮其全部潛力。實際上,這些工具和編程語言是如此重要,以至于它們常常使使FPGA起作用的基本電路設計蒙上陰影。

工程師將大部分時間都花在編程上,而又不想花費時間和精力來考慮提供合適的電源。但是,這些工具隱含的電源要求經常被忽略。由于數字化設計投入了大量精力,因此只有在編譯后的設計融為一體時,才能知道電源需求,并且可以發現電源問題。在數字設計和軟件工具中,就像在硬件設計中一樣,靈活的電源架構對于成功至關重要。

歷史,經濟和人為因素繼續推動創建FPGA的晶體管和架構的發展趨勢。在FPGA的成功中,電源在每個級別和每個設計階段都扮演著至關重要的,看不見的角色。電源的最佳選擇是準確,堅固,靈活,緊湊且易于使用的電源。在所有這些品質中,ADI公司的PSM產品系列為行業樹立了標準。

圖27FPGA設計流程(最后使用硬件)

附錄A:護理和喂養?

可能會有一些讀者對本應用筆記的標題提出疑問,尤其是那些不熟悉英語的讀者。最初,似乎完全不適合提及FPGA的維護和供電。但是,針對此異議的答案非常簡單:英語是一種有趣的語言。盡管沒有人就“護理和喂養”一詞在歷史上的確切時刻達成一致,但眾所周知,該術語起源于更簡單的時代的農業根源,并已被廣泛使用(濫用)以指代幾乎所有可能會變得脆弱或氣質的東西。在這種情況下,我們已經碰到頭了。盡管人們是否必須“饋送” FPGA是有爭議的,但肯定有人必須“照料”它!

雖然“護理和喂養”一詞在現代互聯網時代已廣泛應用于嬰兒,兒童,丈夫,老板,外籍人士,科學數據甚至數字脈沖整形濾波器等事物,但它是最早的,也許也是最奇怪的一種,可以在此經典文本中找到參考文獻,這不僅對其標題感興趣,而且對于它可以在Internet上立即獲得的事實也很有趣。

參考

[1]英特爾。“英特爾Arria 10設備數據表”。6

[2]英特爾。“AN 711:英特爾Arria 10器件的節能功能。”

[3]英特爾。“Intel Arria 10核心結構和通用I / O手冊”,圖10-15和10-16。

[4] Xilinx。“Virtex UltraScale FPGA數據表:直流和交流開關特性。”

[5]英特爾。“AN 692:Arria 10和Stratix 10器件的電源排序注意事項。”

[6] Diodes IncorporatedDMN1032UCB4數據表,圖12。

[7]馮·奧赫,約阿希姆。“應用筆記:SMD電阻上的脈沖負載:處于極限。”

[8]摩爾,戈登。《電子雜志》第1卷,“將更多的組件裝填到集成電路上”。》,第38卷,第8期,1965年4月19日。

[9]摩爾,戈登。“沒有指數是永遠的:但是'永遠'可以被延遲!”2003年國際固態電路會議。

[10] Fullers,S。和Millett,L。Ed。第55頁,“計算性能的未來:是超越游戲還是更高層次?”華盛頓特區國家科學院

Nathan Enger是Analog Devices的混合信號應用工程師。

編輯:hfy

-

FPGA

+關注

關注

1626文章

21665瀏覽量

601828 -

電源設計

+關注

關注

30文章

1530瀏覽量

66297

發布評論請先 登錄

相關推薦

UPS電源維護與保養技巧

適用于 Microsemi? RTG4? FPGA 的 TI 航天級電源解決方案應用手冊

使用航天級電源元件為Microsemi RTG4 FPGA供電

使用航天級電源元件為Microchip RTAX-S/SL FPGA供電

使用航天級電源元件為Microchip RT PolarFire FPGA供電

使用航天級電源元件為AMD Kintex XQRKU060 FPGA供電

ROHM開始提供LogiCoA電源解決方案

FPGA助力簡化電源設計

電池供電系統的單片電源解決方案TPS650732-Q1數據表

用于為FPGA和DSP供電的三電源電源管理ICTPS75003數據表

如何為 FPGA 開發緊湊而高效的電源解決方案

FPGA電源保養和供電的電源解決方案

FPGA電源保養和供電的電源解決方案

評論