在半導體領域,單個模塊中的器件工作頻率和晶體管數量隨時間增加。在本文中,我們將介紹可以在ASIC的物理設計實現中使用的廣為人知的低功耗實現技術。CMOS器件有三大功率損耗:動態功率,靜態功率和短路功率。

CMOS器件的總功耗如下:

CMOS器件具有非常低的靜態功耗,當所有輸入均處于某個有效邏輯電平且該器件未進行開關操作時,就會發生這種情況。

靜態功耗是電源電壓,晶體管閾值電壓和晶體管尺寸的函數。當以更高的頻率工作時,動態功耗會極大地影響總體功耗,并由下式得出:

在哪里,

C負載= CMOS的負載電容

VDD =電源電壓

F =發生過渡的工作頻率

a =開關活動常數

從等式(2),我們可以得出結論,動態功耗與器件的工作頻率和電源電壓成正比。

現在,第一個組件是設計的頻率,但是由于數字設備的速度越來越快,我們無法降低工作頻率。因此,我們需要使用時鐘網絡以節省功耗。為了節省時鐘樹的功率,設計人員使用了時鐘門控技術,其中在時鐘門控單元上施加了特殊的使能信號,以打開指定觸發器組的時鐘,這有助于降低動態功耗。

節省功率的第二個要素是芯片的電源電壓。有多種技術可借助電源電壓來節省功率。

- 多VDD

- 跨域的杠桿移位器插入

- DVFS(動態電壓頻率縮放)

- 多Vt

- 電源門控(電源關閉)

讓我們詳細討論用電源電壓節省功率的實現技術。

1)多VDD

多VDD技術用于節省設計的動態和靜態功耗。在此,芯片以不同的電源電壓實現。不同的功能塊以不同的電源電壓運行。我們可以通過減少設計的標準單元和存儲元件的電源電壓來節省功耗。

在多VDD技術中,根據設計的關鍵程度定義了不同的電源域。這里,電平轉換器用于從低壓電源域到高壓電源域的信號,反之亦然。在網表級別,將以UPF和CPF電源格式編寫設計代碼,在此基礎上,我們可以開發設計的電源結構。

2)跨域的電平轉換器插入

在多VDD設計中,使用了電平轉換器。電平轉換器是一種數字組件,用于將信號從一個轉換為另一電壓電平(從低電壓電平轉換為高電壓電平,反之亦然)。

對于在設計中的不同電源域之間插入電平轉換器,有一些特殊的放置準則。電平轉換器應放置在設計的目標域中。插入電平轉換器的一個缺點是-它占用了設計空間。但是,與此同時,插入電平轉換器將有助于節省芯片的功耗。

有兩種類型的電平轉換器。

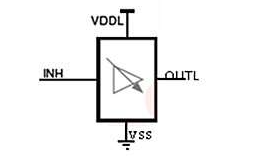

高至低電壓電平轉換器

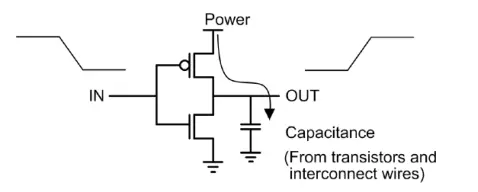

它僅引入緩沖延遲,因此對時序的影響最小。下圖顯示了從高到低的電平轉換器。

圖1從高到低的電平轉換器

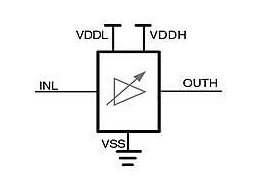

低至高電壓電平轉換器

低壓擺幅輸入信號不一定足夠強,無法完全導通輸入晶體管。這可能導致不可接受的長時間上升或下降時間。這可能會導致更高的開關電流并降低噪聲容限。下圖顯示了從低到高的電平轉換器。

圖2從低到高的電平轉換器。

在放置階段,從低到高電壓電平轉換器需要特別注意。

3)DVFS(動態電壓和頻率縮放)

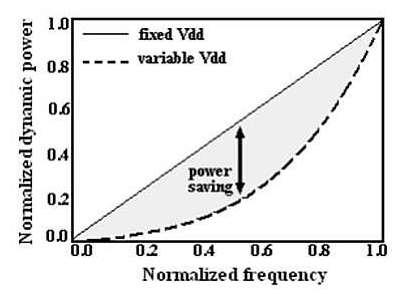

在DVFS技術中,工作電壓以及頻率會根據設計的不同工作模式動態變化。通過隨頻率改變電壓,我們可以降低功耗。當需要高工作速度時,增加電源電壓以獲得更高的工作頻率,而功耗增加。

動態電壓和頻率縮放是廣泛用于各種計算系統,微處理器等的功耗和能耗降低技術。降低電源電壓可以降低功耗,因為電源和電源電壓之間存在二次關系。由于此技術同時優化了電壓和頻率,因此對于靜態和動態功耗非常有效。下圖顯示了通過使用可變電源電壓實現的節能效果。

圖3通過使用可變電源電壓可實現節電

4)多Vt

該技術涉及使用多閾值電壓標準單元庫來實現設計,以節省設計功耗。庫以彼此獨立的標準Vt,低Vt和高Vt形式提供。這些庫用于功率和時序優化。

物理設計流程中的布線完成后,可以通過在非時序關鍵路徑中進行Vt交換來實現功率恢復,方法是在簽約階段的黃金時段將低Vt單元轉換為高閾值電壓單元。

近來,多Vt合成流在較低技術節點中變得更加普遍。在ASIC設計流程中,主要的標準Vt庫用于初始合成。多個閾值單元用于優化和合成的下一個迭代。

5)電源門控(電源關閉)

通過施加特定信號在特定時間間隔內關閉模塊/模塊,可以降低CMOS電路的內部泄漏功率。可以通過使用可插入網表的電源門控技術來節省功耗。

在這種技術中,當功能未激活時,這些塊被置于關閉模式,并在需要時打開。通過在單元(功率門控器)上施加一些特殊信號(上拉或下拉),可以控制系統邏輯功能的啟用和禁用。這些特殊單元(門控)的添加會占用更多的區域。

這些選通器也稱為睡眠晶體管,它們用作開關,以切斷部分設計的電源并將永久電源連接到電路電源。PMOS睡眠晶體管用作VDD電源的“頁眉開關”,而NMOS睡眠晶體管控制VSS電源,稱為“頁腳開關”。

可以采用兩種不同的方式來實現電源關閉(PSO):片上電源關閉和片外電源關閉。電源開關位于片上PSO的SoC中;電源開關在片外PSO中位于芯片外部。

PSO同樣可以是精細或粗略的門控,指的是受單個電源開關約束的每個模塊的大小。通過精細的電源門控程序,我們可以通過關閉單個模塊來節省電源,而無需切斷繼續工作的不同模塊的電源。這將有助于降低CMOS的泄漏功率。利用粗粒度技術,單個睡眠信號可以使整個區域斷電。這有助于減少待機模式下的泄漏功率。

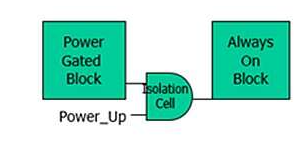

我們需要一個隔離單元來隔離來自功率門控模塊的信號,如下圖4所示。

圖4電源門控塊信號需要一個隔離單元

該隔離單元始終是“加電”單元,它可以防止任何未知的邏輯電平到達“始終在線”邏輯。

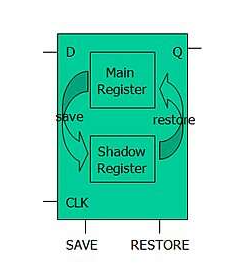

在進行電源門控時,在關閉電源門控模塊之前,還需要一個保留寄存器以保存其內容。如下圖5所示,保留寄存器除主寄存器外還包含一個影子寄存器。影子寄存器由“常開”電源供電,當“ SAVE”置為高電平時,該電源存儲被電源門控的模塊的邏輯值。當“ RESTORE”置為高電平時,它將將此邏輯值恢復到主寄存器。

圖5保留寄存器包含一個影子寄存器和主寄存器

在本文中,已經討論了各種低功耗實現技術。采用特定技術取決于設計復雜度和要降低的功耗。在采用它們之前,還需要考慮上述每種技術的時序損失,面積損失和實現復雜性。

通常,多VDD和DVFS技術用于降低動態和靜態功耗,而多Vt和電源門控技術主要用于降低泄漏功率。

參考

- 許,《面向編譯器的動態電壓和頻率調節,以降低CPU功耗和能耗》,博士學位,美國新澤西州立大學,2003年

- Diary R. Suleiman,Muhammed A. Ibrahim,Ibrahim I. Hamarash,動態電壓頻率縮放(DVFS),用于降低微處理器的功耗和能耗

- 低功耗方法論手冊學習

Vipulkumar Patel是eInfochips的高級物理設計工程師,在VLSI / ASIC領域擁有7年的經驗。

Rakesh Gosai是eInfochips的高級物理設計工程師,在不同納米技術節點(7 nm,16nm)的ASIC領域擁有4年的經驗。

-

CMOS

+關注

關注

58文章

5689瀏覽量

235170 -

asic

+關注

關注

34文章

1195瀏覽量

120346 -

電平轉換器

+關注

關注

1文章

174瀏覽量

19549 -

電源電壓

+關注

關注

2文章

987瀏覽量

23946 -

UPF

+關注

關注

0文章

49瀏覽量

13493

發布評論請先 登錄

相關推薦

低功耗模組短信通:短消息發送實例解析

物聯網系統中TCP低功耗產品長連接狀態下降低功耗功能的實現方案

國產化低功耗窄帶物聯網無線通訊方案_ZETA技術

一款4644芯片低功耗設計思路解析

CPU的低功耗與高功耗的區別

國產藍牙模組 | 低功耗藍牙應用

在ASIC的物理設計的低功耗實現技術解析

在ASIC的物理設計的低功耗實現技術解析

評論